2/24/2008 9T6WP

Preliminary Hardware Data Module BCM7405

06/29/07 Timing and AC Characteristics

Broadcom Corporation

Document 7405-1HDM00-R MPOD Input Timing Page 1-151

MPOD INPUT TIMING

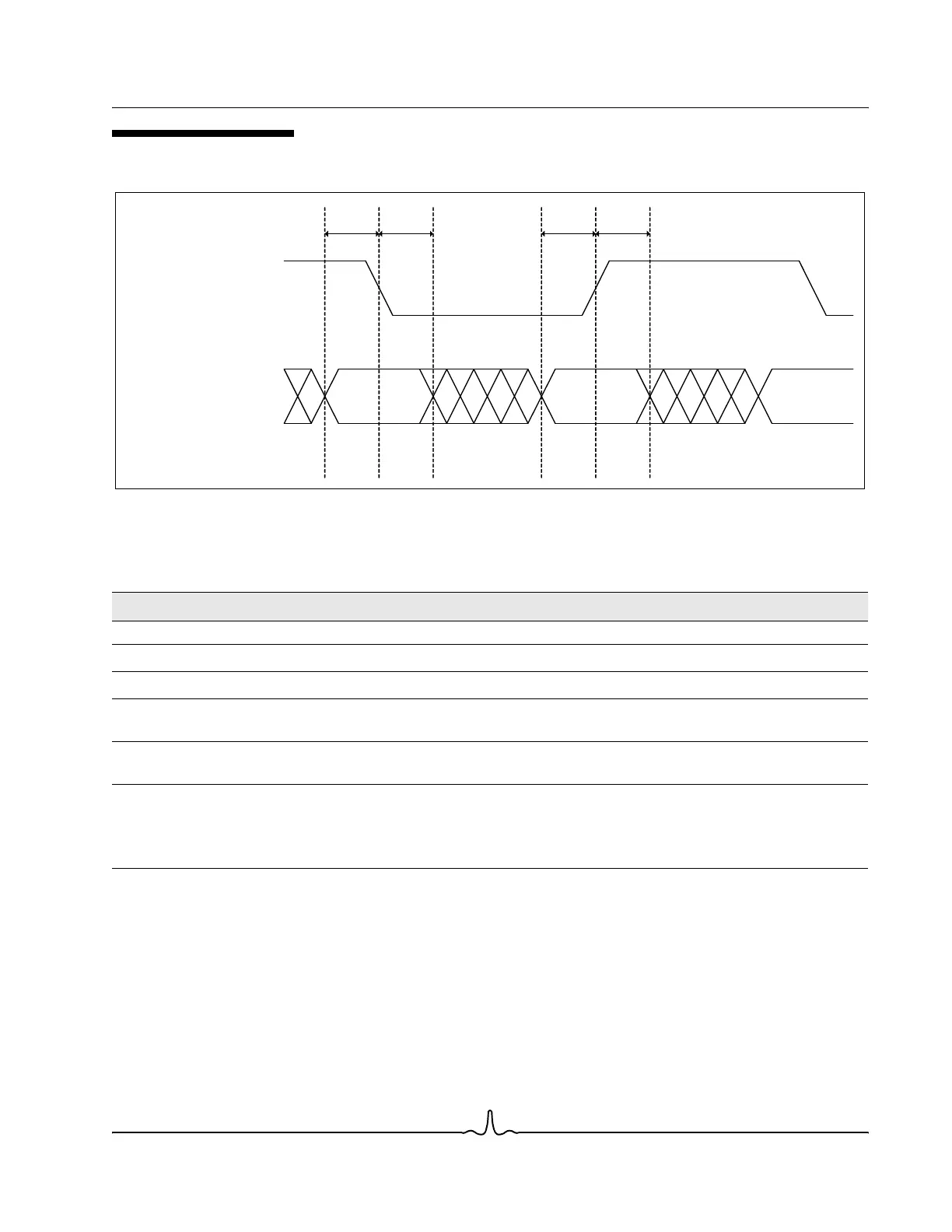

Figure 1-36: MPOD Input Timing

Table 1-22: MPOD Input Timing Parameters

Description Symbol Min. Max. Units

i_MPOD_CLK frequency Fs – 54 MHz

i_MPOD_CLK rise time

1

Trise–2ns

i_MPOD_CLK fall time

1

Tfall–2ns

i_MPOD_DATA, i_MPOD_SYNC Setup Time to i_MPOD_CLK active edge

(rising or falling)

2

Tsu3–ns

i_MPOD_DATA, i_MPOD_SYNC Hold Time from i_MPOD_CLK active

edge (rising or falling)

2

Thd3–ns

1

Rise and Fall time specs are measured from the 10% and 90% VDD levels.

2

The active clock edge for i_MPOD_CLK is programmable to either the rising or falling edge.

3

Tsu and Thd are measured from 10% and 90% VDD levels for falling and rising transitions of i_MPOD_DATA and

i_MPOD_SYNC.

i_MPOD_CLK

i_MPOD_SYNC,

i_MPOD_DATA[1:0]

T

s

u

T

h

d

T

s

u

T

h

d

Loading...

Loading...