2/24/2008 9T6WP

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

Broadcom Corporation

Document 7405-1HDM00-R MIPS4380 Processor Core Page 1-67

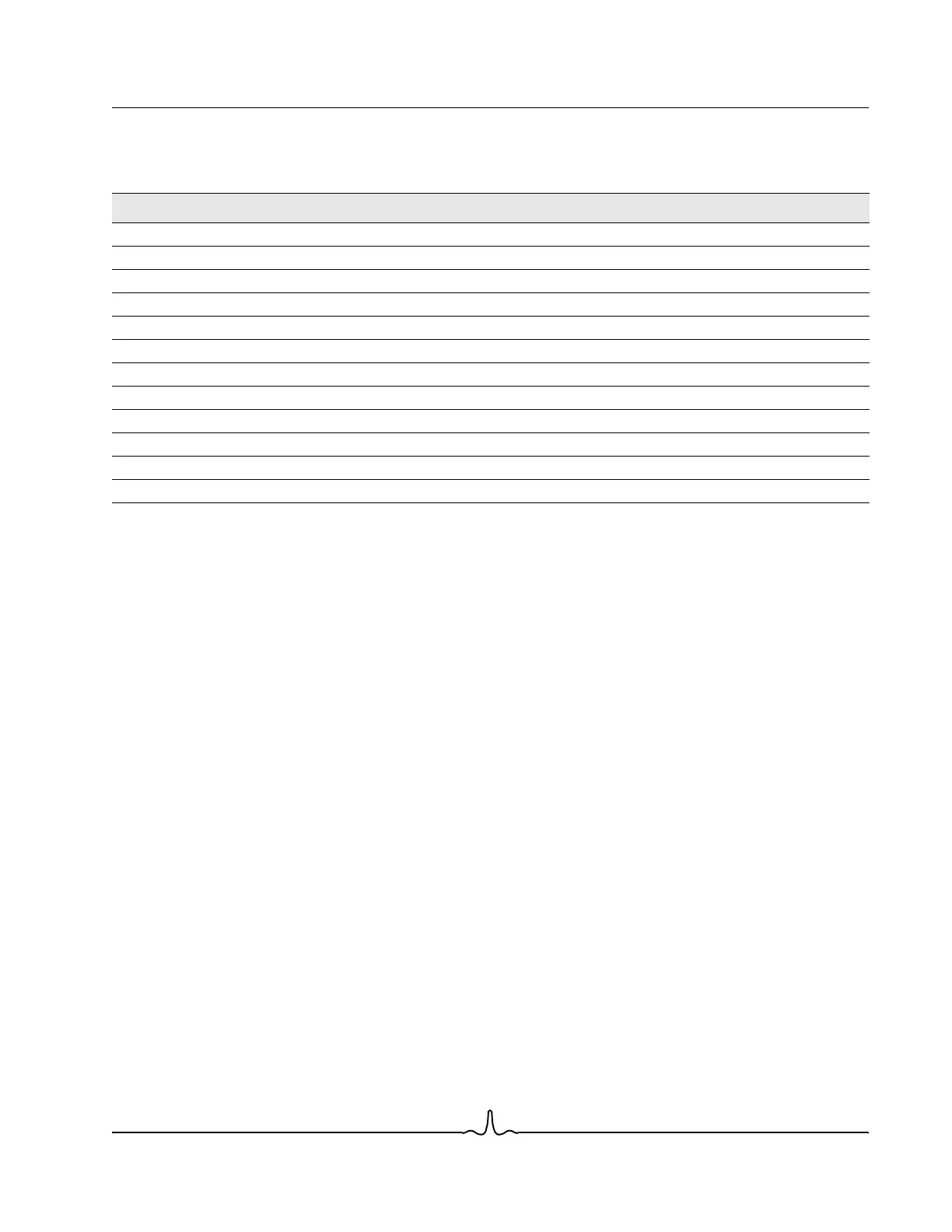

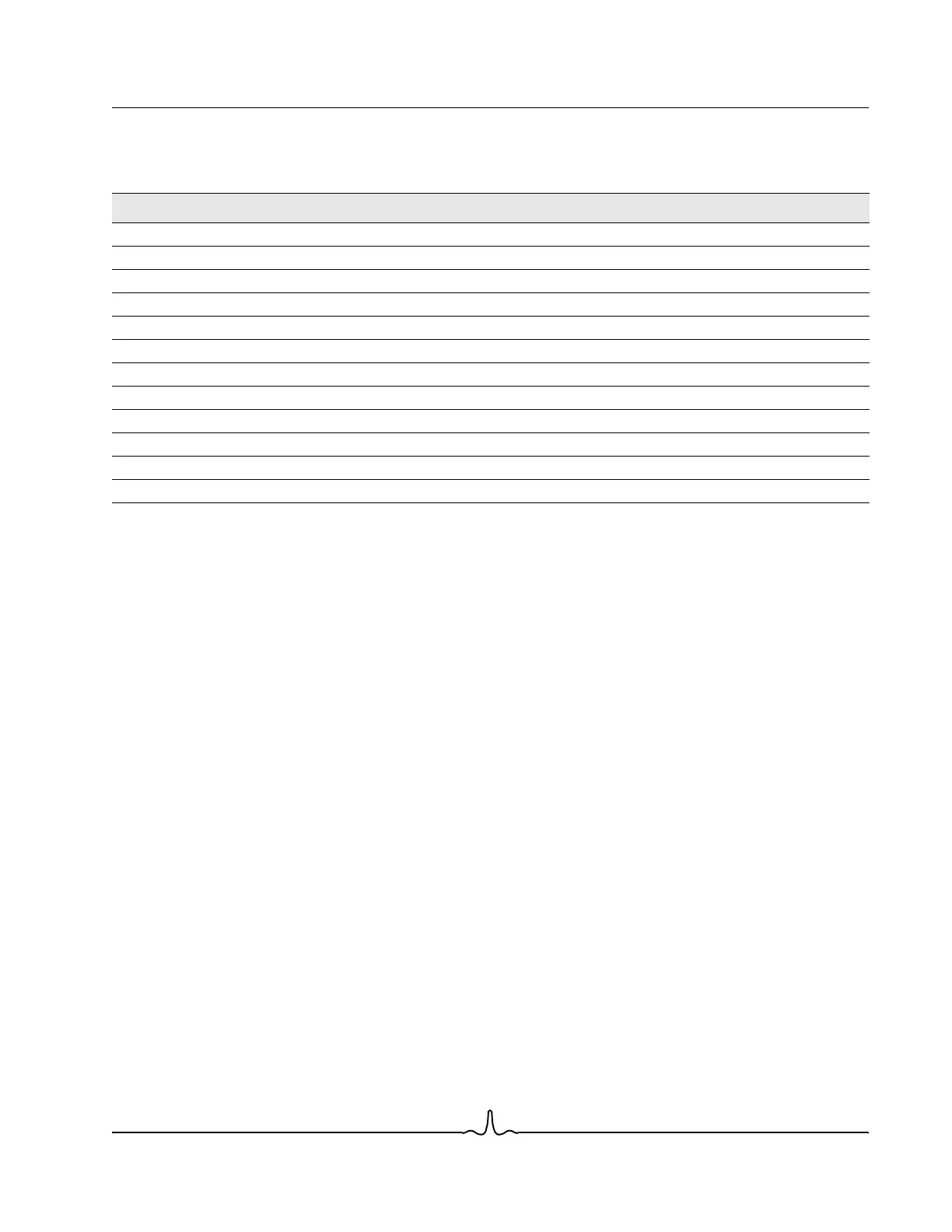

Table 1-16 shows the latency and repeat rate of each basic floating point instruction.

EDSP EXTENDED INSTRUCTIONS

The eDSP extended instructions are Broadcom-specific instructions and are implemented as part of the MDU. The extended

instructions are defined in the MIPS32 SPECIAL2 space for an application to perform 16-bit DSP computation such as

multiply-add, multiply-subtract, saturate, shift-left, and their combinations. In particular, the eDSP instructions in the CPU

can execute SIMD (dual-MAC) instructions and perform direct load and store operations from Hi/Lo accumulators.

Each TP in a CMT CPU can execute eDSP instructions and has its own Hi/Lo accumulators, but like the MDU, the TPs share

the execution unit.

MIPS16E APPLICATION-SPECIFIC EXTENSION

The MIPS16e is a MIPS-standard application-specific extension contains a set of 16-bit instructions and a few new 32-bit

instructions. The ASE allows a user program to be compiled into a 16-bit program for saving the code space. Furthermore,

MIPS16e provides instructions to perform multiple loads and stores at subroutine calls and returns. A 16-bit program is

invoked as a subroutine and can be executed with other 32-bit programs in one application.

Each TP can execute a MIPS16e program at the same time in a CMT CPU.

MEMORY MANAGEMENT UNIT WITH TLB

The Memory Management Unit (MMU) is responsible for virtual-to-physical address translation, memory protection among

active applications, and cache attributes for the memory locations. MIPS32 architecture partitions an address space into five

memory segments; there are segments which use fixed mapping and there are segments which use page-based mapping.

For page-based mapping, the CPU provides a translation lookaside buffer (TLB) to hold those recently translated pages.

The TLB contains 32 entries, each entry holds the translation information of a virtual page with its even half mapped to a

physical page and odd half mapped to another. The page sizes of the physical pages can range from 4 KB to 256 MB.

Table 1-16: FPU Latency and Repeat Rate

Basic FPU Operation Latency (S/D) Repeat rate (S/D)

add, abs, neg, sub, mul 4/4 1/1

*madd, msub, nmadd, nmsub 8/8 1/1

div 24/32 6/8

sqrt 28/40 7/10

*recip 12/20 3/5

*rsqrt 16/28 4/7

c.cond to movf and movt or movt, movn, bc1 instruction 4/4 1/1

ceil, floor, round, trunc 4/4 1/1

mov, movf, movn, movt, movz 4 1

mtc1, dmtc1, mfc1, dmfc1 4 1

cvt.d.s, cvt.[s,d].[w,l], cvt.[w,l].[s,d], cvt.s.d 4 1

* 64-bit FPU instructions

Loading...

Loading...