2/24/2008 9T6WP

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

Broadcom Corporation

Document 7405-1HDM00-R MIPS4380 Processor Core Page 1-65

MAJOR FUNCTIONAL BLOCKS

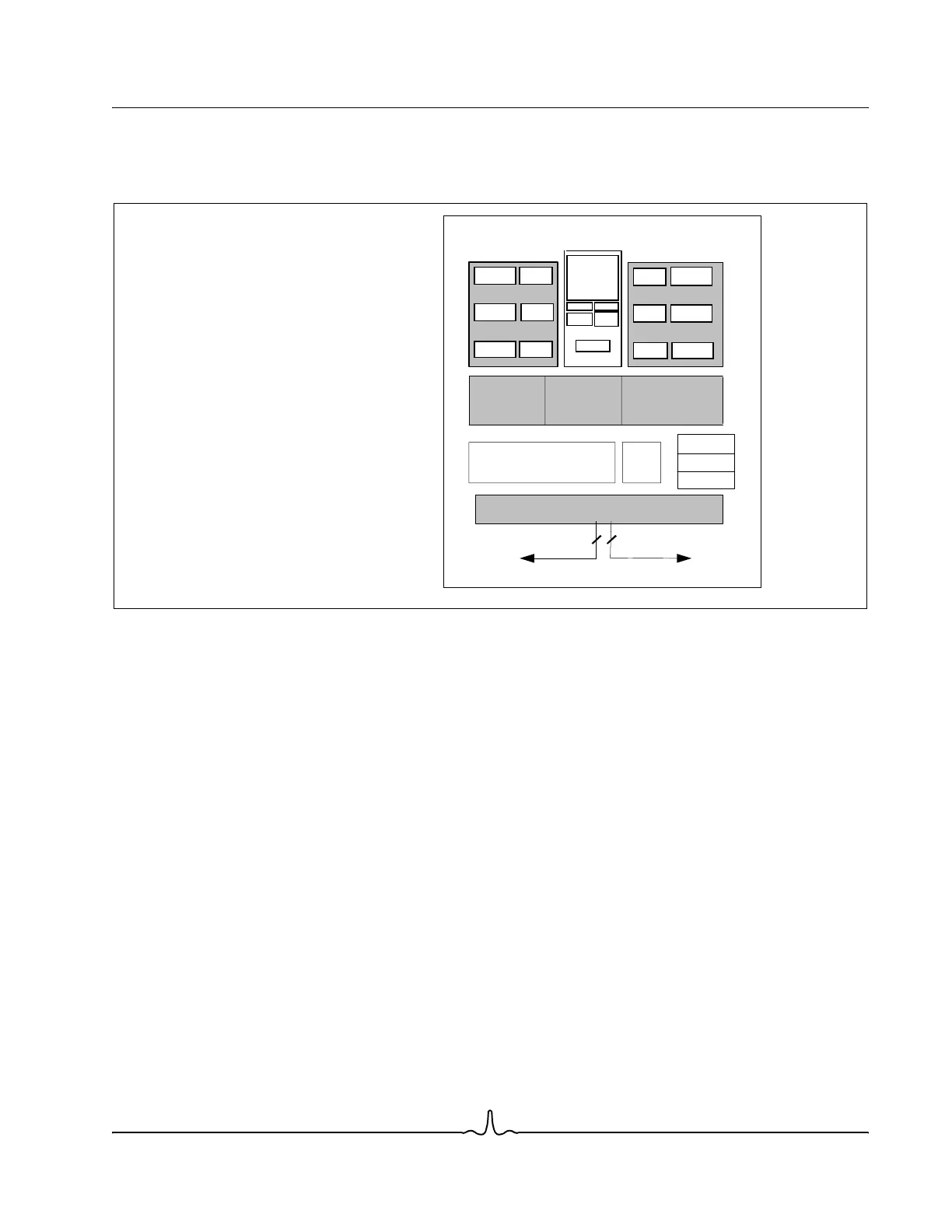

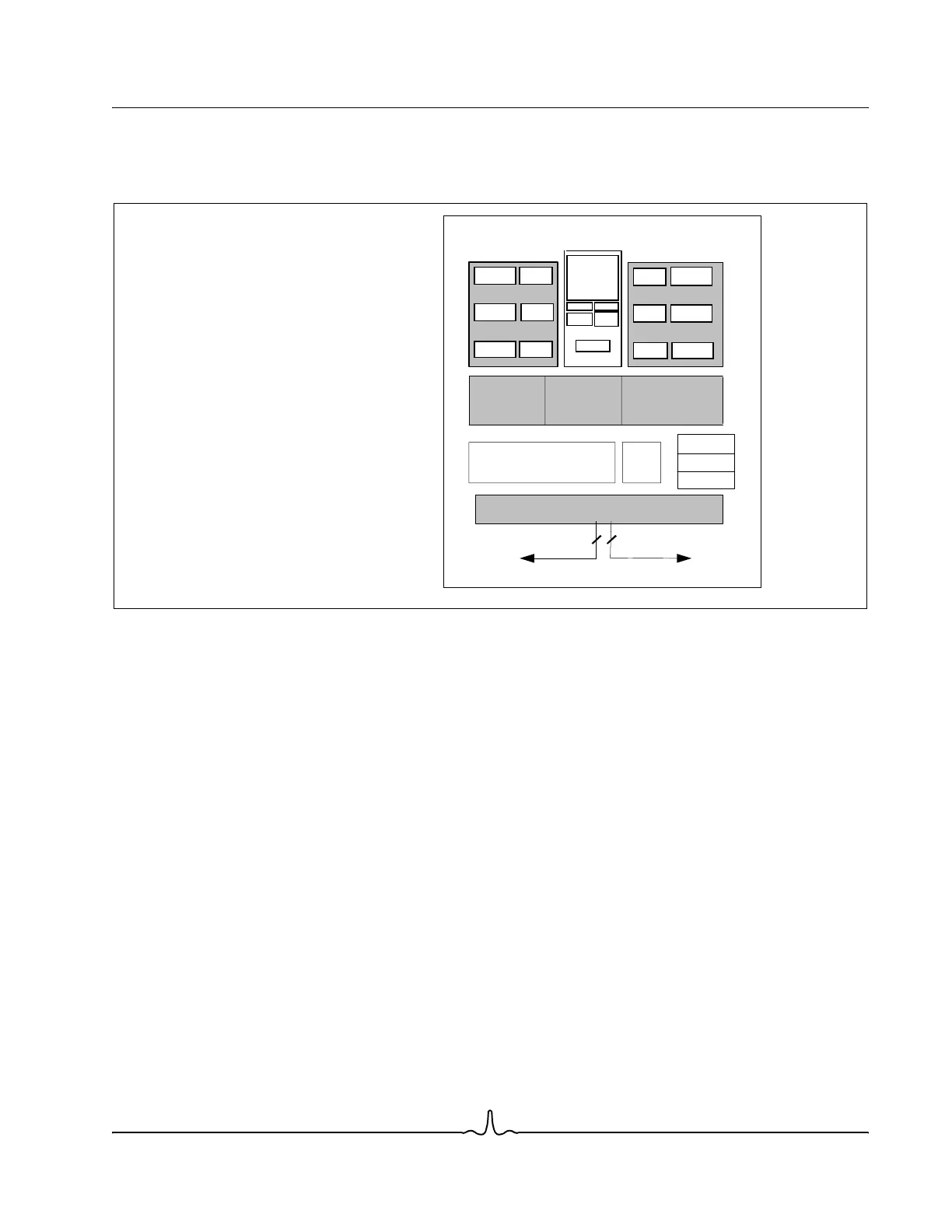

Figure 1-16 depicts a block diagram of the CPU. An overview of these functional blocks is presented in this section.

Figure 1-16: Block Diagram of the CPU

Execution Unit

Each thread processor (TP) can execute the following types of instructions:

1 an ALU for logical, shift, add, and subtract operations,

2 a MDU for multiply, divide, 32-bit and 16-bit (eDSP) multiply-accumulate operations,

3 a MIPS16e unit to decode 16-bit instructions to 32-bit instructions for execution,

4 a Floating-Point Unit (FPU), and

5 generates the address of a load/store instruction.

The processor core contains thirty-two 32-bit general-purpose registers used for scalar integer operations, address

calculation and translation from virtual to physical. The register file is fully bypassed to minimize latency in the six-stage

pipeline.

The execution unit includes:

• Branch unit for branch resolution and next instruction calculation

• MIPS32 and MIPS16e instruction decoding units

• ALU for performing the 32-bit and 16-bit (MIPS16e) arithmetic, shift, and logical operations.

• Address unit with a 32-bit adder used for calculating the next operand address

• Load and store aligners of partial word accesses

PerfCtr

CP0

s

TP

0

Terms:

RAC- ReadAhead Cache

eDSP - 16-bit DSP Extension

JTLB - Translation Lookaside Buffer

ALU - ISA decode & execution units

CP0

l

/CP0

s

- CP0 local and shared registers

GPR - General Purpose Registers

SMISB

LMB

BIU

EJTAG

D-Cache

RAC

MDU

eDSP

BIU - Bus (System) Interface Unit

LMB - Low-latency Memory Bus

64b

FPR

0

FPR/FCR - FPU General & Control Registers

PerfCtr - Performance Counters

FPU/FPE - Floating-Point Unit & Engine

MDU - Multiply-Divide Unit

MIPS16e - 16-bit Compression ISA

EJTAG/DSU - Debug Unit

I-Cache

0

GPR

MIPS16e

ALU CP0

l

TP

1

DSU

I-Cache

1

JTLB

FPR

1

FCR

1

FCR

0

L2 Cache

FP

U

FPE

CP

1

GPR

MIPS16e

ALUCP0

l

JTLB

CP

1

CP1- Coprocessor 1 Interface to the FPU

SMISB - Split-transaction MISB System Bus

256b

System/

Memory

Memory

Loading...

Loading...