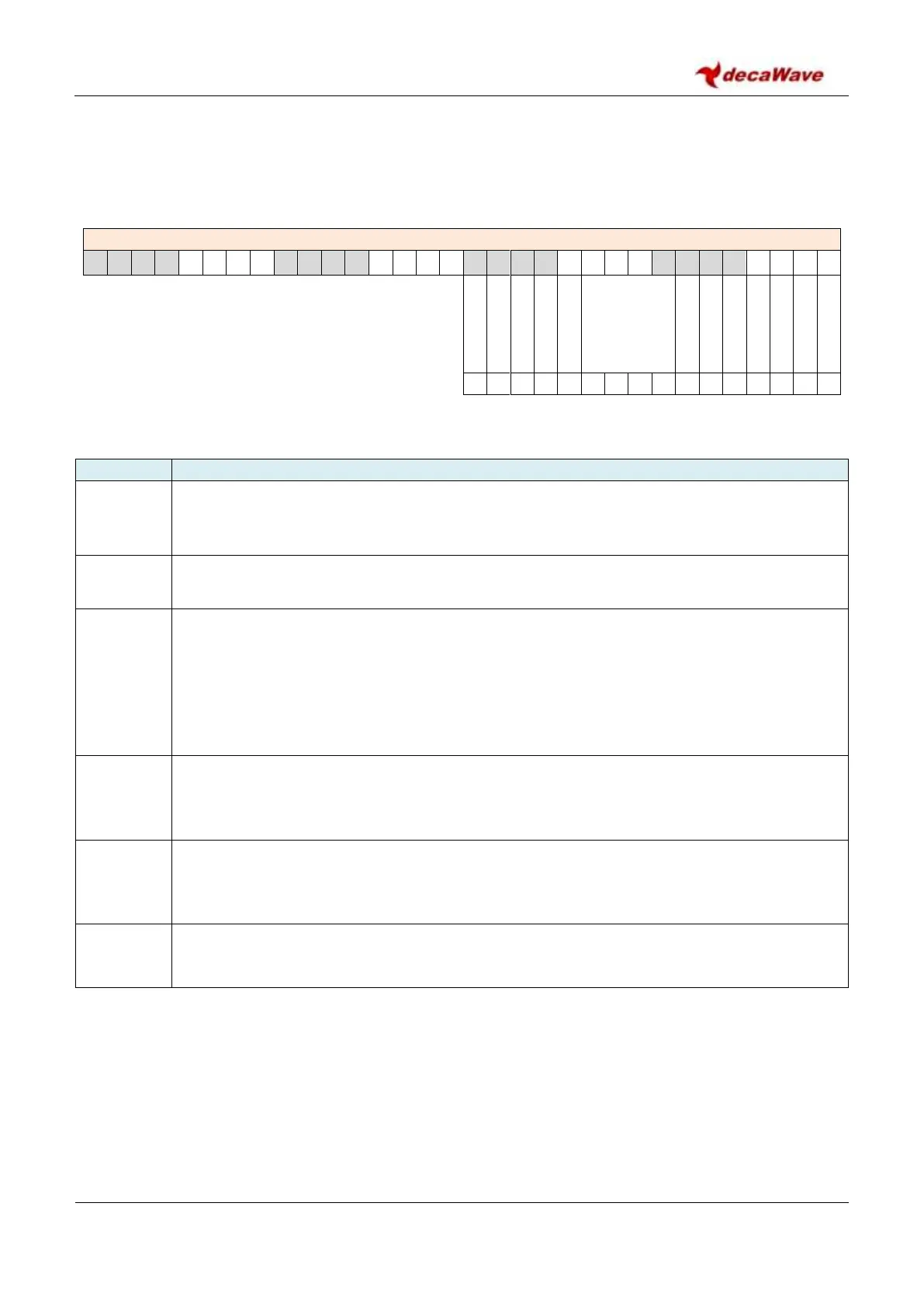

Register file: 0x2D – OTP Memory Interface, sub-register 0x06 is a 16-bit register used to control the

operation of the OTP memory through the process of reading and writing. The OTP_CTRL register contains

the following fields:

REG:2D:06 – OTP_CTRL – OTP Control

The fields of the OTP_CTRL register are described below:

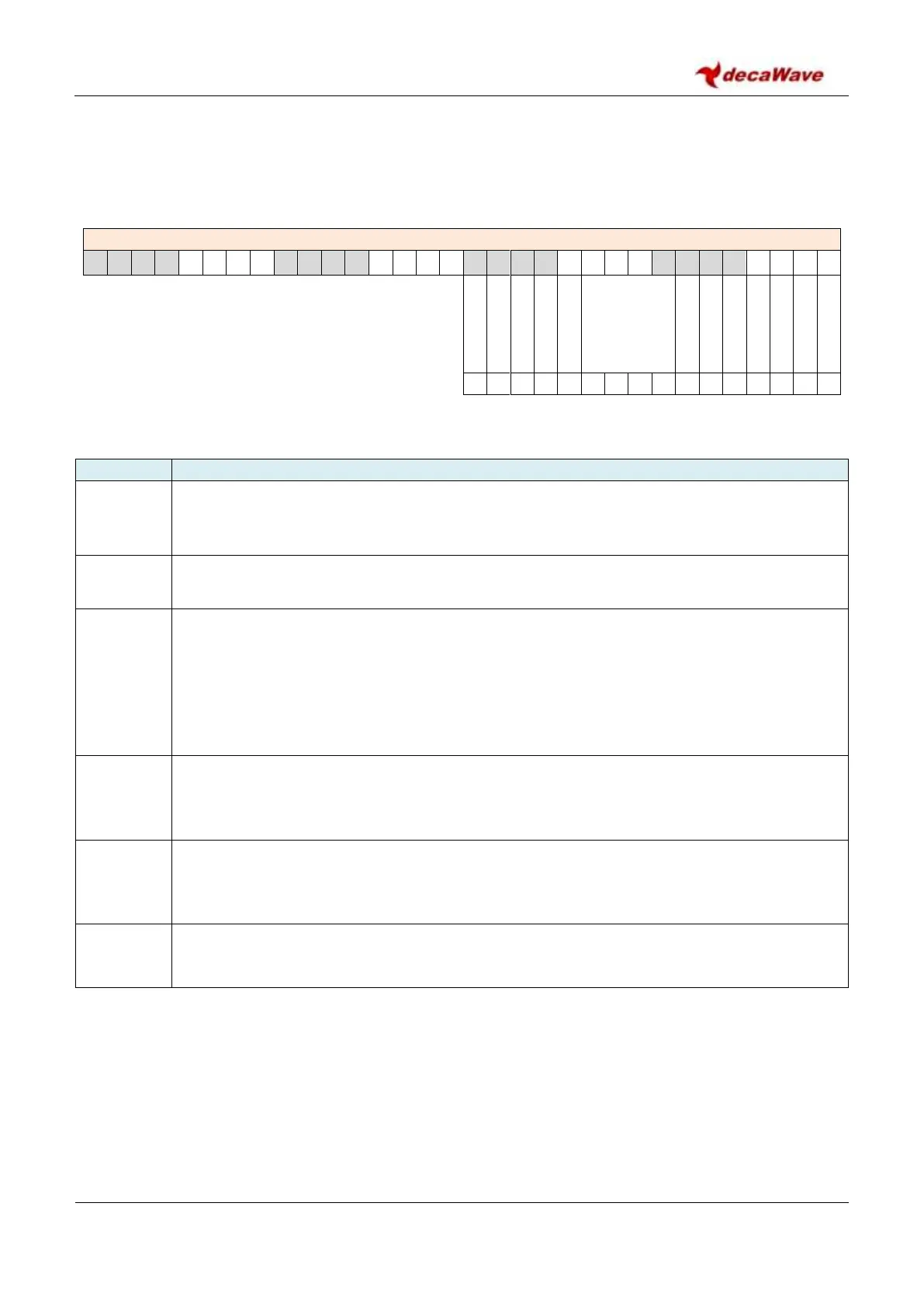

Description of fields within Sub-Register 0x2D:06 – OTP_CTRL

Reserved bits. May be overwritten with their default value.

This bit forces the OTP into manual read mode. This bit must be set if using the OTPREAD bit to

issue a read command.

This bit commands a read operation from the address specified in the OTP_ADDR register, the

value read will then be available in the OTP_RDAT register. This bit will automatically clear

when the read operation is done.

For details of the OTP memory map and the procedures to read and write OTP memory, please

refer to section 6.3 – Using the on-chip OTP memory.

OTP mode register write. This bit should be set to 1 then cleared when applying a new mode to

the OTP. This bit is used to configure the initial circuits of the OTP block. They used during the

programming of the OTP. For a description on how to drive these bits see the sample code in

6.3.2 Programming a value into OTP memory.

Setting this bit will cause the contents of OTP_WDAT to be written to OTP_ADDR. This bit

should be cleared once the programming has completed as indicated by Sub-Register 0x2D:08

– OTP_STAT. For a description on how to drive these bits see the sample code in 6.3.2

Programming a value into OTP memory.

OTP Mode register. These bits are used to configure the internal circuits of the OTP block. They

are used during the programming of the OTP. For a description on how to drive these bits see

the sample code in 6.3.2 Programming a value into OTP memory.

Loading...

Loading...