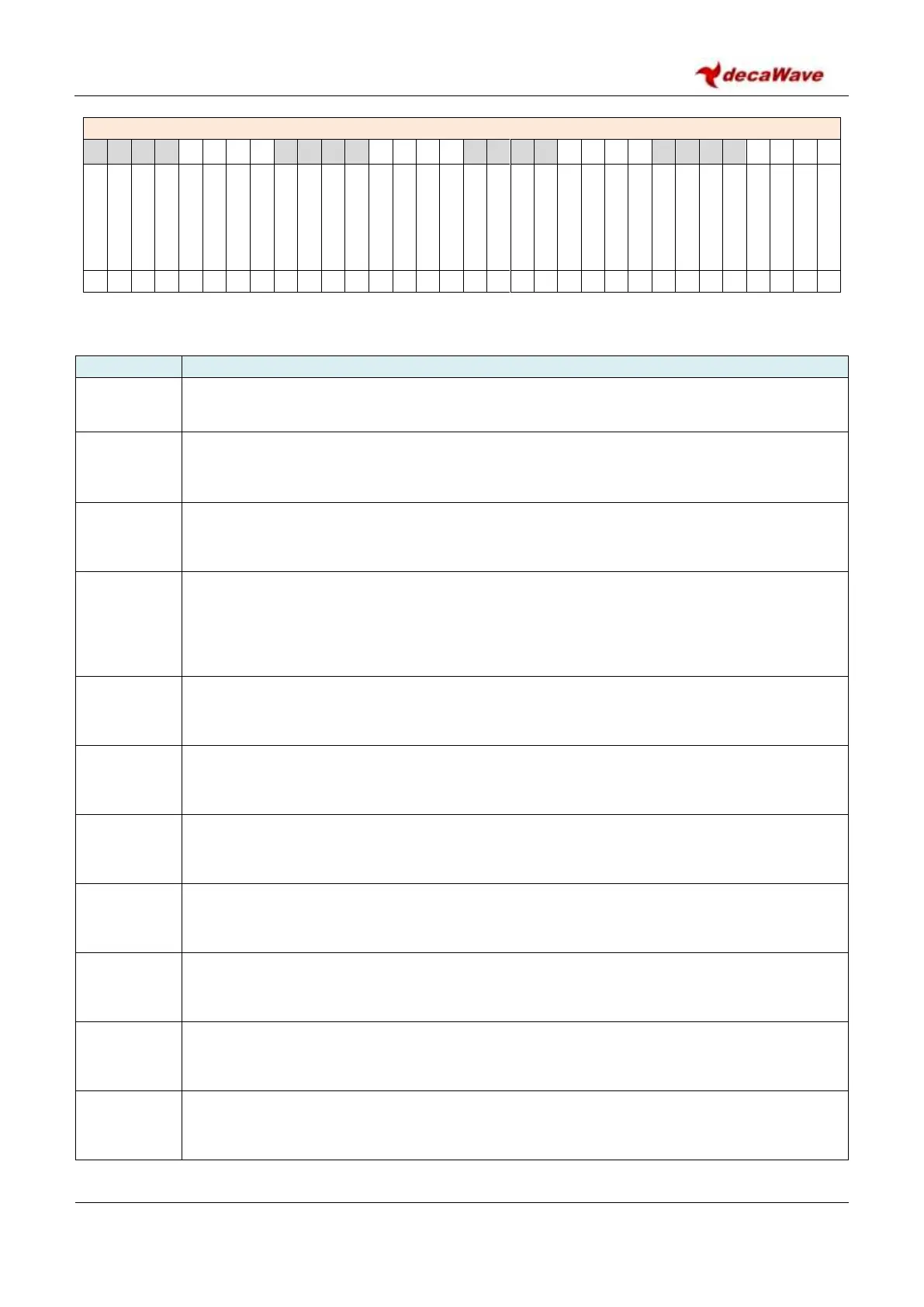

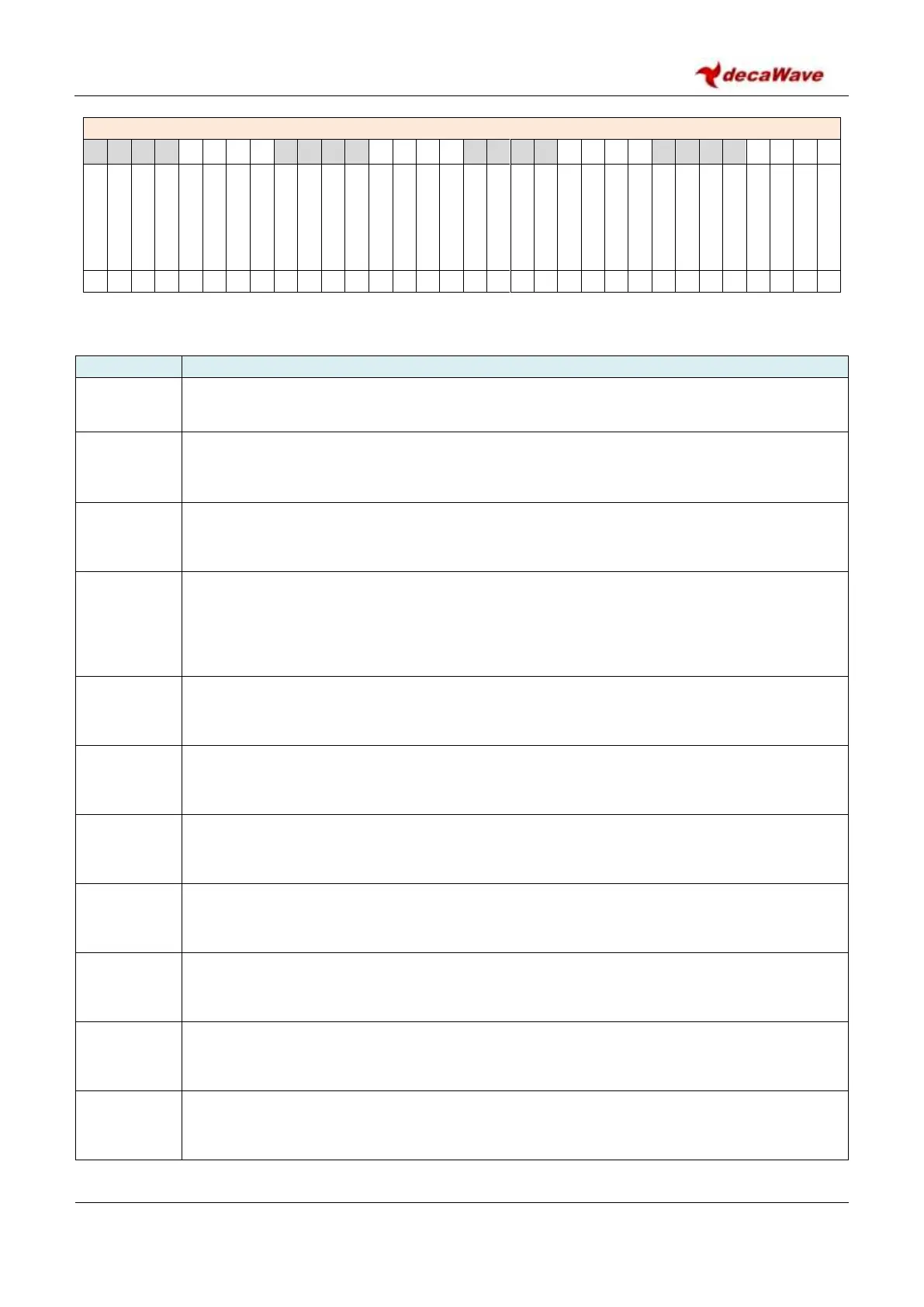

REG:0E:00 – SYS_MASK – System Event Mask

The system event mask bits of the SYS_MASK register identified above are individually described below:

Description of fields within Register file: 0x0E – System Event Mask Register

Mask clock PLL lock event. When MCPLOCK is 0 the CPLOCK event status bit will not

generate an interrupt. When MCPLOCK is 1 and the CPLOCK event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask external sync clock reset event. When MESYNCR is 0 the ESYNCR event status bit will

not generate an interrupt. When MESYNCR is 1 and the ESYNCR event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask automatic acknowledge trigger event. When MAAT is 0 the AAT event status bit will

not generate an interrupt. When MAAT is 1 and the AAT event status bit is 1, the hardware

IRQ interrupt line will be asserted to generate an interrupt.

AAT should be masked when the automatic acknowledge is not enabled so that spurious

interrupts cannot affect system behaviour.

Mask transmit frame begins event. When MTXFRB is 0 the TXFRB event status bit will not

generate an interrupt. When MTXFRB is 1 and the TXFRB event status bit is 1, the hardware

IRQ interrupt line will be asserted to generate an interrupt.

Mask transmit preamble sent event. When MTXPRS is 0 the TXPRS event status bit will not

generate an interrupt. When MTXPRS is 1 and the TXPRS event status bit is 1, the hardware

IRQ interrupt line will be asserted to generate an interrupt.

Mask transmit PHY Header Sent event. When MTXPHS is 0 the TXPHS event status bit will

not generate an interrupt. When MTXPHS is 1 and the TXPHS event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask transmit frame sent event. When MTXFRS is 0 the TXFRS event status bit will not

generate an interrupt. When MTXFRS is 1 and the TXFRS event status bit is 1, the hardware

IRQ interrupt line will be asserted to generate an interrupt.

Mask receiver preamble detected event. When MRXPRD is 0 the RXPRD event status bit will

not generate an interrupt. When MRXPRD is 1 and the RXPRD event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Mask receiver SFD detected event. When MRXSFDD is 0 the RXSFDD event status bit will not

generate an interrupt. When MRXSFDD is 1 and the RXSFDD event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

MLDEDONE

reg:0E:00

bit:10

Mask LDE processing done event. When MLDEDONE is 0 the LDEDONE event status bit will

not generate an interrupt. When MLDEDONE is 1 and the LDEDONE event status bit is 1, the

hardware IRQ interrupt line will be asserted to generate an interrupt.

Loading...

Loading...