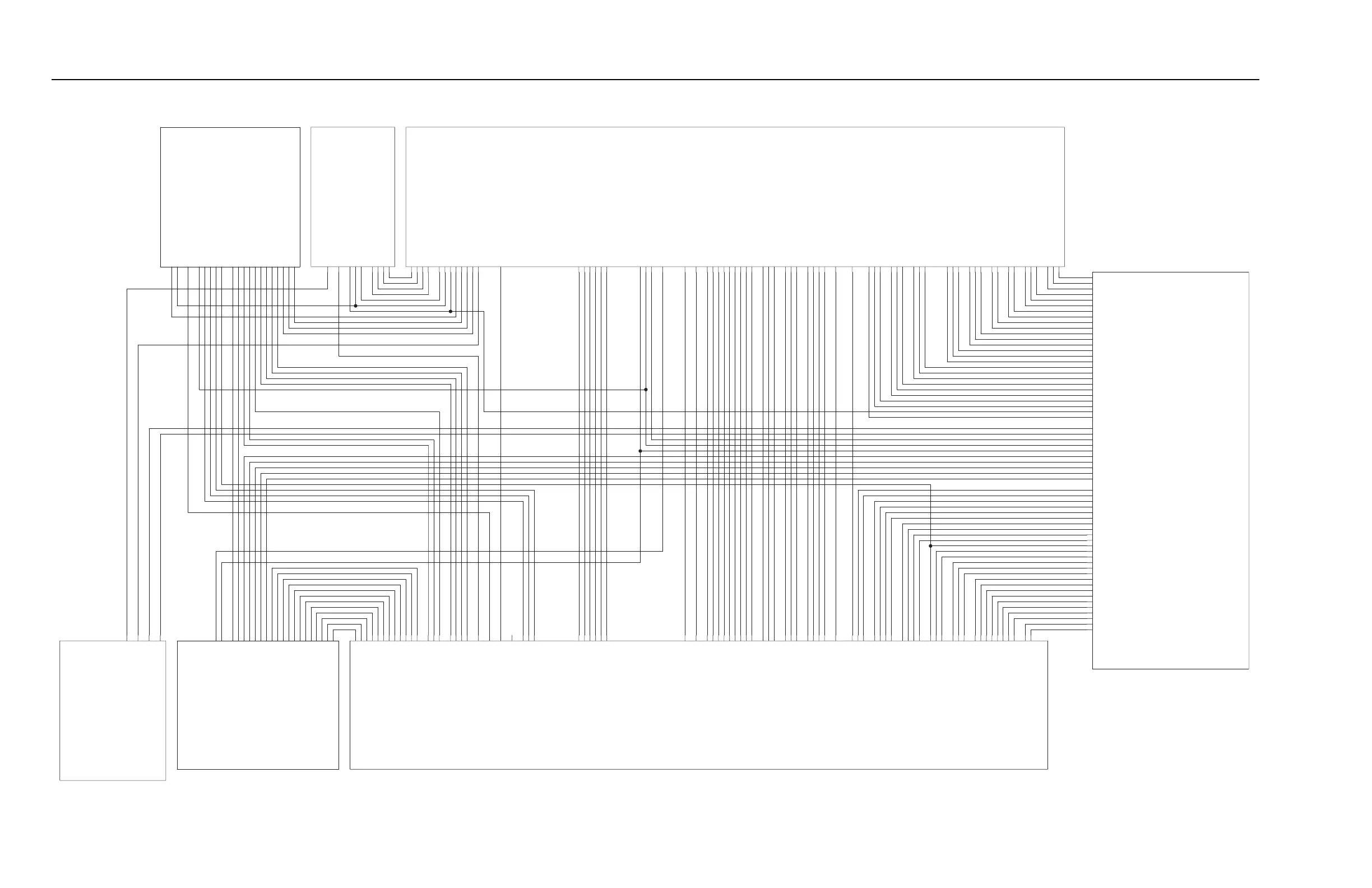

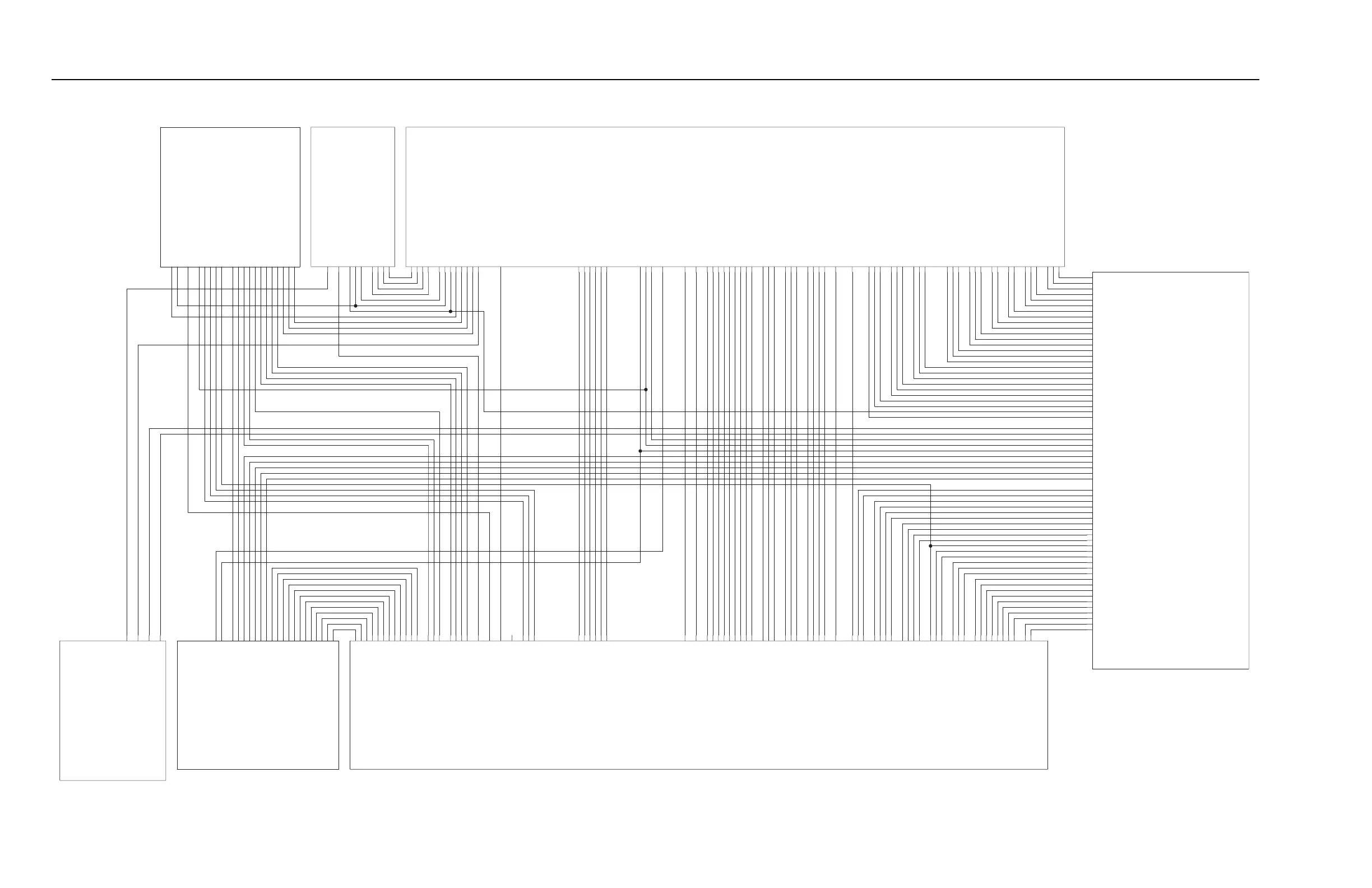

4-34 Controller Schematics (UHF)

4.4 Controller Schematics (UHF)

5MHZ_BNC_IN

USB1_MAKO_DP

USB2_MAKO_DP

USB2_MAKO_DM

FP_LED<0..12>

FP_FPGA_RST_N

USB1_MAKO_DM

MIC_BUTTON_INT_N

MIC_BUTTON

MIC_PTT_N

SPEAKER_AUDIO

MIC_AUDIO

SSI_ABACUS<2..0>

RXOMAP_SYNC_IN

TXOMAP_SYNC_TRIG_OUT

FPGA_ENET_RX_RESET_N

ETHERNET_ENABLE

RXOMAP_SYNC_OUT

1_4V_ROMAP_PG

BUFFER

ED_1_4V_ROMAP_PG

2_775VA_PG

BOUNDARY_SCAN<9..0>

1_4V_TOMAP_PG

1_4V_ROMAP_PG

5V_MON

FPGA_TDO

FPGA_TMS

FPGA_TDI

FPGA_TCK

TXOMAP_SPARE3

FPGA_BP_OP1_CS1_N

FPGA_SPI<0..6>

RCVR_SPI<0..7>

ABA_SPI<0..3>

RXOMAP_SPARE2

TXOMAP_SPARE2

TXOMAP_SPARE1

RXOMAP_SPARE3

FP_FPGA_RST_N

RXOMAP_SPARE1

BP_FPGA

_MISO

FPGA_BP_SPI_CLK

FPGA_BP_WIRELINE_BCLK

FPGA_BP_WIRELINEL34_FSYNC

FPGA_BP_WIRELINE34_RXD

BP_FPGA_WIRELINE34_TXD

FPGA_BP_WIRELINE12_FSYNC

FPGA_BP_WIRELINE12_RXD

BP_FPGA_WIRELINE12_TXD

STA_FPGA<0..7>

FP_FPGA_EXT_REF

FP_LED<0..12>

MAKO_USB_CRNT_LIMIT

FPGA_BP_WIRELIN

E_MCLK

FPGA_BP_WL1_CS_N

FPGA_BP_WL2_CS_N

FPGA_BP_MOSI

FPGA_BP_OP2_CS1_N

FPGA_BP_OP1_CS3_N

FPGA_BP_OP1_CS2_N

CLK_FPGA_RXOMAP_32_768KHZ

CLK_FPGA_TXOMAP_32_768KHZ

FPGA_EX_DISABLE_N

FPGA_GPIO_<7..0>

FPGA_BP_PA_ADDR1

FPGA_BP_PA_ADDR0

FPGA_BP_OP2_CS3_N

FPGA_BP_OP2_CS2_N

RCVR_ADD

R<2..0>

MAKO_FPGA_RST_DET_N

MAKO_FPGA_V9_DET

FPGA_MAKO_MECH_SW_N

FPGA_EX_ADDR<2..0>

SPI_CS_ADDR<3..0>

FPGA_MAKO_SPI<3..0>

SPIF_TXOMAP<3..0>

SPIF_RXOMAP<4..0>

CLK_FPGA_WBCODEC_12MHZ

CLK_FPGA_TXOMAP_12MHZ

CLK_FPGA_RXOMAP_12MHZ

FPGA_EX_RESET_N

FPGA_ENET_RX_RESET_N

FPGA_WBCODEC_BP_

RESET_N

FPGA_TXOMAP_SPI_IRQ_N

CLK_FPGA_MAKO_24_576MHZ

BUFFERED_1_4V_ROMAP_PG

1_4V_TOMAP_PG

1_4V_ROMAP_PG

FPGA_TDO

FPGA_TMS

FPGA_TDI

FPGA_TCK

SSI_CODEC12<3..0>

RXOMAP_FPGA_RST

TXOMAP_FPGA_RST

FPGA_RESET_TXOMAP_N

FPGA_RESET_RXOMAP_N

ROMAP_FPGA_WDRST_N

TOMAP_FP

GA_WDRST_N

574

HEC_AC_FPGAHEC_AC_PBJHEC_AC_FP

WIRELINE_ID

MAKO_BP_RSSI

RF_RELAY_CONTROL

AUX_RX_AUDIO

TX_AUDIO_PRE

TX_AUDIO

FPGA_BP_PA_ADDR0

AC_FAIL

OPT_IRQ_N

OPTION1_ID

OPTION2_ID

FPGA_BP_WIRELINE12_FSYNC

FPGA_BP_WIRELINE12_RXD

RCV

R_SPI_<0..7>

FPGA_BP_WL1_CS_N

FPGA_BP_WIRELINE_MCLK

FPGA_BP_WIRELINE34_RXD

FPGA_BP_MOSI

FPGA_BP_WIRELINE34_FSYNC

PTEMP+

BP_FPGA_WIRELINE12_TXD

BP_FPGA_WIRELINE34_TXD

FPGA_BP_WIRELINE_BCLK

FPGA_BP_WL2_CS_N

DMCS

OMAP_GPIO_7

OMAP_GPIO_9

BP_FPGA_MISO

FPGA

_SPI_<0..6>

CLK_EX_16_8MHZ

TXDATA_PL_DPL

ABA_SPI_<0..3>

FPGA_BP_SPI_CLK

SSI_ABACUS<2..0>

OMAP_GPIO_10

OMAP_GPIO_8

OMAP_GPIO_6

EX_ENABLE

RX_AUDIO

FPGA_BP_PA_ADDR1

FPGA_EX_RESET_N

SSI_TRIDENT<2..0>

FPGA_ENET_RX_RESET_N

FPGA_WBCODEC_BP_RESET_N

PA_ENABLE

ANTENNA_RELAY

AB

ACUS_SYNCB

RX_ATTEN

OMAP_GPIO_5

OMAP_GPI_1

OMAP_GPI_4

OMAP_GPIO_2

OMAP_GPIO_3

1_4V_TOMAP_PG

FPGA_GPIO_<7..0>

CLK_RX_16_8MHZ

FPGA_BP_OP2_CS3_N

FPGA_BP_OP2_CS2_N

FPGA_BP_OP2_CS1_N

FPGA_BP_OP1_CS3_N

FPGA_BP_OP1_CS2_N

FPGA_BP_OP1_CS1_N

3

HEC_AC_EXT_INT

FPGA_WBCODEC_BP_RESET_N

TXDATA_PL_DPL

AUX_RX_AUDIO

ANALOG_MUX1

ANALOG_MUX2

I2C_TXOMAP_SDA

CLK_FPGA_WBCODEC_12MHZ

ANALOG_MUX3

SPEAKER_AUDIO

TX_AUDIO_PRE

TXAUD_MIC_FLTR

ANALOG_MUX0

I2C_TXOMAP_SCL

I2C_RXOMAP_SDA

I2C_RXOMAP_SCL

MAKO_C

ODEC_AUDIO_P

TXAUD_MIC_TDATA

SSI_CODEC_WB<3..0>

MIC_AUDIO

RX_AUDIO

TX_AUDIO

TXOMAP_SYNC_TRIG_OUT

RXOMAP_SYNC_OUT

I2C_TXOMAP_SDA

I2C_RXOMAP_SCL

I2C_RXOMAP_SDA

ANALOG_MUX2

ANALOG_MUX3

GPI_4

GPIO_2

GPIO_3

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

EX_ENABLE

SSI_TRIDEN

T<2..0>

SSI_ABACUS<2..0>

AC_FAIL

OPTION2_ID

RF_RELAY_CONTROL

CLK_FPGA_MAKO_24_576MHZ

RCVR_ADDR<2..0>

MAKO_MECH_SW_N

RESET_OUT_RXOMAP_N

TXOMAP_FPGA_RST

SSI_CODEC12<3..0>

FPGA_IRQ_N

RXOMAP_FPGA_RST

I2C_TXOMAP_SCL

SPI_ENET<3..0>

GPI_1

MIC_BUTTON

SSI_CODEC_

WB<3..0>

ANALOG_MUX0

TXAUD_MIC_FLTR

ANALOG_MUX1

MAKO_CODEC_AUDIO_P

TXAUD_MIC_DATA

MAKO_USB_CRNT_LIMIT

RXOMAP_SYNC_IN

CLK_FPGA_RXOMAP_12MHZ

CLK_FPGA_TXOMAP_12MHZ

BOUNDARY_SCAN<9..0>

USB1_MAKO_DM

ETHERNET_ENABLE

RXOMAP_SPARE1

SPIF_RXOMAP<4..0>

FPGA_MAKO_SPI<3..0>

USB2_MAKO_DP

RXOMAP_SPARE3

OPTION

1_ID

FPGA_EX_DISABLE_N

MAKO_BP_RSSI

WIRELINE_ID

MIC_BUTTON_INT_N

TXOMAP_SPARE1

RX_ATTEN

DMCS

TXOMAP_SPARE2

MIC_PTT_N

TXOMAP_SPARE3

RXOMAP_SPARE2

USB1_MAKO_DP

USB2_MAKO_DM

ABACUS_SYNCB

GPIO_5

RESET_OUT_TXOMAP_N

MAKO_FPGA_V9_DET

RESET_IN_TXOMAP_N

RESET_IN_RXOMAP_N

MAKO_FPGA_RST_DET_N

SPIF_TXOMAP<3..0>

CLK_FPGA_TXOMAP_32_768KHZ

CLK_FPGA_RXOMAP_32_768KHZ

PTEMP+

OPT_IRQ_N

ANTENNA_RELAY

PA_ENABLE

SPI_CS_ADDR<3..0>

FPGA_EX_ADDR<2..0>

2_775VA_PG

STA_FPGA_<0..7>

CLK_RX_16_8_MHZ

CLK_EX_16_8MHZ

6

1

2

HEC_AC_STATREF

HEC_OMAP1710

HEC_AC_ANALOG

5V_MON

Controller – Main Schematic Diagram (Kit No. CLN8502)

Loading...

Loading...