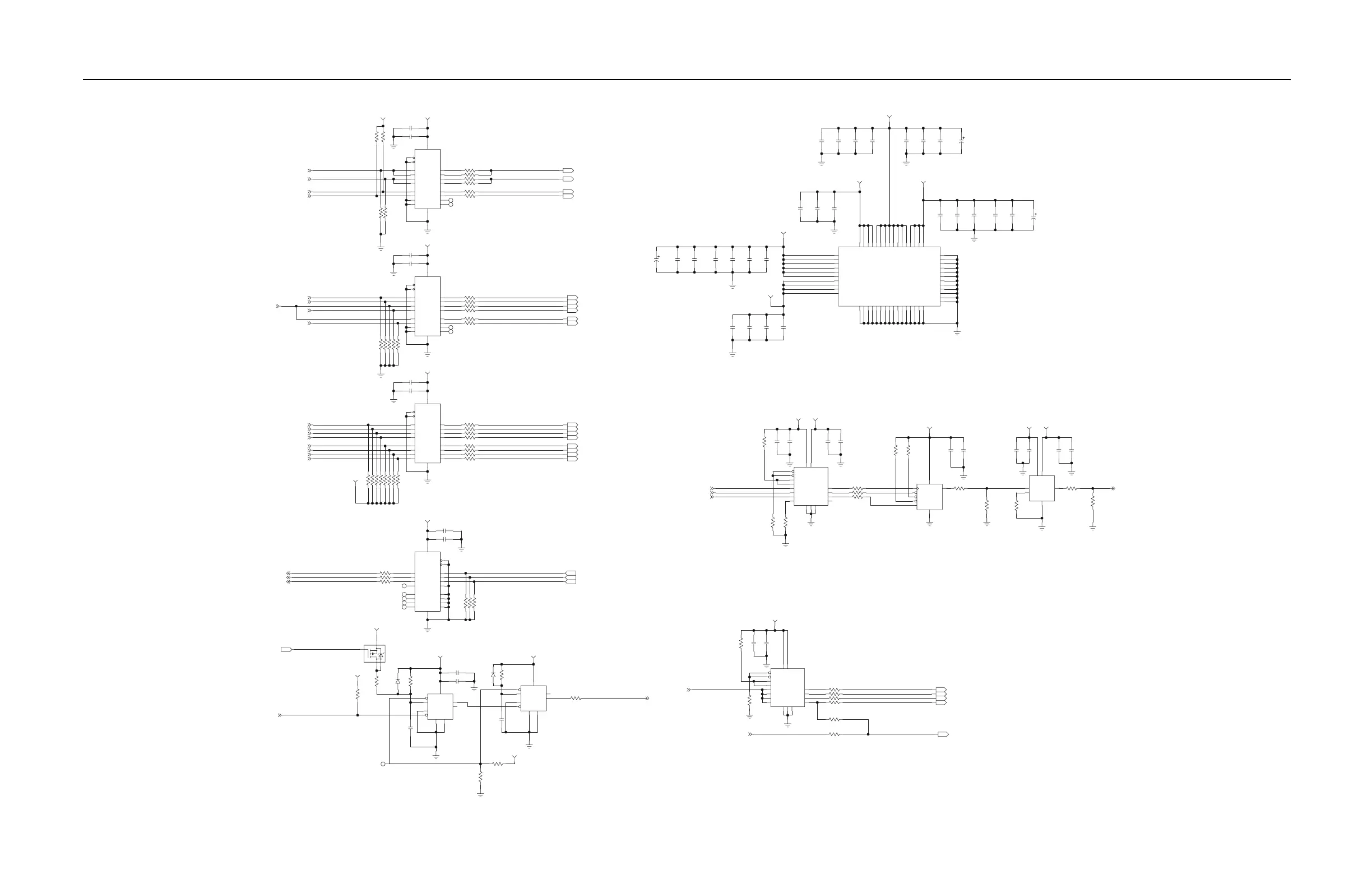

Controller Schematics (UHF) 4-41

7

FPGA_SPI_CLK

FPGA_WL2_LATCH_CS_N

FPGA_SPI_MOSI

FPGA_WL1_LATCH_CS_N

R2215M5

R2212M5 10K

10K

GND

Y0A0

A1

Y3

Y4

A5

A6

Y7

EN_OE1

EN_OE2

Y1

Y2A2

A3

A4

Y5

Y6

A7

VCC

2

4

6

8

11

13

15

17

1

19

C2201M5

C2200M5

0.1UF

.01UF

20

5V

3_3V

U2200M5

MC74HCT244

18

16

14

12

9

7

5

3

R2225M5

R2224M5

R2223M5

R2222M5

R2221M5

R2220M5

NC

NC

49.9

49.9

49.9

49.9

0

0

10

R2206M5

R2203M5

10K

10K

GND

Y0A0

A1

Y3

Y4

A5

A6

Y7

EN_OE1

EN_OE2

Y1

Y2A2

A3

A4

Y5

Y6

A7

VCC

NC

NC

R2232M5

R2231M5

R2230M5

R2229M5

R2228M5

R2227M5

0

0

0

0

0

0

18

16

14

12

9

7

5

3

FPGA_BP_WIRELINE_BCLK

FPGA_BP_WIRELINE12_FSYNC

FPGA_BP_WIRELINE12_RXD

FPGA_BP_WIRELINE34_RXD

FPGA_BP_WIRELINE_MCLK

FPGA_BP_WIRELINEL34_FSYNC

OUT

OUT

OUT

OUT

OUT

OUT

U2201M5

C2203M5

.01UF

MC74HCT244

2

4

6

8

11

13

15

17

1

19

10 20

C2202M5

0.1UF

5V

R2218M5

R2216M5

R2213M5

R2207M5

R2204M5

10K

10K

10K

10K

10K

FPGA_WL12_RXD

FPGA_WL_M_B_CLK

FPGA_WL34_RXD

FPGA_WL34_FSYNC

FPGA_WL12_FSYNC

GND

Y0A0

A1

Y3

Y4

A5

A6

Y7

EN_OE1

EN_OE2

Y1

Y2A2

A3

A4

Y5

Y6

A7

VCC

U2202M5

R2240M5

R2239M5

R2238M5

R2237M5

R2236M5

R2235M5

R2234M5

R2233M5

C2205M5

.01UF

0

0

0

0

0

0

0

0

MC74HCT244

2

4

6

8

11

13

15

17

1

19

20

18

16

14

12

9

7

5

3

R2219M5

R2217M5

R2214M5

R2208M5

R2205M5

R2202M5

R2201M5

R2200M5

10

10K

10K

10K

10K

10K

10K

10K

10K

3_3V

FPGA_OP1_CS2_N

FPGA_OP2_CS3_N

FPGA_PA_ADDR0

FPGA_PA_ADDR1

FPGA_OP2_CS2_N

FPGA_OP1_CS1_N

FPGA_OP1_CS3_N

FPGA_OP2_CS1_N

NC

NC

NC

NC

NC

U2203M5

R2211M5

R2210M5

R2209M5

0

0

0

MC74LVX244

18

16

14

12

9

7

5

3

FPGA_WIRELINE12_TXD

FPGA_WIRELINE34_TXD

BP_FPGA_MISO_B

GND

Y0

A0

A1

Y3

Y4

A5

A6

Y7

EN_OE1

EN_OE2

Y1

Y2

A2

A3

A4

Y5

Y6

A7

VCC

R2242M5

R2241M5

R2226M5

C2207M5

C2206M5

0.1UF

.01UF

10K

10K

10K

DNP

2

4

6

8

11

13

15

17

1

19

10

20

3_3V

BP_FPGA_MISO

BP_FPGA_WIRELINE34_TXD

BP_FPGA_WIRELINE12_TXD

IN

IN

IN

FPGA_BP_OP2_CS1_N

FPGA_BP_PA_ADDR0

FPGA_BP_OP1_CS1_N

FPGA_BP_OP1_CS3_N

FPGA_BP_OP2_CS3_N

FPGA_BP_OP2_CS2_N

FPGA_BP_OP1_CS2_N

FPGA_BP_PA_ADDR1

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

C2204M5 0.1UF

5V

FPGA_BP_WL2_CS_N

FPGA_BP_MOSI

FP

GA_BP_SPI_CLK

FPGA_BP_WL1_CS_N

OUT

OUT

OUT

OUT

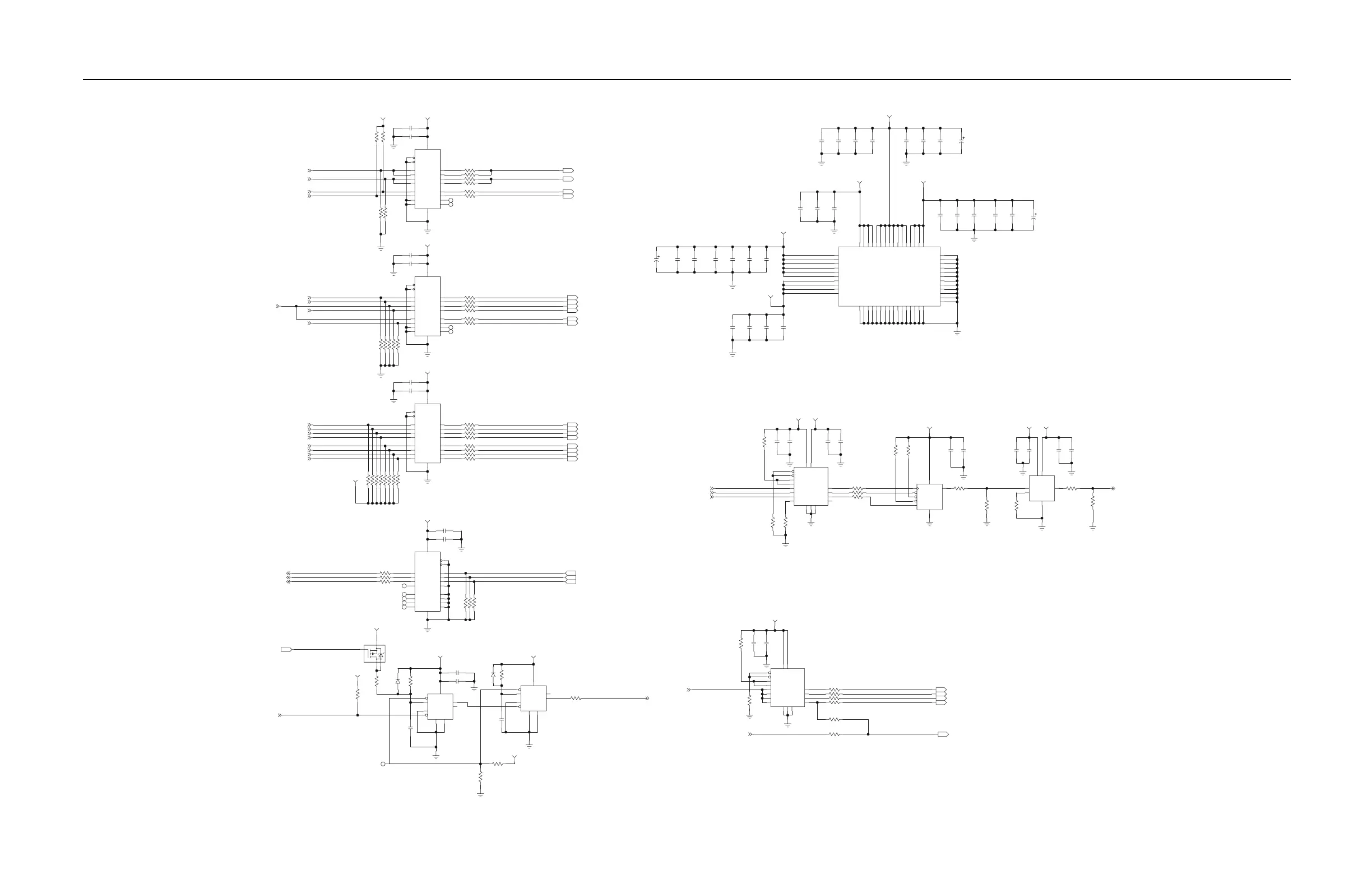

Q2200M5

SI8401DB

2

3

1

4

BUFFERED_1_4V_ROMAP_PG

3_3V

IN

GND

VCC

Q*

Q

GND_CX

A

CX_RX

B

RESET

U2207M5

R2257M5

C2248M5

C2247M5 0.1UF

.01UF

475K

MC74HC4538A

4

5

2

8

1

6

7

3

3_3V

TP2200M5

C2246M5

10UF

TEST_POINT

1

16

R2270M5

R2269M5

D2200M5

BAS52

332

100K

3_3V

CLK_FPGA_WD_32_768KHZ

PLACE PULL UP TO ENABLE WATCH DOG.

PLACE PULL DOWN TO DISABLE WATCH DOG.

R2259M5

R2258M5

1K

DNP

1K

3_3V

GND

VCC

Q*

Q

GND_CX

A

CX_RX

B

RESET

U2207M5

R2260M5

D2201M5

C2249M5

.01UF

BAS52

1K

MC74HC4538A

12

11

14

8

15

10

9

13

16

3_3V

R2261M5

0

FPGA_PROG_B

1_875V

C2225M5C2224M5C2223M5C2221M5

.01UF .01UF 0.1UF 0.1UF

C2231M5

C2228M5C2227M5C2226M5

100PF

50V 50V

100PF

16V

1UF

10UF

12

3_3V

C2235M5

C2234M5C2233M5

C2232M5

C2230M5C2229M5

.01UF 0.1UF

0.1UF

100PF

50V

1UF

16V

10UF

1

2

VCCAUX4

VCCAUX3

VCCAUX2

VCCAUX1

VCCINT6

VCCINT5

VCCINT4

VCCINT3

GND25

GND26

GND27

GND28

GND18

GND19

GND20

GND21

GND22

GND12

GND13

GND14

GND15

VCCO_3_4

VCCO_1_2

VCCO_1_3

VCCO_1_4

VCCO_2_1

VCCO_0_2

GND7

VCCO_3_2

VCCO_3_3

GND1

GND2

VCCO_2_2

VCCO_2_3

VCCO_2_4

VCCO_3_1

GND16

GND17

GND8

GND9

GND10

GND11

GND3

GND4

GND6

VCCINT1

VCCINT2

GND23

GND24

VCCO_0_1

VCCO_0_3

VCCO_0_4

VCCO_1_1

GND5

U2000M5

XC3S200AN

B5

B9

B13

E8

E15

H12

J15

N15

M9

R4

R8

R12

D2

H2

J5

M2

K7

K9

L11

L15

M5

M12

P3

P14

R6

R10

T1

T16

A1

F6

G8

G10

G15

H9

J8

K2

A16

B7

B11

C3

C14

E5

E12

F2

E11

F5

L12

M6

G7

G9

H8

J9

K8

K10

1_2V_FPGA_CORE

C2218M5C2217M5

C2215M5C2213M5

.01UF .01UF 100PF

50V 16V

1UF

3_3V

C2216M5C2214M5C2212M5

C2211M5C2210M5

C2209M5

C2208M5

10UF

12

16V

1UF

100PF

50V 50V

100PF .01UF .01UF .01UF

3_3V

C2222M5

C2220M5

C2219M5

100PF

50V 0.1UF 0.1UF

FPGA EXTERNAL FLASH CIRCUIT

EXTERNAL FLASH CIRCUIT IS ONLY NEEDED

IF A NON XILINX 3AN FPGA IS USED.

VCCB

VCCA

GND3

GND2

GND1

B1_2

B1_1

B2_2

B2_1

A2_2

A2_1

A1_2

A1_1

DIR2

DIR1

OE2

OE1

R2247M5

R2246M5

10K

DNPDNP

10K

4

6

5

7

2

3

8

9

17

15

14

FPGA_CSO_B

FPGA_MOSI

FPGA_CCLK

13

11

12

10

1

16

U2204M5

R2250M5

R2249M5

R2248M5

DNP

0

DNP

0

0

DNP

SN74AVC4T245

DNP

SI

CS

SCK

R2245M5

C2239M5

C2238M5

C2237M5

C2236M5

0.1UF DNP

.01UF

DNP

0.1UF

DNP

.01UF

DNP

10K

DNP

1_875V 3_3V

R2252M5

R2251M5

10K DNP

10K DNP

3_3V

THIS RESISTOR IS NEEDED

MISO INPUT ON FPGA.

TO TERMINATED THE

SO

VCC

SCK

CS

GND

RESET

WP

SI

B

DIR

VCCA

VCCB

GND

A

U2206M5

U2205M5

R2268M5

R2256M5

R2255M5

R2254M5

R2253M5

0DNP

DNP

10K

0DNP

10K

10K

DNP

AT45DB041D

DNP

4

3

2

1

8

6

5

SN74AVC1T45

DNP

C1C2

B2

B1

A1

A2

SO

FPGA_MISO

C2245M5

C2244M5

C2243M5

C2242M5

C2241M5

C2240M5

DNP

0.1UF

.01UF

DNP

0.1UF

DNP

DNP.01UF

DNP

0.1UF

.01UF

DNP

3_3V1_875V

R2243M5

C2251M5

C2250M5

0.1UF

.01UF

10K

1_875V

VCCB

VCCA

GND3

GND2

GND1

B1_2

B1_1

B2_2

B2_1

A2_2

A2_1

A1_2

A1_1

DIR2

DIR1

OE2

OE1

R2244M5

10K

4

6

5

7

2

3

8

9

17

15

14

FPGA_MAIN_RESET_N

FPGA_RESET_RXOMAP_ALT_N

U2208M5

R2267M5

R2266M5

R2265M5

R2264M5

R2263M5

R2262M5

0

0

0

0

0

DNP

0

SN74AVC4T245

13

11

12

10

1

16

FPGA_RESET_TXOMAP_N

FPGA_EX_RESET_N

FPGA_WBCODEC_BP_RESET_N

FPGA_ENET_RX_RESET_N

FPGA_RESET_RXOMAP_N

OUT

OUT

OUT

OUT

OUT

Controller – FPGA Logic Schematic Diagram (Kit No. CLN8502)

Loading...

Loading...