1193

CS/CJ/NSJ Series Instructions Reference Manual (W474)

4. Instruction Execution Times and Number of Steps

4-2 CJ1 CPU Unit Instruction Execution Times and Number of Steps

4

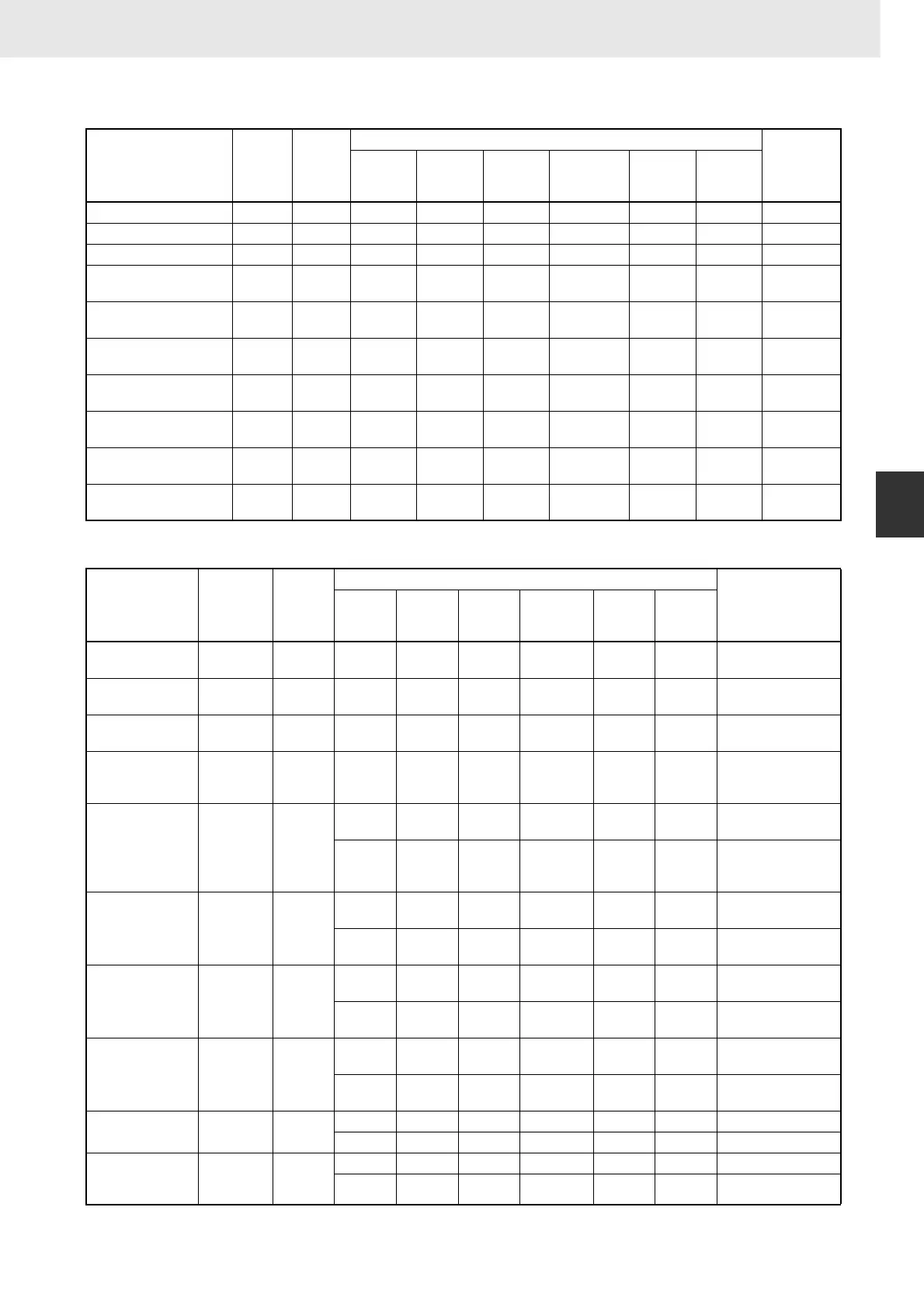

4-2-29 Other Instructions

4-2-29 Other Instructions

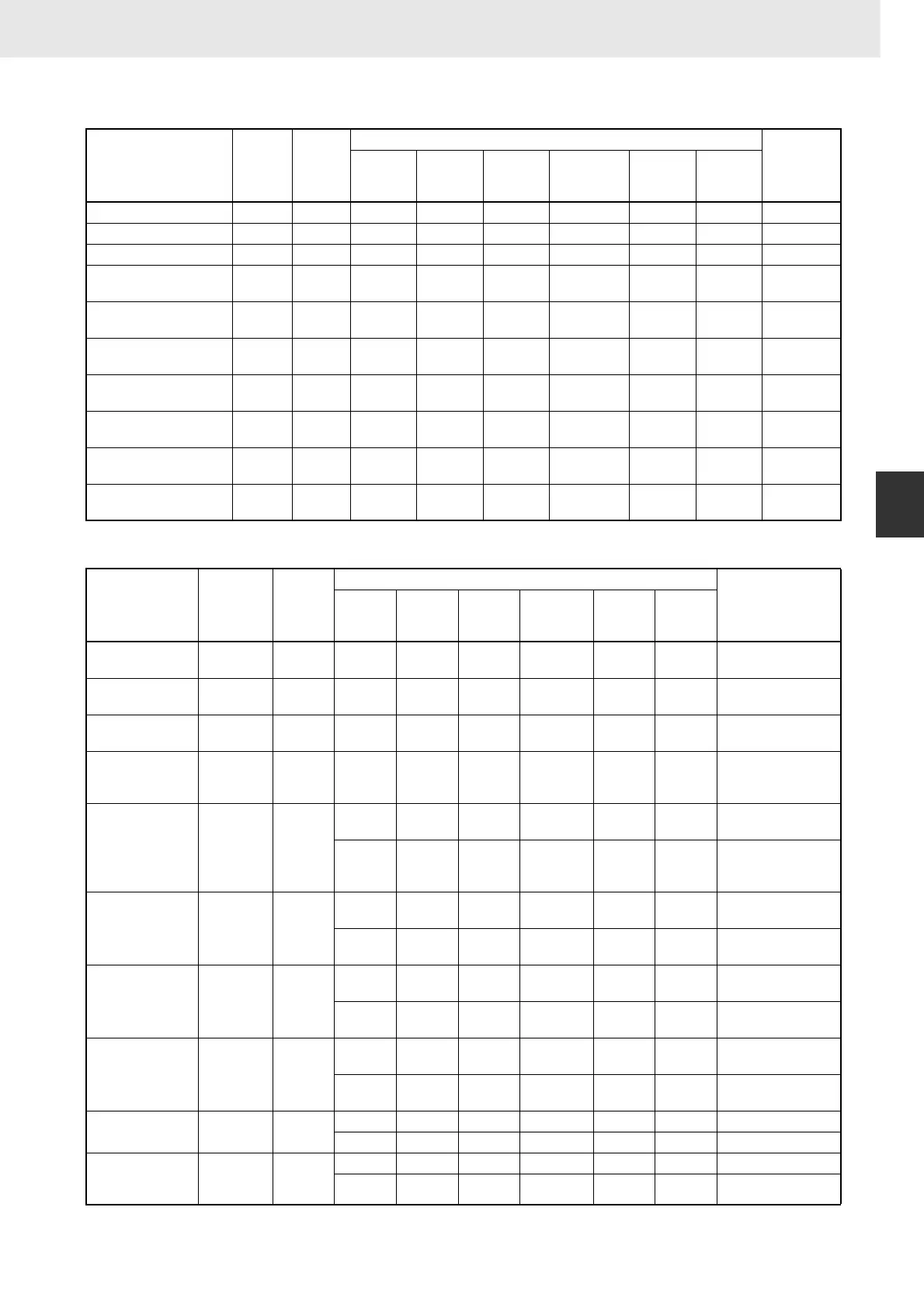

4-2-30 Block Programming Instructions

Instruction Mne-

monic

Length

(steps)

ON execution time (µs) Condi-

tions

CJ1H

CPU6@

H-R

CJ1H

CPU6@

H

CJ1G

CPU4@

H

CJ1M

CPU12/13/

22/23

CJ1M

CPU11/

21

CJ1G

CPU4@

SET CARRY STC 1 0.048 0.06 0.06 0.15 0.15 0.12 ---

CLEAR CARRY CLC 1 0.048 0.06 0.06 0.15 0.15 0.12 ---

SELECT EM BANK EMBC 2 14.0 14.0 15.1 --- --- 15.1 ---

EXTEND MAXIMUM

CYCLE TIME

WDT 2 15.0 15.0 19.7 23.6 22.0 19.7 ---

SAVE CONDITION

FLAGS

CCS 1 8.6 8.6 12.5 14.2 12.9 --- ---

LOAD CONDITION

FLAGS

CCL 1 9.8 9.8 13.9 16.3 15.7 --- ---

CONVERT

ADDRESS FROM CV

FRMCV 3 13.6 13.6 19.9 23.1 31.8 --- ---

CONVERT

ADDRESS TO CV

TOCV 3 to 4 11.9 11.9 17.2 22.5 31.4 --- ---

DISABLE PERIPH-

ERAL SERVICING

IOSP 1 13.9 13.9 19.8 21.5 21.5 --- ---

ENABLE PERIPH-

ERAL SERVICING

IORS 1 63.6 63.6 92.3 22.2 22.2 --- ---

Instruction Mne-

monic

Length

(steps)

ON execution time (µs) Conditions

CJ1H

CPU6@

H-R

CJ1H

CPU6@

H

CJ1G

CPU4@

H

CJ1M

CPU12/

13/22/23

CJ1M

CPU11/

21

CJ1G

CPU4@

BLOCK PRO-

GRAM BEGIN

BPRG 2 12.1 12.1 13.0 27.5 30.4 13.0 ---

BLOCK PRO-

GRAM END

BEND 1 9.6 9.6 12.3 23.2 27.1 13.1 ---

BLOCK PRO-

GRAM PAUSE

BPPS 2 10.6 10.6 12.3 16.0 21.7 14.9 ---

BLOCK PRO-

GRAM

RESTART

BPRS 2 5.1 5.1 5.6 9.0 10.2 8.3 ---

CONDITIONAL

BLOCK EXIT

(Execu-

tion condi-

tion) EXIT

1 10.0 10.0 11.3 23.8 26.0 12.9 Block exited (input

condition ON)

4.0 4.0 4.9 7.2 8.4 7.3 Block not exited

(input condition

OFF)

CONDITIONAL

BLOCK EXIT

EXIT (bit

address)

2 9.8 9.8 13.5 28.4 30.6 16.3 Block exited (bit

ON)

4.7 4.7 7.2 11.4 13.1 10.7 Block not exited

(bit OFF)

CONDITIONAL

BLOCK EXIT

(NOT)

EXIT NOT

(bit

address)

2 12.4 12.4 14.0 28.4 31.2 16.8 Block exited (bit

OFF)

7.1 7.1 7.6 11.8 13.5 11.2 Block not exited

(bit ON)

Branching IF (execu-

tion condi-

tion)

1 4.6 4.6 4.8 6.8 8.5 7.2 IF true (input con-

dition ON)

6.7 6.7 7.3 12.2 13.9 10.9 IF false (input con-

dition OFF)

Branching IF (bit

address)

2 6.8 6.8 7.2 11.0 12.7 10.4 IF true (bit ON)

9.0 9.0 9.6 16.5 18.5 14.2 IF false (bit OFF)

Branching

(NOT)

IF NOT

(bit

address)

2 7.1 7.1 7.6 11.5 13.1 10.9 IF true (bit OFF)

9.2 9.2 10.1 16.8 18.9 14.7 IF false (bit ON)

Loading...

Loading...