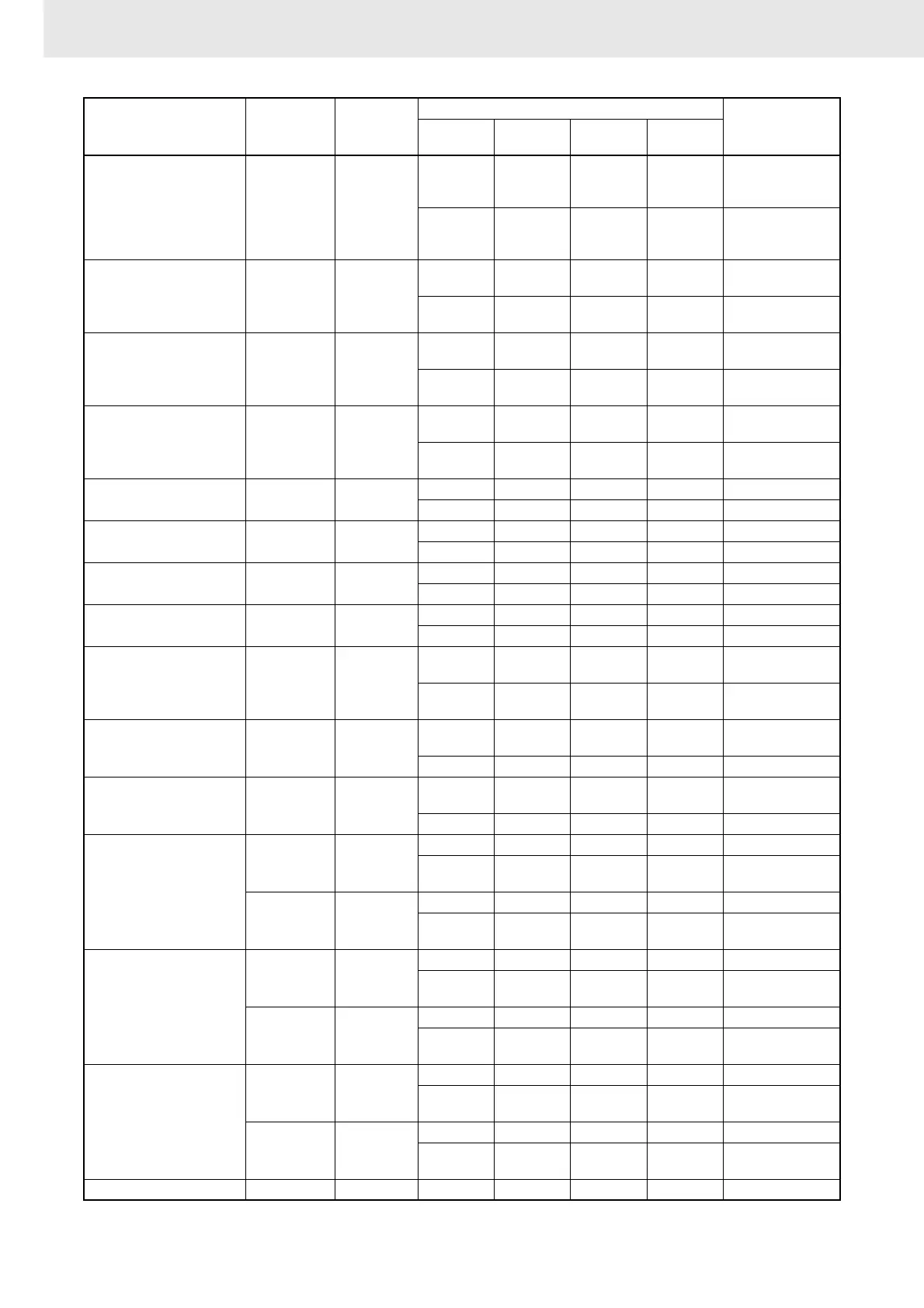

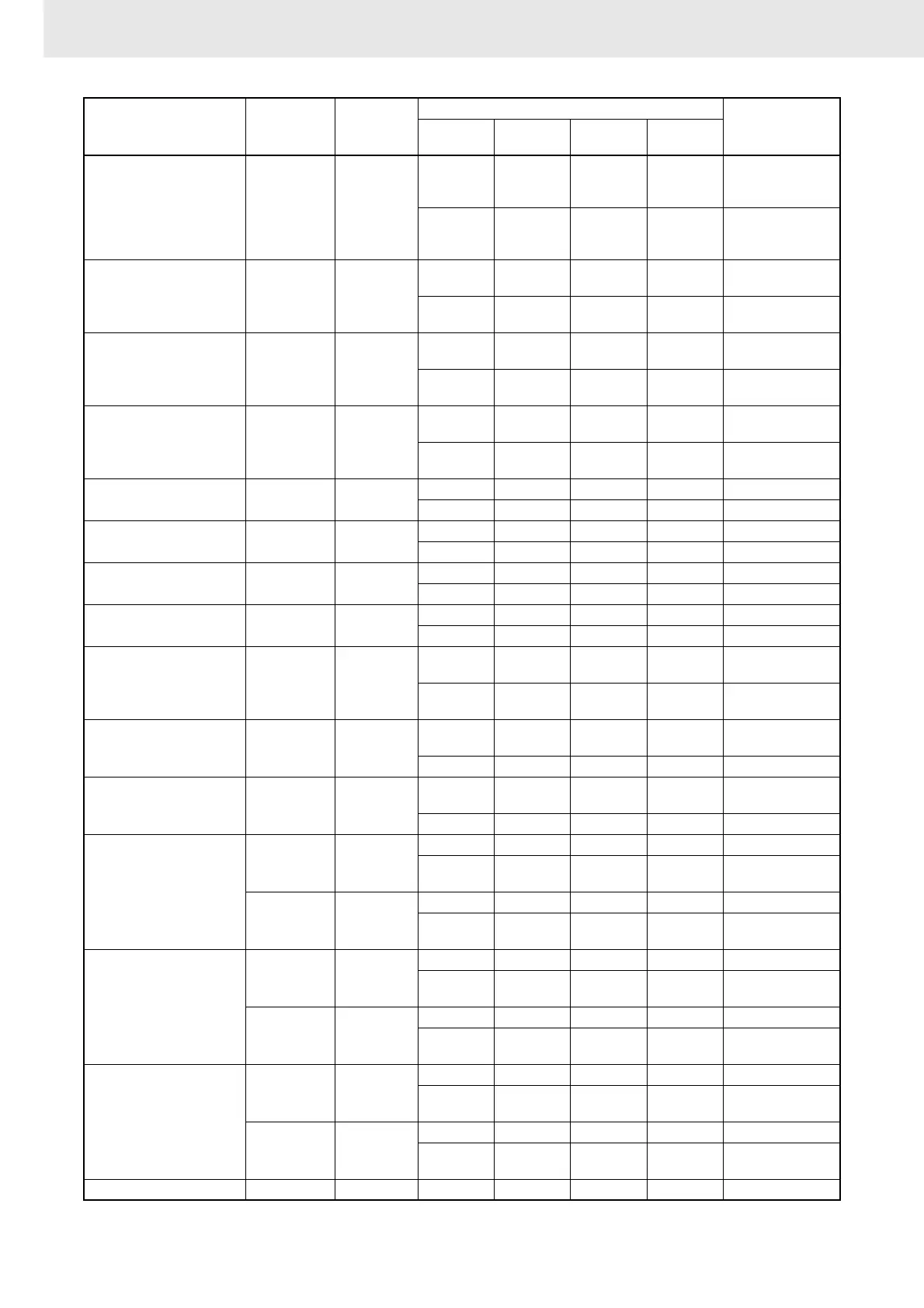

1218

CS/CJ/NSJ Series Instructions Reference Manual (W474)

4. Instruction Execution Times and Number of Steps

CONDITIONAL BLOCK

EXIT

(Execution

condition)

EXIT

1 10.0 11.3 12.9 12.9 Block exited

(input condition

ON)

4.0 4.9 7.3 7.3 Block not exited

(input condition

OFF)

CONDITIONAL BLOCK

EXIT

EXIT (bit

address)

2 6.8 13.5 16.3 16.3 Block exited (bit

ON)

4.7 7.2 10.7 10.7 Block not exited

(bit OFF)

CONDITIONAL BLOCK

EXIT (NOT)

EXIT NOT

(bit address)

2 12.4 14.0 16.8 16.8 Block exited (bit

OFF)

7.1 7.6 11.2 11.2 Block not exited

(bit ON)

Branching IF (execution

condition)

1 4.6 4.8 7.2 7.2 IF true (input

condition ON)

6.7 7.3 10.9 10.9 IF false (input

condition OFF)

Branching IF (bit

address)

2 6.8 7.2 10.4 10.4 IF true (bit ON)

9.0 9.6 14.2 14.2 IF false (bit OFF)

Branching (NOT) IF NOT (bit

address)

2 7.1 7.6 10.9 10.9 IF true (bit OFF)

9.2 10.1 14.7 14.7 IF false (bit ON)

Branching ELSE 1 6.2 6.7 9.9 9.9 IF true

6.8 7.7 11.2 11.2 IF false

Branching IEND 1 6.9 7.7 11.0 11.0 IF true

4.4 4.6 7.0 7.0 IF false

ONE CYCLE AND WAIT WAIT (exe-

cution condi-

tion)

1 12.6 13.7 16.7 16.7 Do not wait (input

condition ON)

3.9 4.1 6.3 6.3 Wait (input condi-

tion OFF)

ONE CYCLE AND WAIT WAIT (bit

address)

2 12.0 13.4 16.5 16.5 Do not wait (bit

ON)

6.1 6.5 9.6 9.6 Wait (bit OFF)

ONE CYCLE AND WAIT

(NOT)

WAIT NOT

(bit address)

2 12.2 13.8 17.0 17.0 Do not wait (bit

OFF)

6.4 6.9 10.1 10.1 Wait (bit ON)

HUNDRED-MS TIMER

WAIT

TIMW 3 22.3 25.2 33.1 33.1 Default setting

24.9 27.8 35.7 35.7 Normal execu-

tion

TIMWX 3 22.3 25.2 33.1 33.1 Default setting

24.9 27.8 35.7 35.7 Normal execu-

tion

TEN-MS TIMER WAIT TMHW 3 25.8 27.9 34.1 34.1 Default setting

20.6 22.7 28.9 28.9 Normal execu-

tion

TMHWX 3 25.8 27.9 34.1 34.1 Default setting

20.6 22.7 28.9 28.9 Normal execu-

tion

COUNTER WAIT CNTW 4 17.9 22.6 27.4 27.4 Default setting

19.1 23.9 28.7 28.7 Normal execu-

tion

CNTWX 4 17.9 22.6 27.4 27.4 Default setting

19.1 23.9 28.7 28.7 Normal execu-

tion

Loop Control LOOP 1 7.9 9.1 12.3 12.3 ---

Instruction Mnemonic Length

(steps)

ON execution time (µs) Conditions

CS1H

CPU6@H

CS1G

CPU4@H

CS1H

CPU6@

CS1G

CPU4@

Loading...

Loading...