94

Sequence Input Instructions Section 3-2

Operand Specifications

Description AND is used for a normally open bit connected in series. AND cannot be

directly connected to the bus bar, and cannot be used at the beginning of a

logic block. If there is no immediate refreshing specification, the specified bit

in I/O memory is read. If there is an immediate refreshing specification, the

status of the CPU Unit’s input terminal is read.

Flags There are no flags affected by this instruction.

Precautions Differentiate up (@) or differentiate down (%) can be specified for AND. If dif-

ferentiate up (@) is specified, the execution condition is turned ON for one

cycle only after the status of the operand bit goes from OFF to ON. If differen-

tiate down (%) is specified, the execution condition is turned ON for one cycle

only after the status of the operand bit goes from ON to OFF.

Immediate refreshing (!) can be specified for AND. An immediate refresh

instruction updates the status of the input bit for CPU Unit built-in inputs just

before the instruction is executed.

For AND, it is possible to combine immediate refreshing and up or down differ-

entiation (!@ or !%). If either of these is specified, the input is refreshed from

the CPU Unit just before the instruction is executed and the execution condi-

tion is turned ON for one cycle only after the status goes from OFF to ON, or

from ON to OFF.

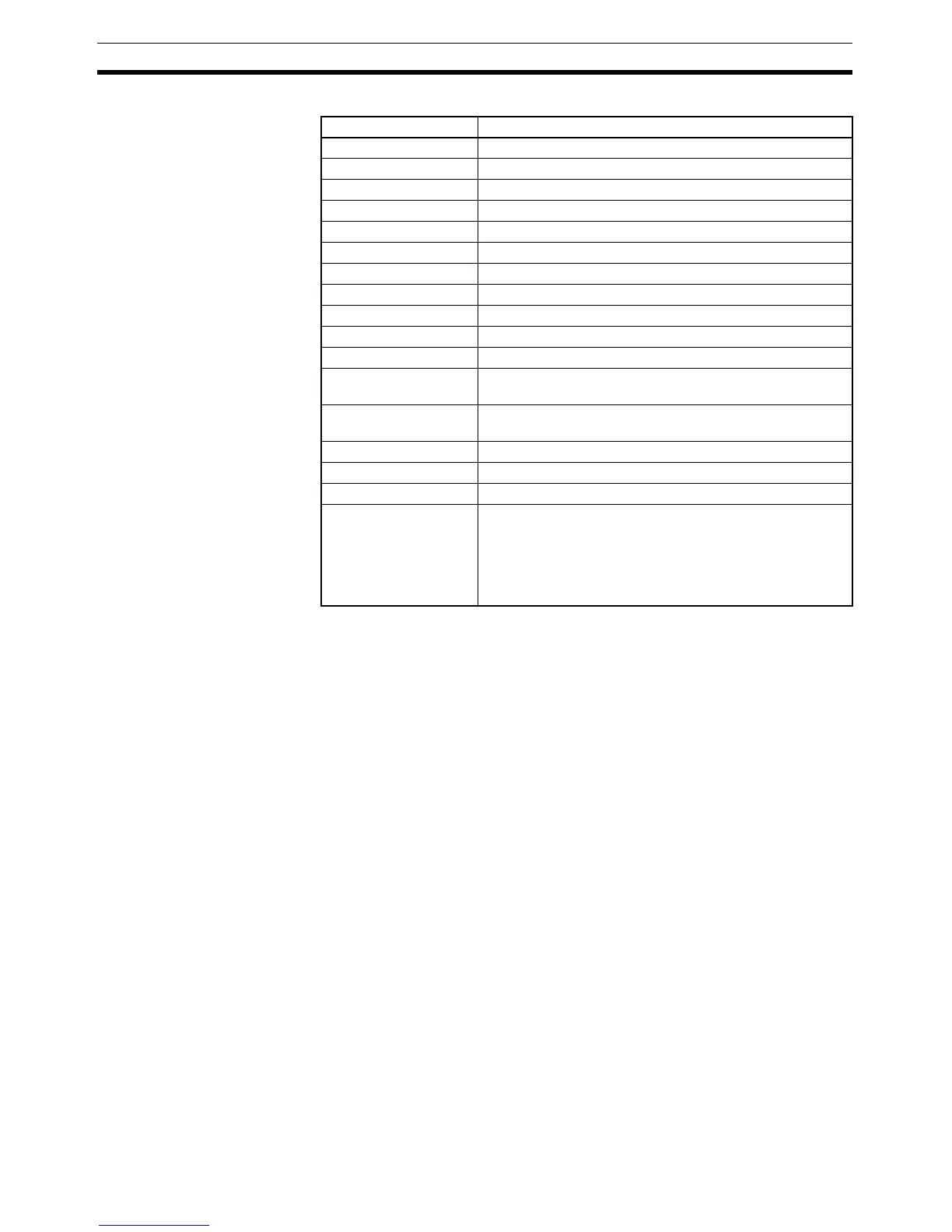

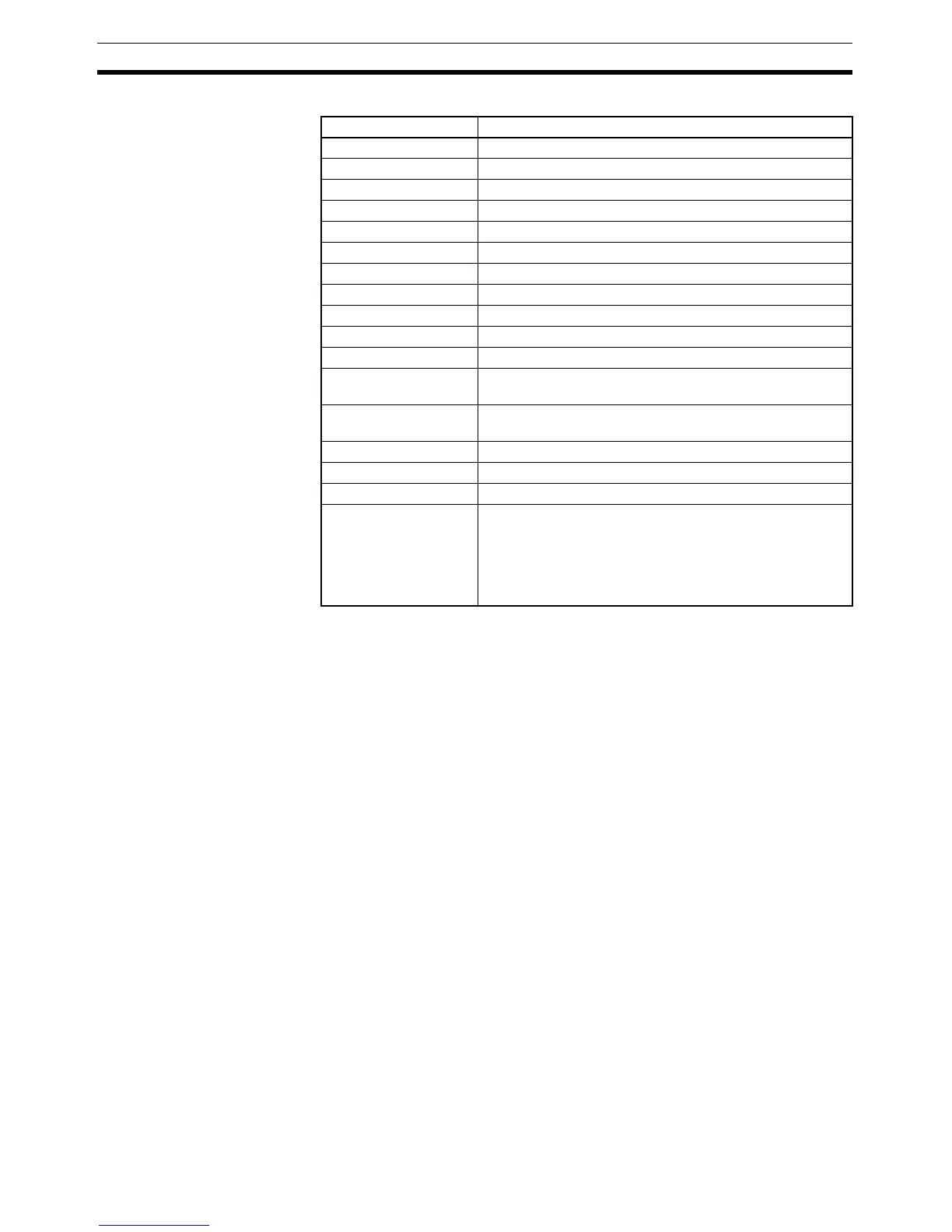

Area AND bit operand

CIO Area CIO 0.00 to CIO 6143.15

Work Area W0.00 to W511.15

Holding Bit Area H0.00 to H511.15

Auxiliary Bit Area A0.00 to A959.15

Timer Area T0000 to T4095

Counter Area C0000 to C4095

Task Flag Area TK00 to TK31

Condition Flags ER, CY, N, OF, UF, >, =, <, >=, <>, <=, ON, OFF, AER

Clock Pulses 0.02 s, 0.1 s, 0.2 s, 1 s, 1 min

TR Area ---

DM Area ---

Indirect DM addresses

in binary

---

Indirect DM addresses

in BCD

---

Constants ---

Data Registers ---

Index Registers ---

Indirect addressing

using Index Registers

,IR0 to ,IR15

–2048 to +2047 ,IR0 to –2048 to +2047 ,IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –)IR0 to, –(– –)IR15

Loading...

Loading...