700

Interrupt Control Instructions Section 3-19

Scheduled Interrupts

N specifies the scheduled interrupt number and S specifies the time to the first

scheduled interrupt.

High-speed Counter Interrupts

N specifies the high-speed counter interrupt number and S specifies the oper-

ation

Operand Specifications

Description Depending on the value of N, CLI(691) either clears the specified recorded

input interrupts or high-speed counter interrupts, or sets the time before exe-

cution of the first scheduled interrupt.

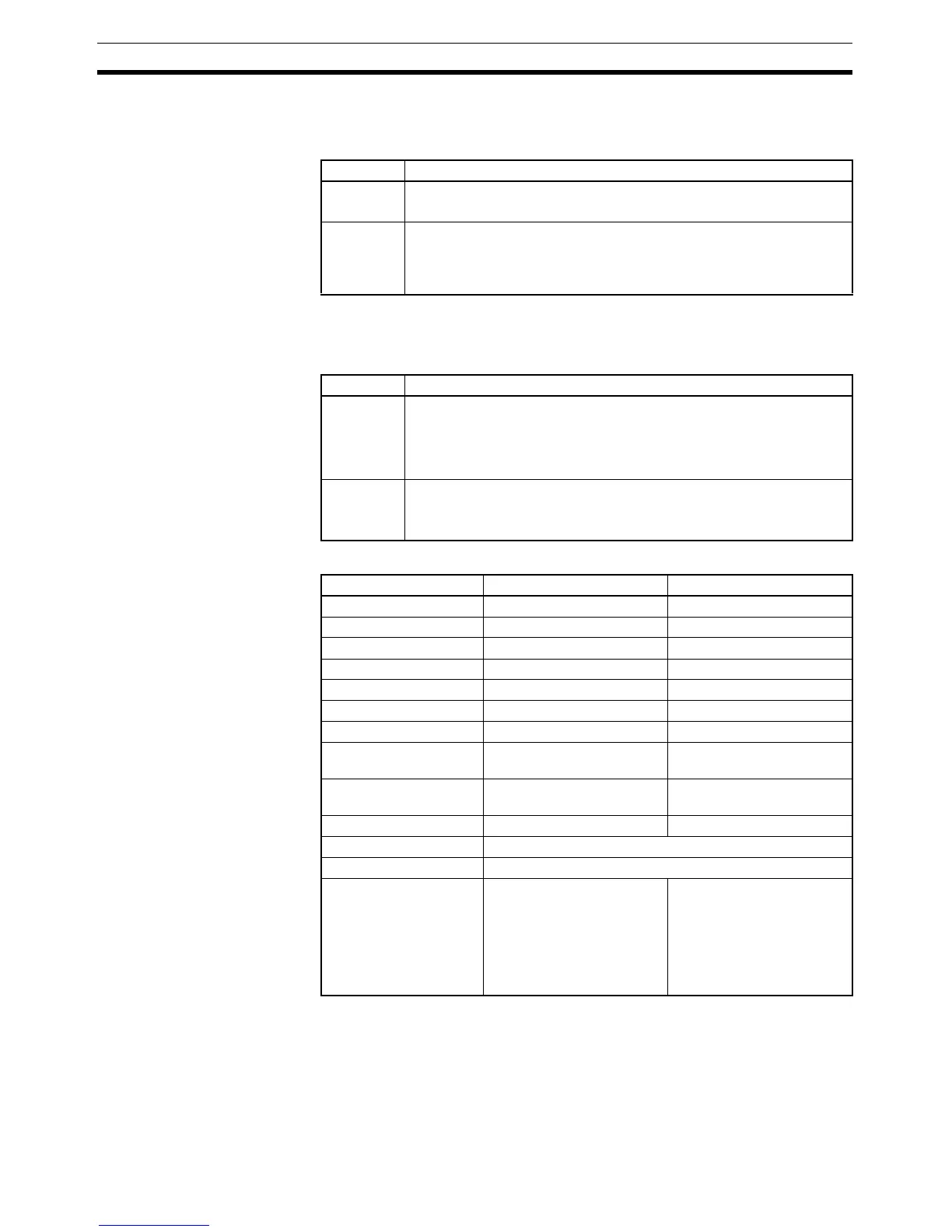

Operand Contents

N Specify the scheduled interrupt number.

4: Scheduled interrupt 0 (interrupt task 2)

S 0000 to 270F hex:

Time to first scheduled interrupt (0 to 9999)

Note The unit for the scheduled interrupt interval can be set to 10 ms,

1.0 ms, or 0.1 ms in the PLC Setup interrupt settings.

Operand Contents

N High-speed Counter Interrupt Number

10: High-speed counter input 0

11: High-speed counter input 1

12: High-speed counter input 2

13: High-speed counter input 3

S Recorded Interrupt Clear Specification

0000 hex: Recorded interrupt retained

0001 hex: Recorded interrupt cleared

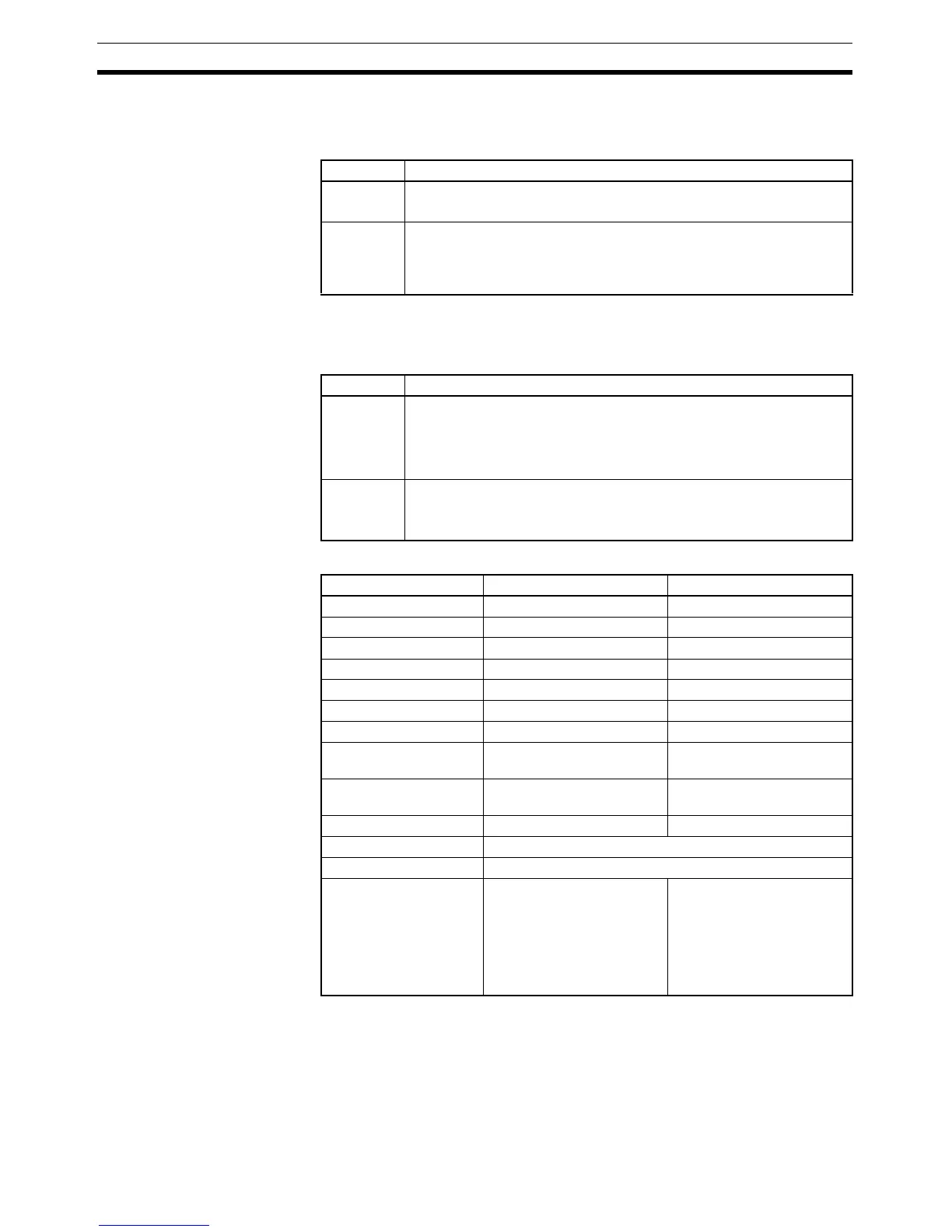

Area N S

CIO Area --- CIO 0 to CIO 6143

Work Area --- W0 to W511

Holding Bit Area --- H0 to H511

Auxiliary Bit Area --- A0 to A959

Timer Area --- T0000 to T4095

Counter Area --- C0000 to C4095

DM Area --- D0 to D32767

Indirect DM addresses

in binary

--- @ D0 to @ D32767

Indirect DM addresses

in BCD

--- *D0 to *D32767

Constants --- DR0 to DR15

Data Registers Specified values only

Index Registers ---

Indirect addressing

using Index Registers

--- ,IR0 to ,IR15

–2048 to +2047, IR0 to

–2048 to +2047, IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –) IR0 to, –(– –) IR15

Loading...

Loading...