201

Timer and Counter Instructions Section 3-5

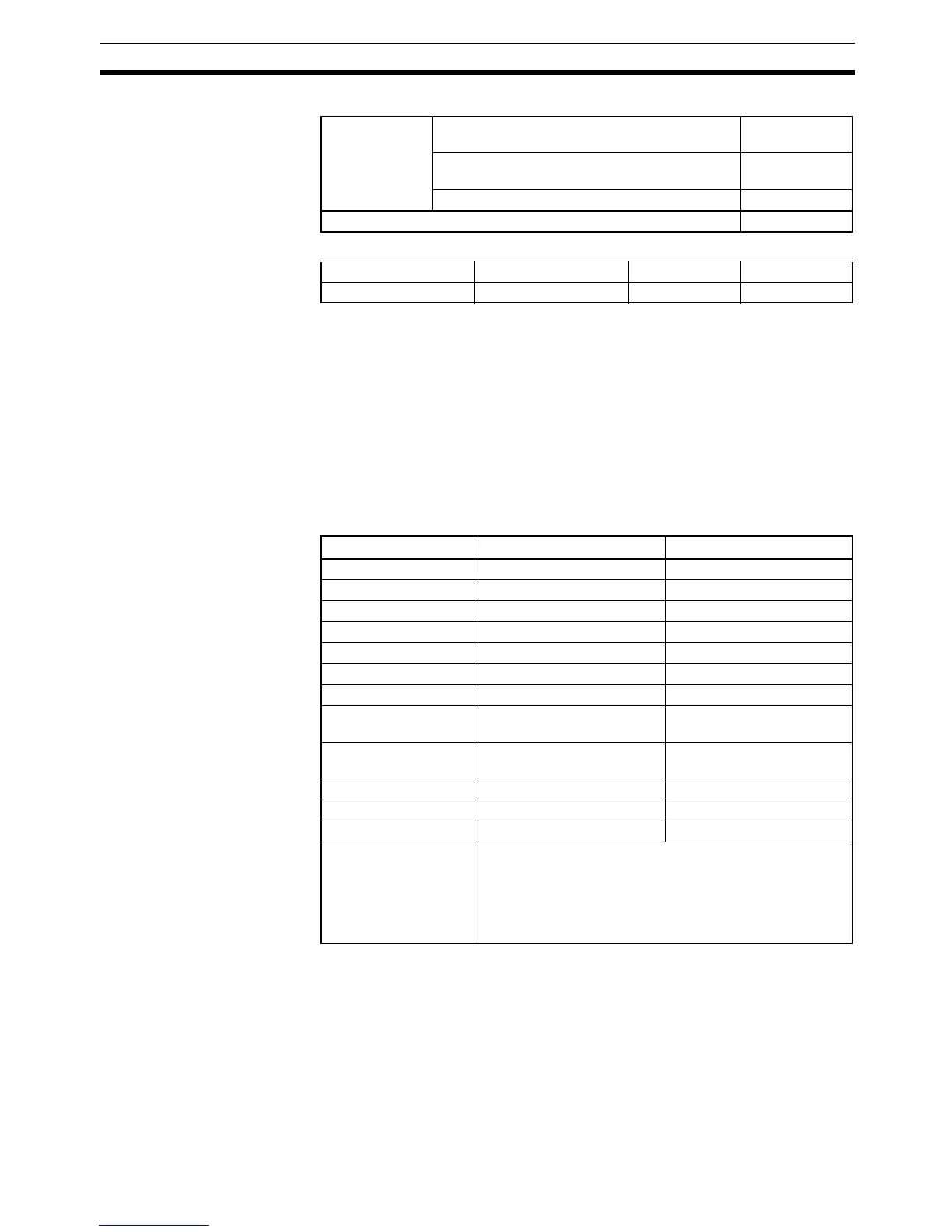

Variations

Applicable Program Areas

Operands N

1

: First Number in Range

N

1

must be a timer number between T0000 and T4095 or a counter number

between C0000 and C4095.

N

2

: Last Number in Range

N

2

must be a timer number between T0000 and T4095 or a counter number

between C0000 and C4095.

Note N

1

and N

2

must be in the same data area, i.e., N

1

and N

2

must be timer num-

bers or counter numbers.

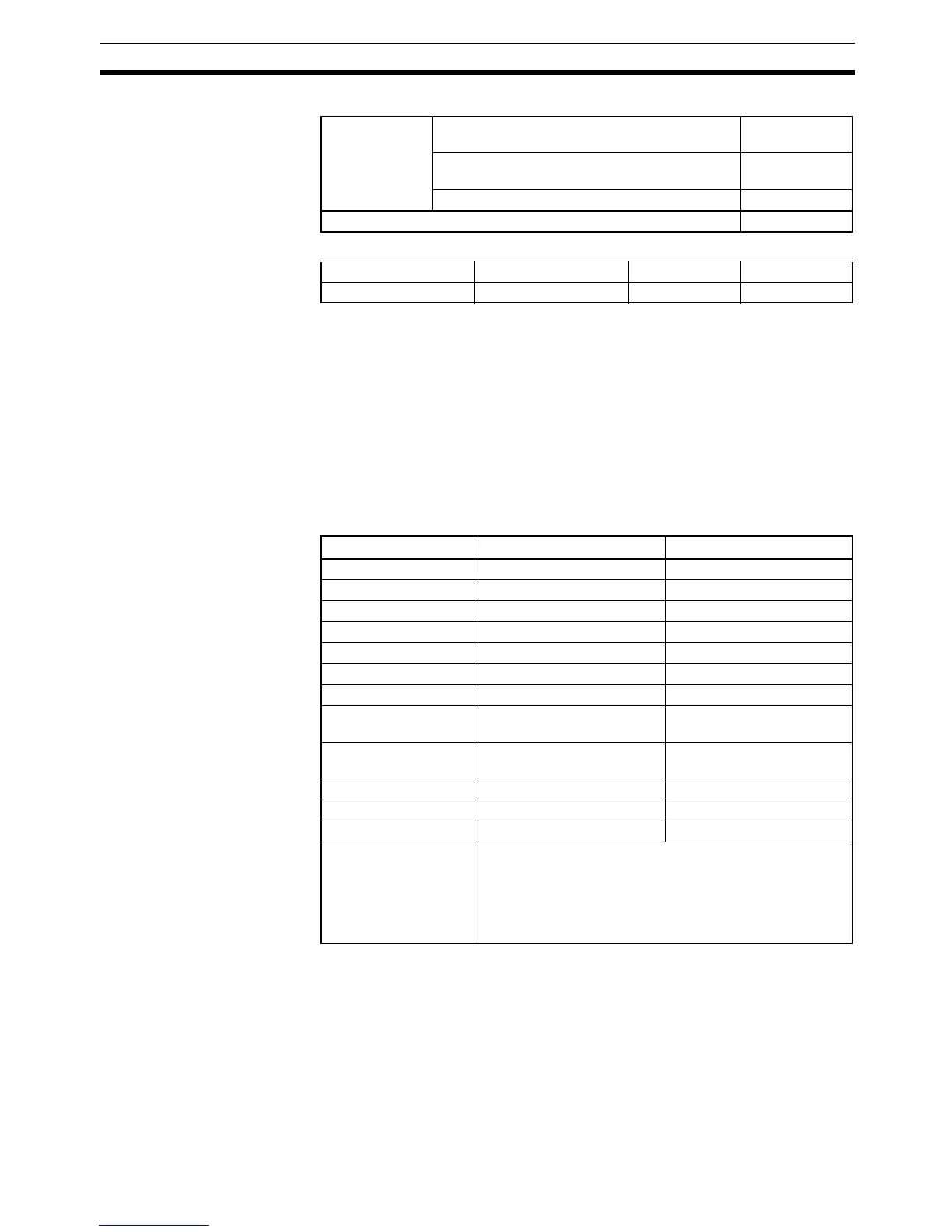

Operand Specifications

Description CNR(545)/CNRX(547) resets the Completion Flags of all timers or counters

from N

1

to N

2

. At the same time, the PVs will all be set to the maximum value

(9999 for BCD and FFFF for binary). (The PV will be set to the SV the next

time that the timer or counter instruction is executed.)

Variations Executed Each Cycle for ON Condition CNR(545)/

CNRX(547)

Executed Once for Upward Differentiation @CNR(545)/

CNRX(547)

Executed Once for Downward Differentiation Not supported.

Immediate Refreshing Specification Not supported.

Block program areas Step program areas Subroutines Interrupt tasks

OK OK OK OK

Area N

1

N

2

CIO Area --- ---

Work Area --- ---

Holding Bit Area --- ---

Auxiliary Bit Area --- ---

Timer Area C0000 to C4095 C0000 to C4095

Counter Area T0000 to T4095 T0000 to T4095

DM Area --- ---

Indirect DM addresses

in binary

--- ---

Indirect DM addresses

in BCD

--- ---

Constants --- ---

Data Registers --- ---

Index Registers --- ---

Indirect addressing

using Index Registers

,IR0 to ,IR15

–2048 to +2047 ,IR0 to –2048 to +2047 ,IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –)IR0 to, –(– –)IR15

Loading...

Loading...