271

Data Movement Instructions Section 3-7

Variations

Applicable Program Areas

Operands D: Destination

The destination must be an Index Register (IR0 to IR15).

Operand Specifications

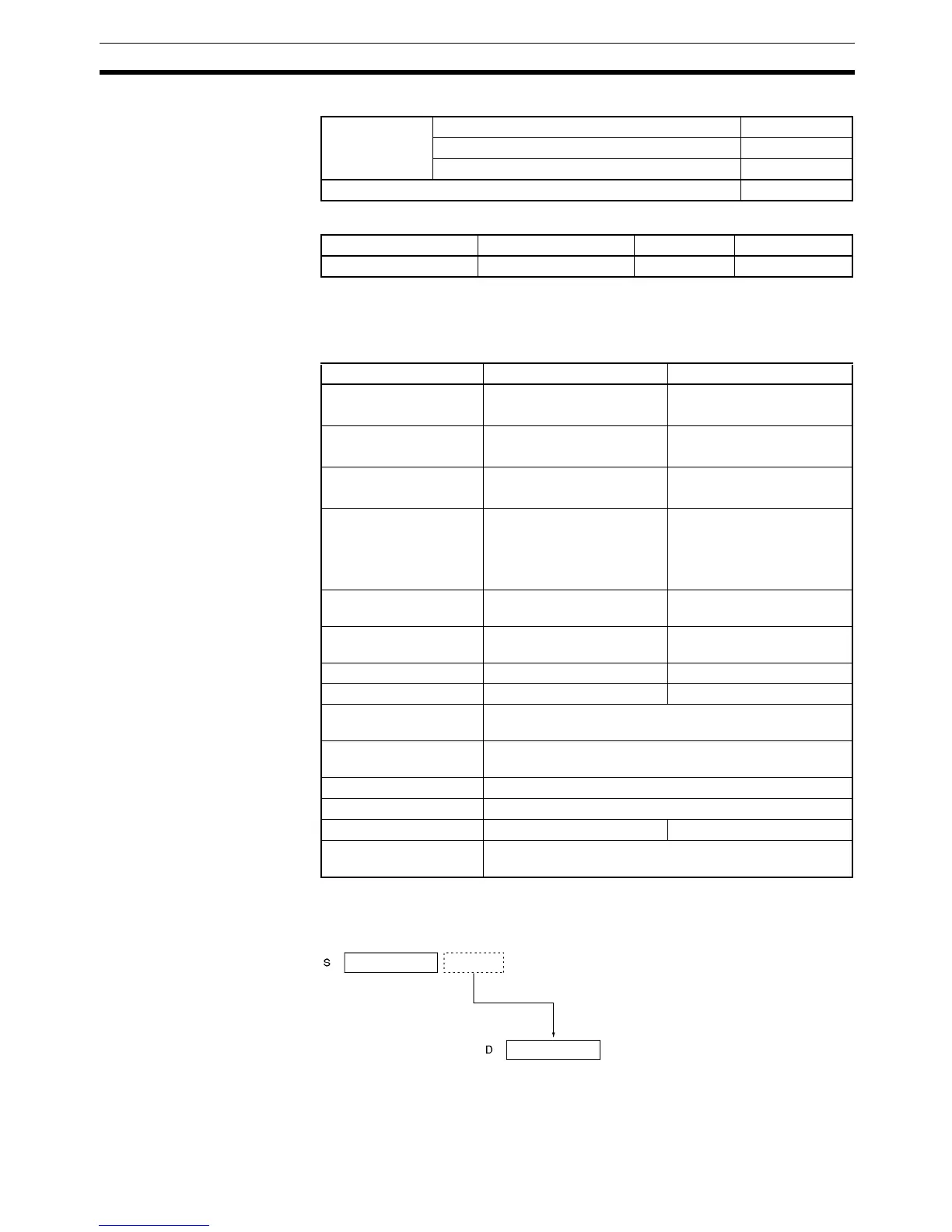

Description MOVR(560) finds the PLC memory address (absolute address) of S and

writes that address in D (an Index Register).

If a timer or counter is specified in S, MOVR(560) will write the PLC memory

address of the timer/counter Completion Flag in D. Use MOVRW(561) to write

the PLC memory address of the timer/counter PV in D.

Variations Executed Each Cycle for ON Condition MOVR(560)

Executed Once for Upward Differentiation @MOVR(560)

Executed Once for Downward Differentiation Not supported

Immediate Refreshing Specification Not supported

Block program areas Step program areas Subroutines Interrupt tasks

OK OK OK OK

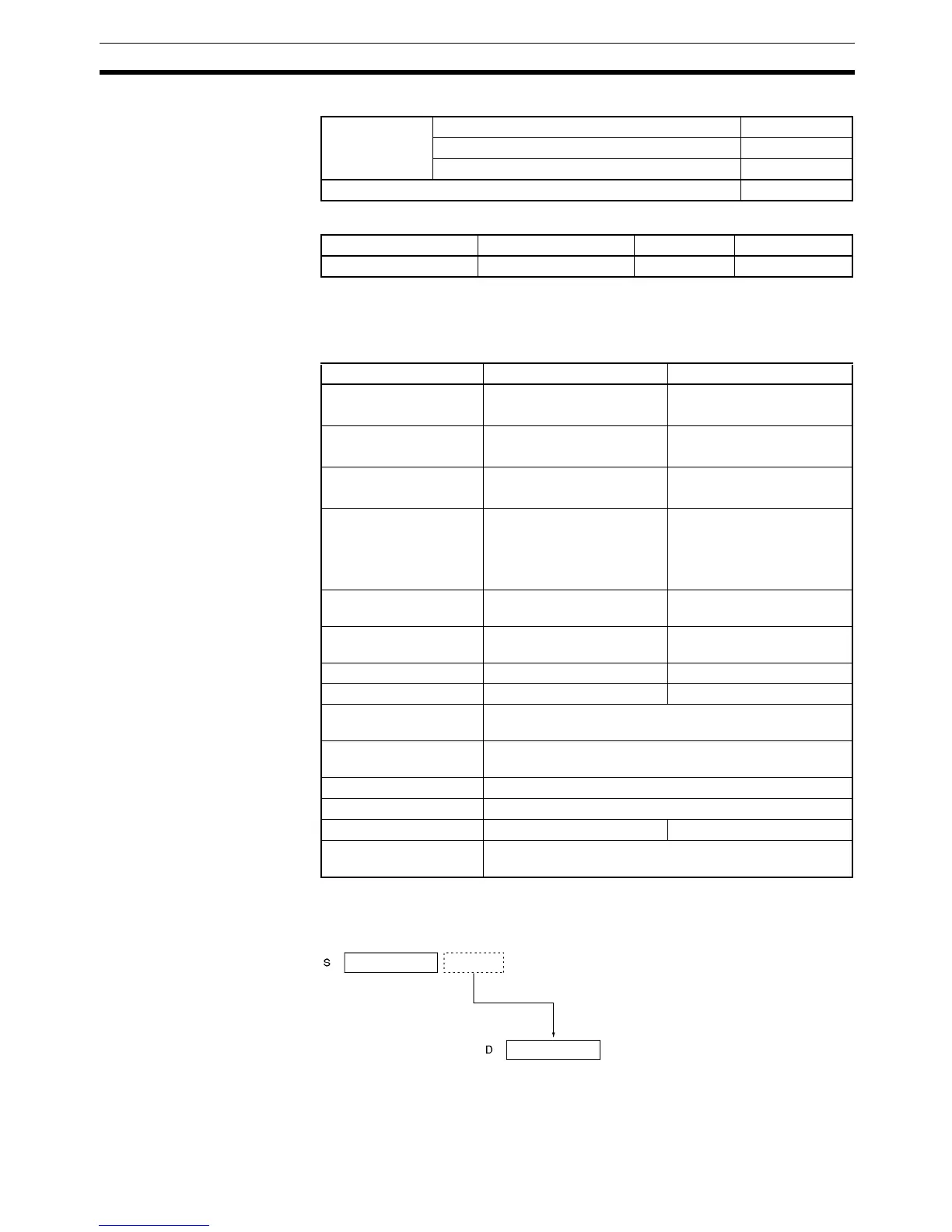

Area S D

CIO Area CIO 0 to CIO 6143

CIO 0.00 to CIO 6143.15

---

Work Area W0 to W511

W0.00 to W511.15

---

Holding Bit Area H0 to H511

H0.00 to H511.15

---

Auxiliary Bit Area A0 to A447

A448 to A959

A0.00 to A447.15

A448.00 to A959.15

---

Timer Area T0000 to T4095

(Completion Flag)

---

Counter Area C0000 to C4095

(Completion Flag)

---

Task Flag TK00 to TK31 ---

DM Area D0 to D32767 ---

Indirect DM addresses

in binary

---

Indirect DM addresses

in BCD

---

Constants ---

Data Registers ---

Index Registers --- IR0 to IR15

Indirect addressing

using Index Registers

---

Internal I/O memory address of S

Index Register

Loading...

Loading...