441

Logic Instructions Section 3-12

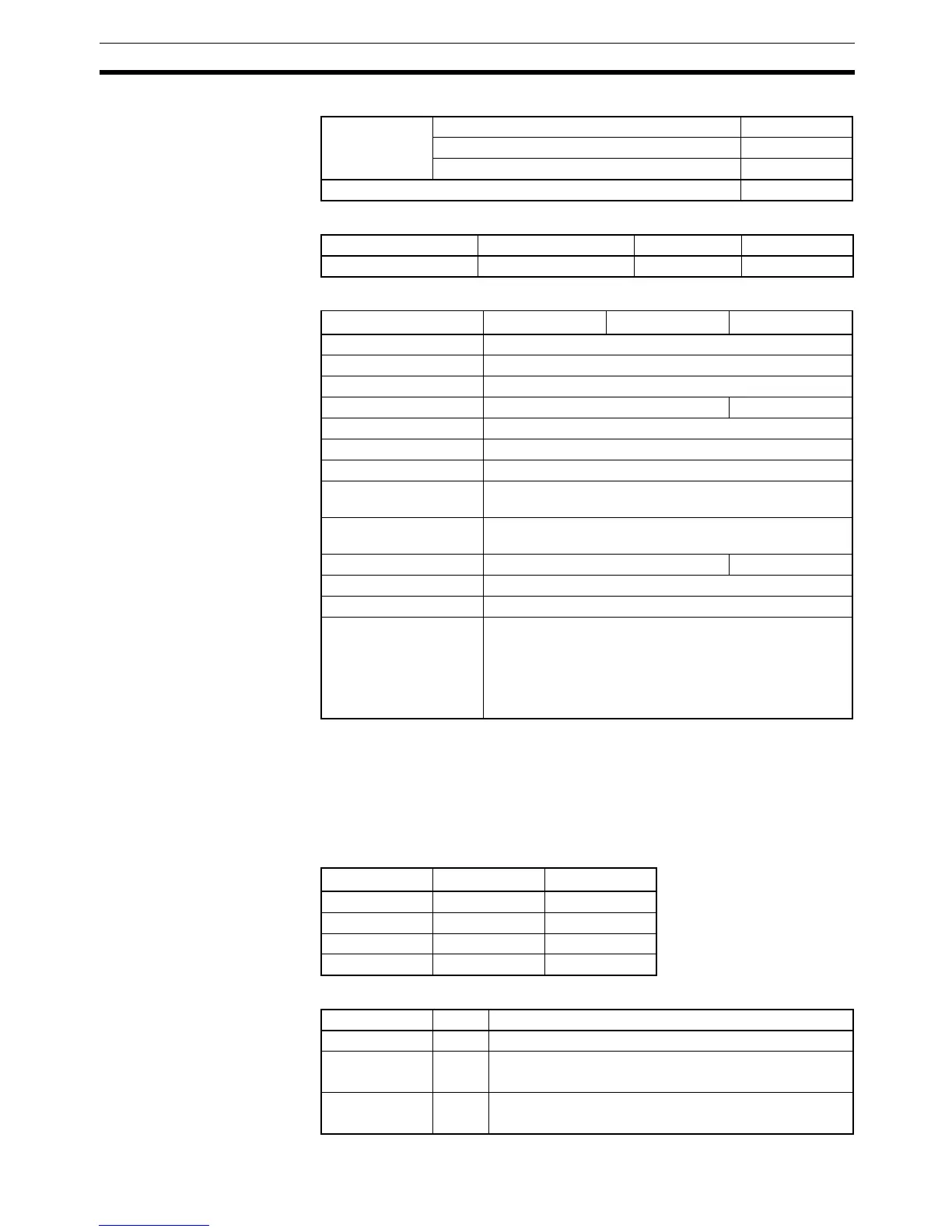

Variations

Applicable Program Areas

Operand Specifications

Description ORWL(611) takes the logical OR of data specified in I

1

and I

2

as double-word

data and outputs the result to R, R+1.

• When any of the corresponding bits in I

1,

I

1

+1, I

2,

and

I

2

+1are 1, a 1 will

be output to the corresponding bit it R+1. When any of them are 0, a 0 will

be output to the corresponding bit in R+1.

(I

1,

I

1

+1) + (I

2,

I

2

+1)

→ (R, R+1)

Flags

Variations Executed Each Cycle for ON Condition ORWL(611)

Executed Once for Upward Differentiation @ORWL(611)

Executed Once for Downward Differentiation Not supported.

Immediate Refreshing Specification Not supported.

Block program areas Step program areas Subroutines Interrupt tasks

OK OK OK OK

Area I

1

I

2

R

CIO Area CIO 0 to CIO 6142

Work Area W0 to W510

Holding Bit Area H0 to H510

Auxiliary Bit Area A0 to A958 A448 to A958

Timer Area T0000 to T4094

Counter Area C0000 to C4094

DM Area D0 to D32766

Indirect DM addresses

in binary

@ D0 to @ D32767

Indirect DM addresses

in BCD

*D0 to *D32767

Constants #00000000 to #FFFFFFFF (binary) ---

Data Registers ---

Index Registers ---

Indirect addressing

using Index Registers

,IR0 to ,IR15

–2048 to +2047 ,IR0 to –2048 to +2047 ,IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –)IR0 to, –(– –)IR15

I

1,

I

1

+1 I

2,

I

2

+1 R, R+1

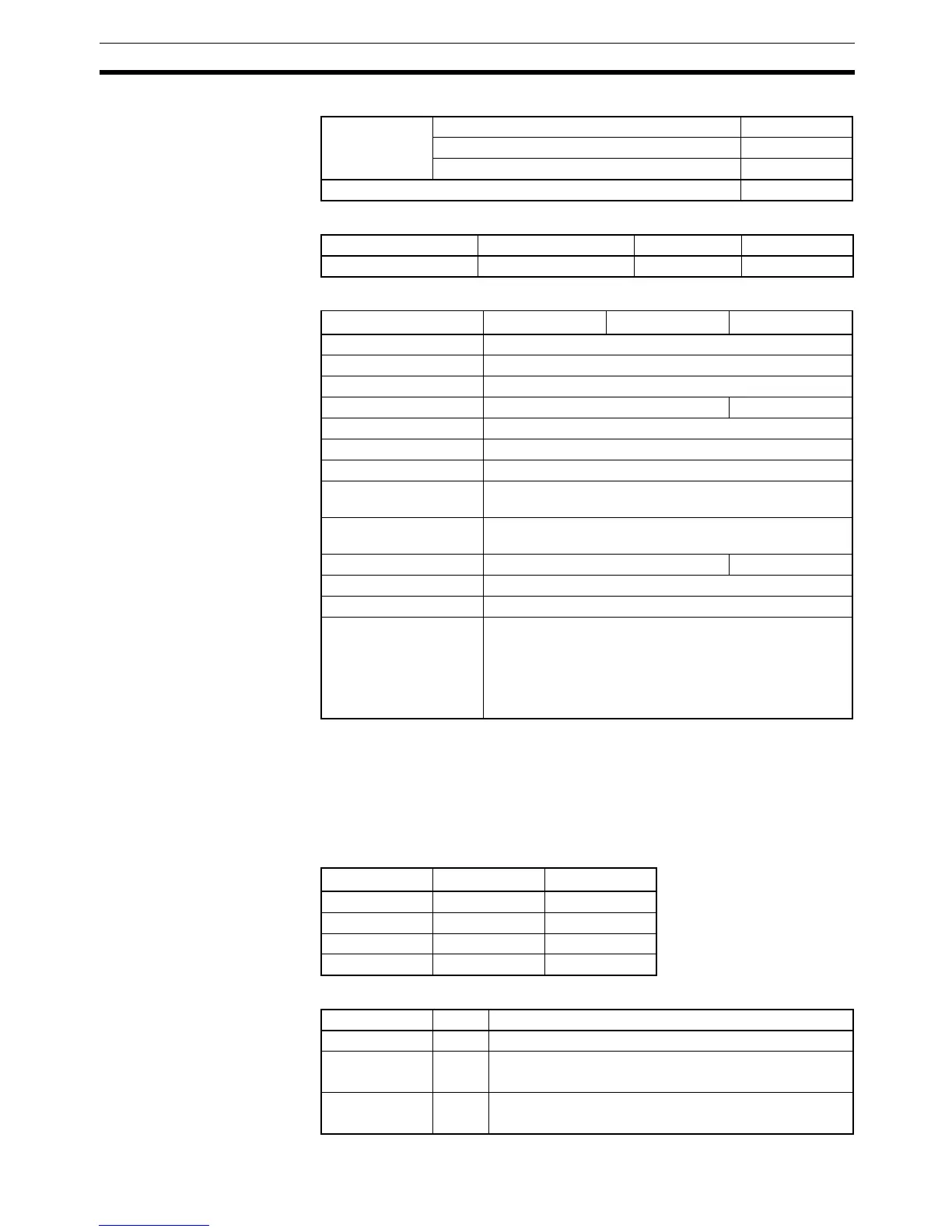

111

101

011

000

Name Label Operation

Error Flag ER OFF

Equals Flag = ON when the result is 0.

OFF in all other cases.

Negative Flag N ON when the leftmost bit of R is 1.

OFF in all other cases.

Loading...

Loading...