4-10

MAINTENANCE ORBAN MODEL 8685

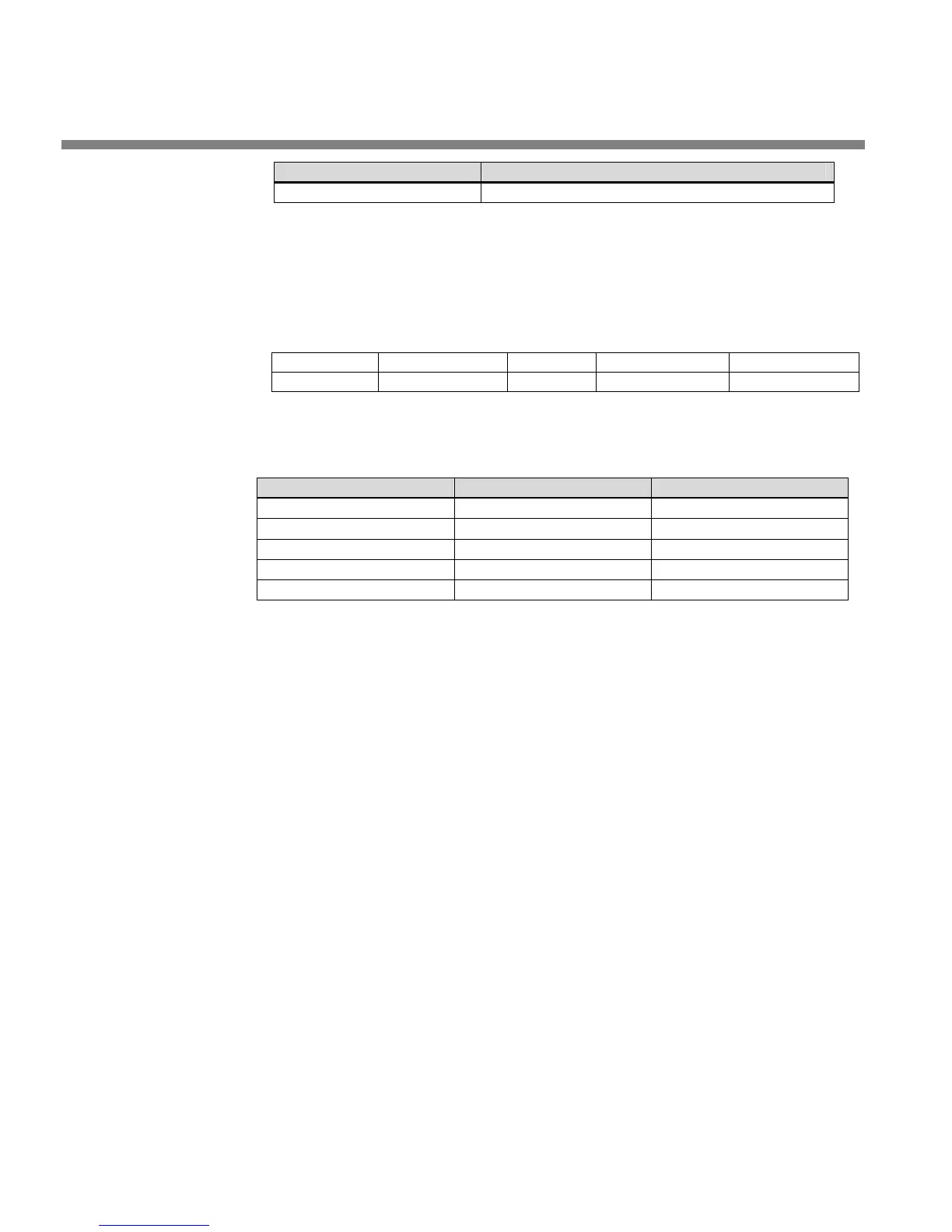

Number of Red Flashes Problem With

9 CPU +2.5V supply

Table 4-1: Decoder Chart for Power Supervisor

You can monitor power supply voltages at connector J7 on the power

supply board (see page 6-51 for the parts locator drawing and page 6-52

for

the schematic). When one faces the connector, the voltages can be

found on the pins in the following pattern:

(1) + unreg. (3) digital gnd (5) +15V (7) +5 V digital (9) –5V analog

(2) - unreg (4) chassis gnd (6) -15V (8) +5V analog (10) NC

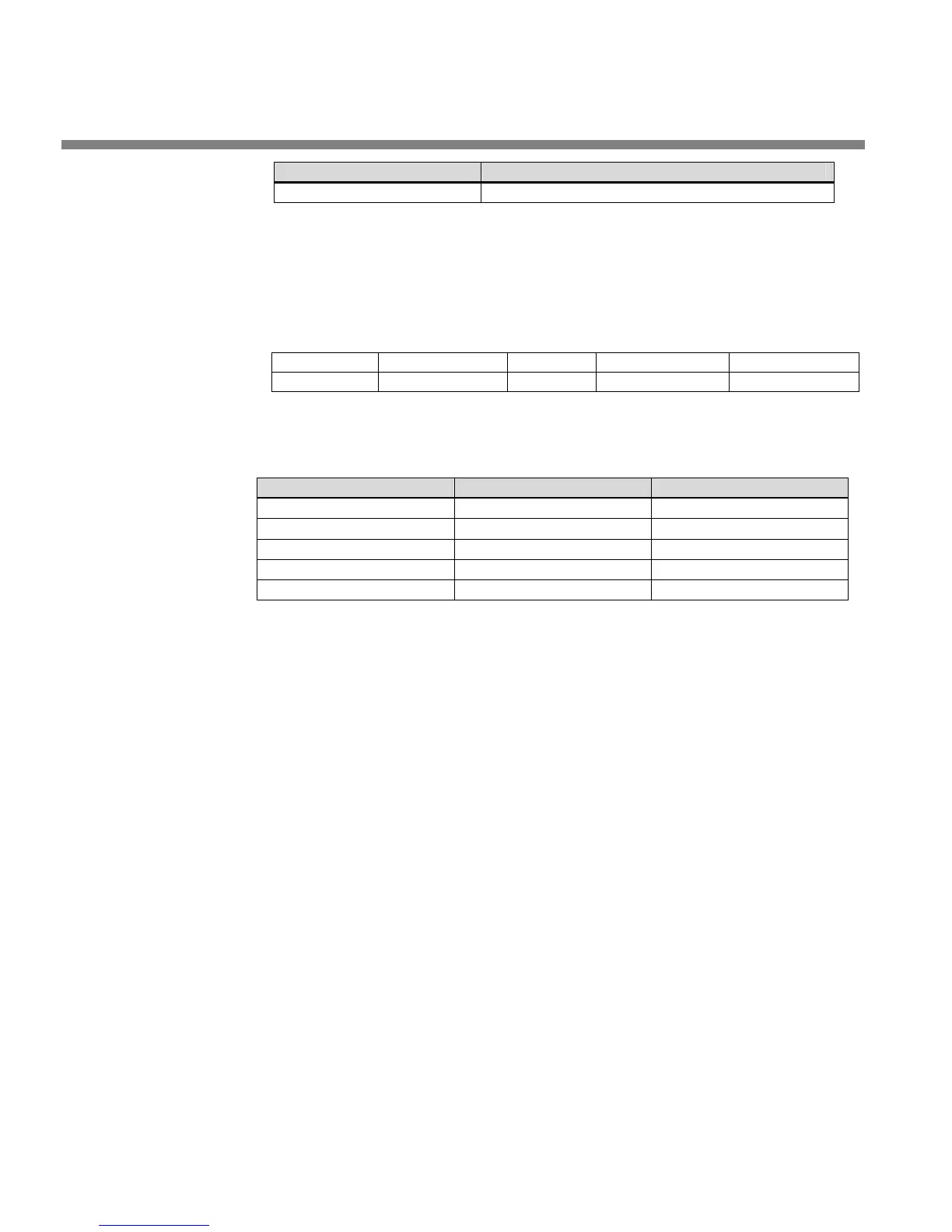

Table 4-2: Layout Diagram of J7, with expected voltages on each pin

C) Measure the regulated voltages at J7 with the DVM and observe the ripple

with an oscilloscope, AC-coupled. The following results are typical:

Power Supply Rail DC Voltage (volts) AC Ripple (mV p-p)

+15VDC

+15 ± 0.5

<20

–15VDC

–15 ± 0.5

<20

+5VDC

+5 ± 0.25

<20

–5VDC

–5 ± 0.25

<20

Digital +5VDC

+5 ± 0.25

[Obscured by noise]

Table 4-3: Typical Power Supply Voltages and AC Ripple

3. Adjust Analog Output Level Trim; Verify Analog Output THD and Noise.

A) L

OCATE to RECALL/IMPORT>RECALL SETUP>AUDIT1 and press the ENTER button.

This will recall the AUDIT1 Setup.

B) Connect the distortion analyzer to the left analog output.

C) Using the distortion analyzer’s level meter, adjust output trim VR200 to make

the meter indicate +10.0 dBu. (0 dBu = 0.775V rms.) Verify a frequency read-

ing of 400 Hz.

D) Verify a THD+N reading of <0.03% using a 22 kHz low pass filter in the distor-

tion analyzer.

E) Optional: L

OCATE to SYSTEM SETUP>TEST MODES>TONE FREQUENCY. Using the

distortion analyzer, measure the level and THD+N at 20 Hz, 50 Hz, 100 Hz, 400

Hz, 5 kHz, and 20 kHz. (Set the frequencies with the 8685’s knob.) Verify that

frequency response is within ±0.1 dB of the level at 400 Hz and that THD+N

does not exceed 0.03% at any of these frequencies.

F) Using VR201, repeat steps (B) through (E) for the right analog output.

G) Recall the A

UDIT2 Setup.

H) Verify a reading (noise) of <–80 dBu at the left and right analog outputs.

Loading...

Loading...