197

MEP-7000

5

6 7 8

5

6 7 8

A

B

C

D

E

F

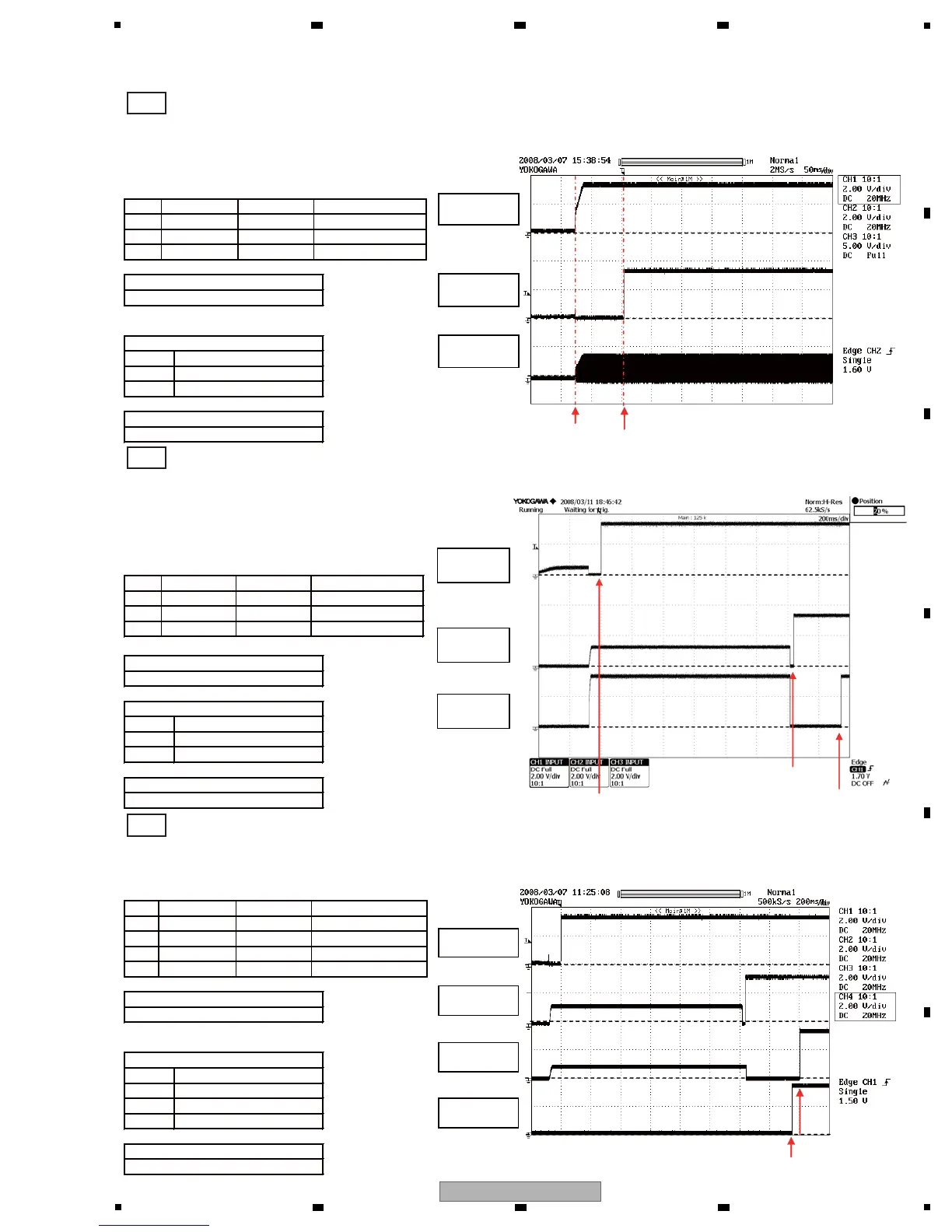

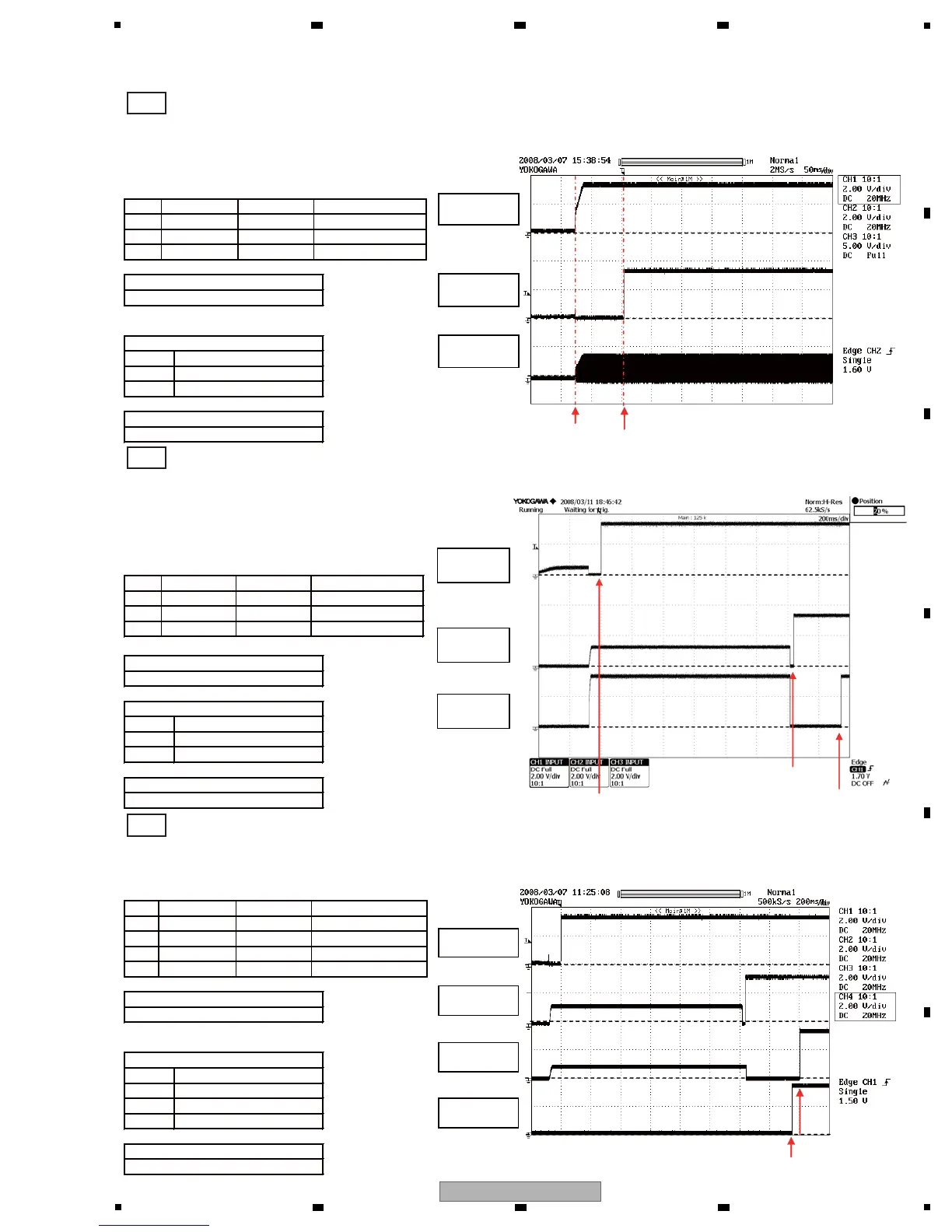

10.29 WAVEFORMS

[1] SMAIN: WAVEFORMS

SOUTH CPU RESET

CH1

CH2

CH3

a-b : 75ms

Devices that the South CPU resets

CH1

CH2

CH3

Devices that the AUDIO DSP resets - 1

CH1

CH2

CH3

CH4

Voltage

2.0V/div

Measurement conditions

At the time of power on

Measurement conditions

At the time of power on

200ms/div

2.0V/div

2.0V/div

2.0V/div

Time

200ms/div

2.0V/div

2.0V/div

2.0V/div

Voltage

Time

Measurement conditions

At the time of power on

Voltage

Time

50ms/div

2.0V/div

2.0V/div

5.0V/div

CH1

V+3R3D

CH2

RST#

a

b

CH3

100MHz

CH1

RST#

CH2

DSPRST#

CH3

FPGARST#

CH1

RST#

CH2

DSPRST#

CH3

USBRST#

CH4

DACRST#

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

South CPU Reset Clear

DAC Reset Clear

USB CONTROLLER

Reset Clear

South CPU Reset Clear

DSP Reset Clear

FPGA Reset Clear

Power On

Signal Name

No.(SCH/PCB)

Measurement Point

CH1 V+3R3D 1 V+3R3D (TP)

CH2 RST# 2 RST# (TP)

CH3 100MHz 3 R225

Signal Name

No.(SCH/PCB)

Measurement Point

CH1 RST# 2 RST# (TP)

CH2 DSPRST# 11 DSPRST# (TP)

CH3 FPGARST# 18 FPGARST# (TP)

Signal Name

No.(SCH/PCB)

Measurement Point

CH1 RST# 2 RST# (TP)

CH2 DSPRST# 11 DSPRST# (TP)

CH3 USBRST# 13 USBRSTv# (TP)

CH4 DACRST# 12 DACRST# (TP)

1

2

3

Loading...

Loading...