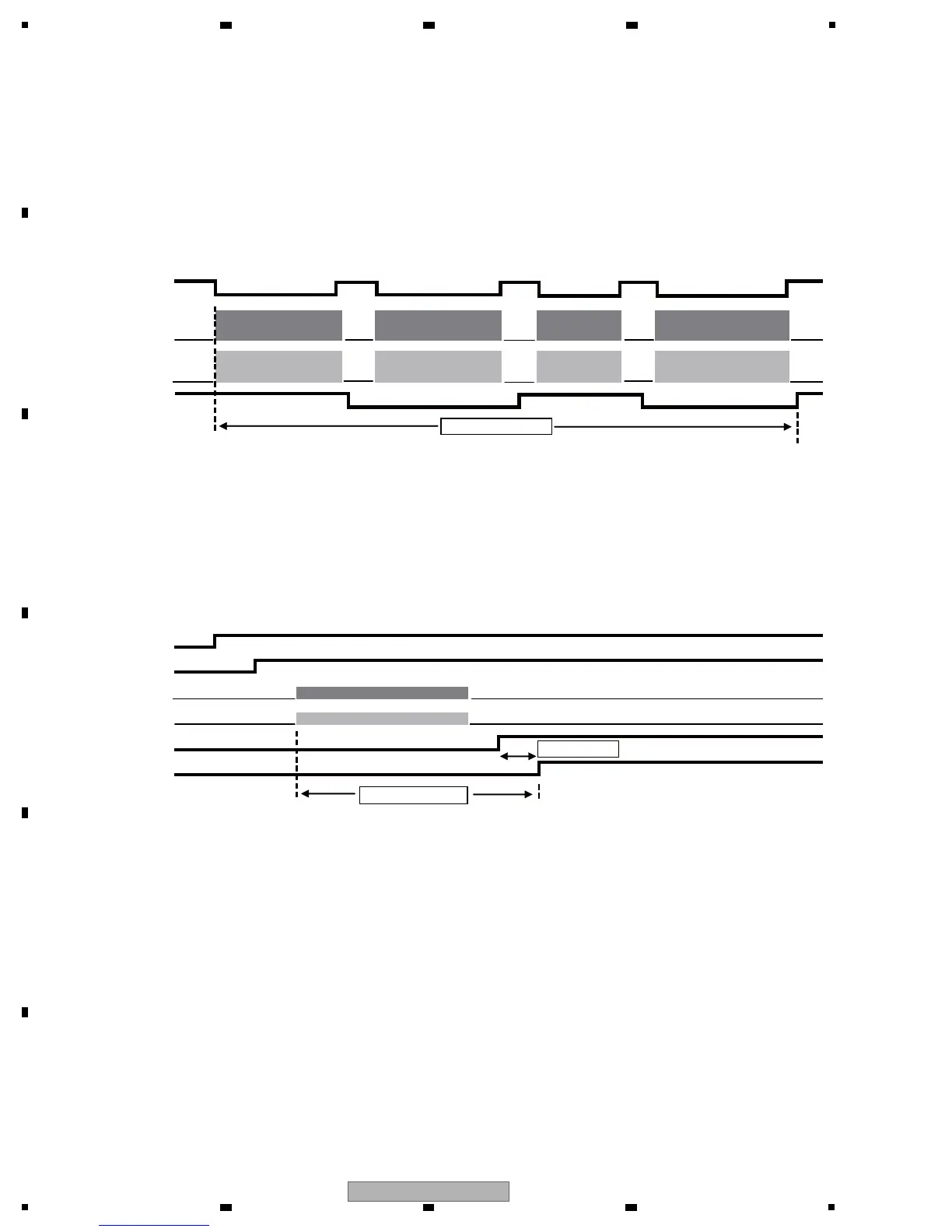

• Downloading the firmware to the AUDIO DSP

[3] Downloading Sequence

Downloading the firmware to the AUDIO DSP is performed in 4 sessions.

1. After reset of the AUDIO DSP is canceled, DSPCS# is set to “L.” Then transfer of the initialization program 1 starts.

2. After the transfer is completed, it is checked that DSPCS# is set to “H.” Then DSPDREQB# is set to “L.”

3. DSPCS# is set to “L.” Then transfer of the initialization program 2 starts.

4. After the transfer is completed, it is checked that DSPCS# is set to “H.” Then DSPDREQB# is set to “H.”

5. DSPCS# is set to “L” then transfer of the initial values starts.

6. After the transfer is completed, it is checked that DSPCS# is set to “H.” Then DSPDREQB# is set to “L.”

7. DSPCS# is set to “L.” Then transfer of the program for the main unit starts.

8. After the transfer is completed, it is checked that DSPCS# is set to “H.” Then DSPDREQB# is set to “H.”

Downloading is completed.

DSPCS# (Pin 50)

SPICLK (Pin 53)

SPIOUT (Pin 55)

Transfer of the

initialization program 1

Transfer of the

initialization program 2

Transfer of the

initial values

Transfer of the program

for the main unit

DSPDREQB# (Pin 27)

Note: The above-mentioned pin numbers are those of the IC202 (SOUTH CPU).

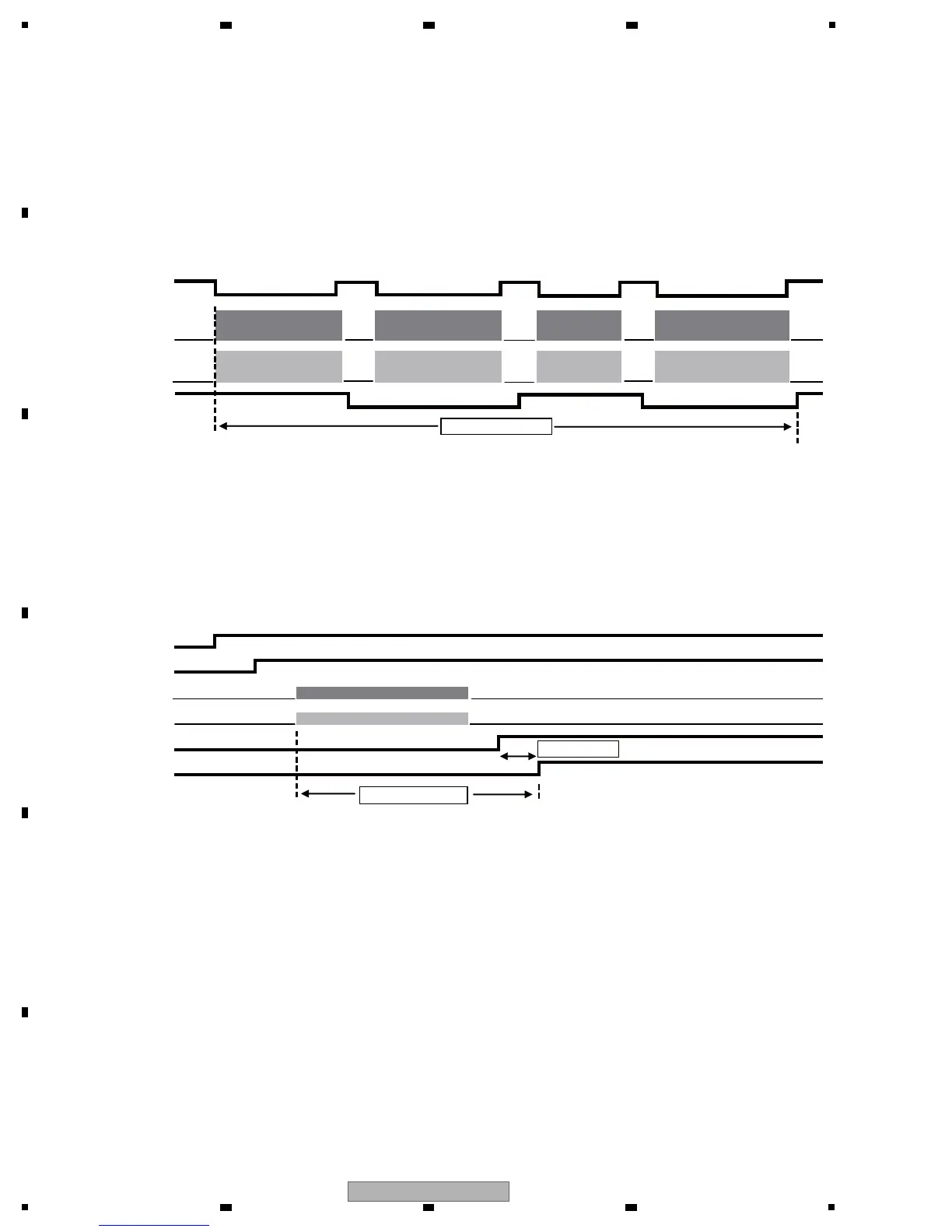

• Downloading the firmware to the FPGA

1. The FPGRM is set to “H.”

2. It is checked that SD2_OUT is set to “H.”

3. Transfer of the FPGA firmware starts.

4. After the transfer is completed, it is checked that DONE is set to “H.”

5. After a wait of 1 ms or more, FPGARST# is set to “H” (released).

Downloading is completed.

FPRGM (Pin 38)

SD2_OUT (Pin 36)

SPICLK (Pin 53)

SPIOUT (Pin 55)

Transfer of the FPGA firmware

FDONE (Pin 37)

FPGARST# (Pin 46)

Note: The above-mentioned pin numbers are those of the IC202 (SOUTH CPU).

1 ms or more

Approx. 200 msec

Approx. 110 msec

Loading...

Loading...