HAP-S1

86

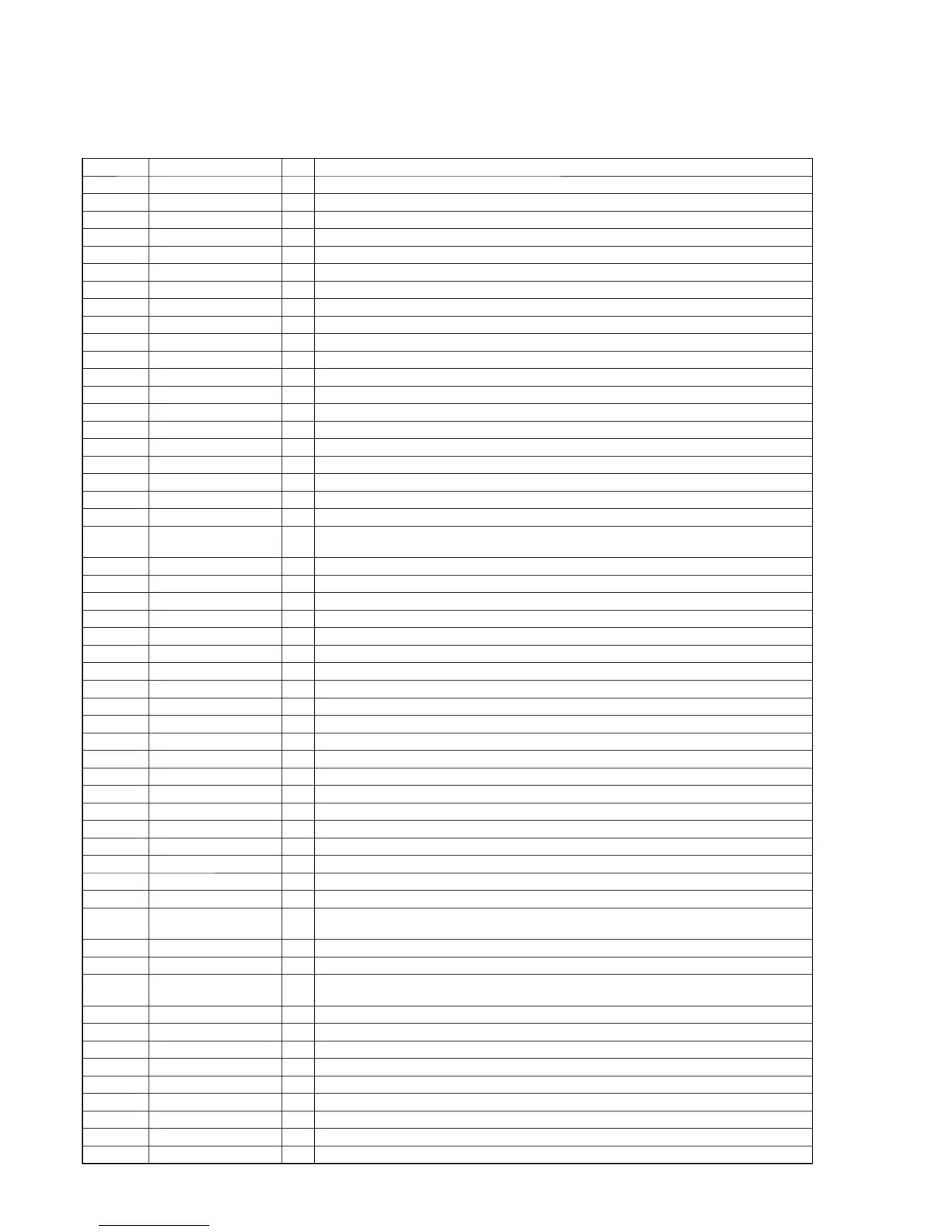

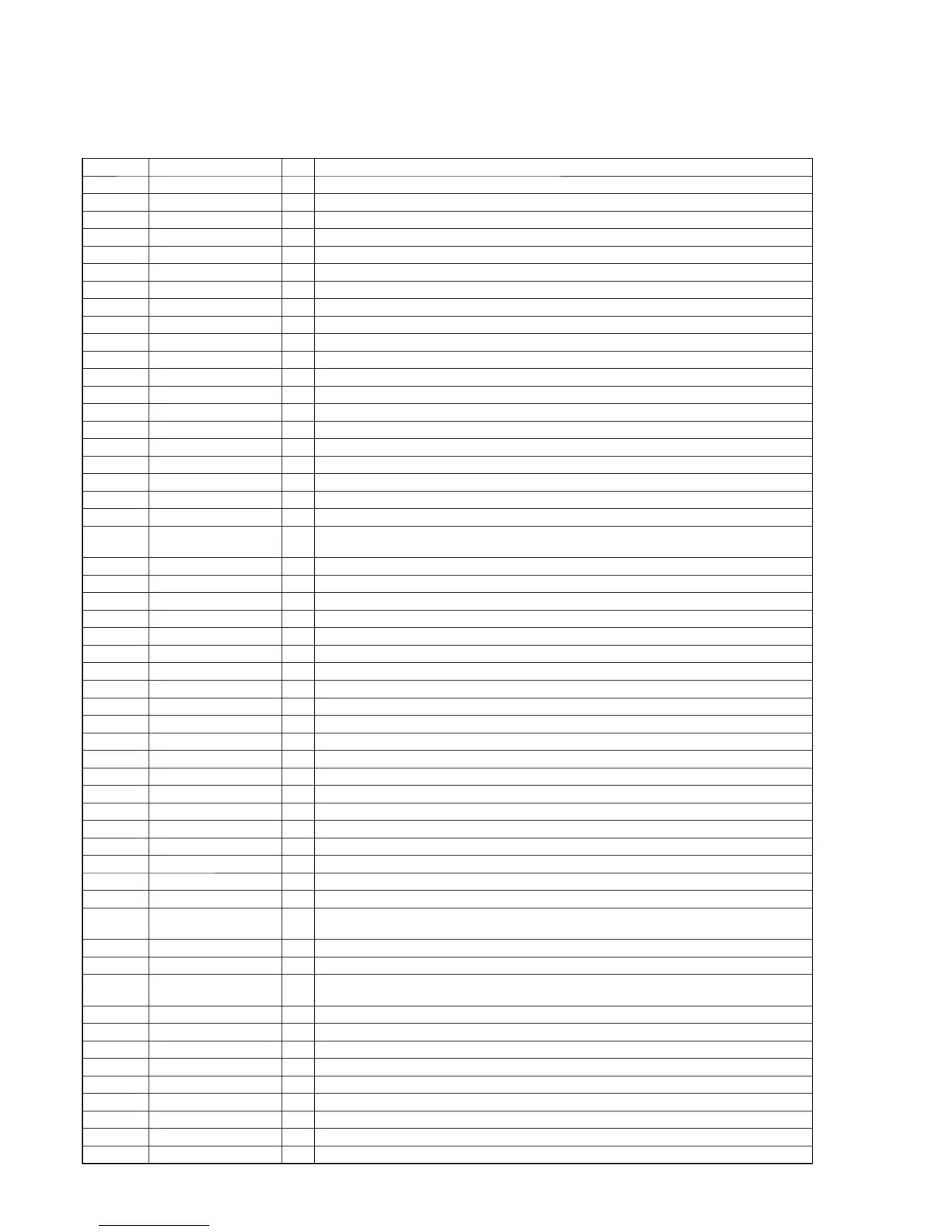

Pin No. Pin Name I/O Description

A2 PCIE_REXT - Terminal for the Impedance calibration

A3 PCIE_TXM O Transmit data (negative) output to the FPGA

A4 GND3 - Ground terminal

A5 FA_ANA - Not used

A6 USB_OTG_DP I/O Two-way USB data (positive) with the USB connector

A7 XTALI I System clock input terminal (24 MHz)

A8 GND4 - Ground terminal

A9 MLB_SN - Not used

A10 MLB_DP - Not used

A11 MLB_CN - Not used

A12 SATA_TXP O Transmit data (positive) output to the hard disk drive

A13 GND1 - Ground terminal

A14 SATA_RXM I Receive data (negative) input from the hard disk drive

A15 SD3_DAT2 I/O Two-way data bus terminal Not used

A16 NANDF_ALE O Reset signal output to the system controller “H”: reset

A17 NANDF_CS2 - Not used

A18 NANDF_D0 I/O Two-way data bus terminal Not used

A19 NANDF_D4 - Not used

A20 SD4_DAT3 I/O Two-way data bus with the fl ash memory

A21 SD1_DAT0 I/O Two-way data bus terminal Not used

A22, A23

SD2_DAT0,

SD2_DAT2

- Not used

A24 RGMII_TD3 O RGMII transmit data output to the ethernet transceiver

A25 GND2 - Ground terminal

B1 PCIE_RXM I Receive data (negative) input from the FPGA

B2 PCIE_RXP I Receive data (positive) input from the FPGA

B3 PCIE_TXP O Transmit data (positive) output to the FPGA

B4 GND22 - Ground terminal

B5 VDD_FA - Not used

B6 USB_OTG_DN I/O Two-way USB data (negative) with the USB connector

B7 XTALO O System clock output terminal (24 MHz)

B8 USB_OTG_CHD_B - Not used

B9 MLB_SP - Not used

B10 MLB_DN - Not used

B11 MLB_CP - Not used

B12 SATA_TXM O Transmit data (negative) output to the hard disk drive

B13 SD3_CMD - Not used

B14 SATA_RXP I Receive data (positive) input from the hard disk drive

B15 SD3_DAT3 - Not used

B16 NANDF_RB0 O Interrupt signal output terminal Not used

B17 SD4_CMD O Command signal output to the fl ash memory

B18 NANDF_D5 - Not used

B19, B20

SD4_DAT1,

SD4_DAT6

I/O Two-way data bus with the fl ash memory

B21 SD1_CMD - Not used

B22 SD2_DAT3 - Not used

B23, B24

RGMII_RD1,

RGMII_RD2

I RGMII receive data input from the ethernet transceiver

B25 RGMII_RXC I RGMII receive clock signal input from the ethernet transceiver

C1 GND23 - Ground terminal

C2 JTAG_TRSTB - Not used

C3 JTAG_TMS - Not used

C4 GND25 - Ground terminal

C5 CLK2_N - Not used

C6 GND26 - Ground terminal

C7 CLK1_N O Clock signal (negative) output to the FPGA

C8 GPANAIO - Not used

• IC Pin Function Description

MAIN BOARD IC101 MCIMX6D5EYM10AC (MPU)

Loading...

Loading...