Maintenance—2230 Service

INPUT_PORTS. This exerciser displays the input data

for all microprocessor input ports. An explanation of the

displayed data is shown in Table 6-23.

A_TO_D_TESTS/SAMPLES. This exerciser sets the

number of acquisitions used to test the A/D Converter.

Turn the CURSORS control to select the number of

4096 byte acquisitions (a power of 2 is best) used to test

the A/D Converter (see LINEARITY exerciser).

A_TO_D_TESTS/LINEARITY. This exerciser tests the

acquisition A/D converter for missing bits.

Inject a highly linear 11 division vertically centered, (2 x

4096 x 50) ns duration triangle wave signal into the CH 1

or X input. Set the trigger so that the oscilloscope triggers

close to the negative peak.

If any codes are missing in samples x 4096 acquisi

tions a message indicating that there were missing codes

is displayed (and sent to the communications option if

operating in extended diagnostics).

Setting the trigger point close to the positive peak tests

negative going conversions.

The display is a histogram with a vertical scale of 5 x

samples X (codes converted) per division and a horizontal

scale of 0 to 255 codes across 10 divisions left to right

(25.5 codes per division).

COM_OPTION/DEBUG. This exerciser is used in

debuging the communications option. Debug outputs a

test message and displays any incoming messages (data)

on the crt.

PICTURES. The picture exercisers use line drawings to

exercise the instruments display system. The Tekbug is a

line drawing of the Tektronix symbol. The Wizard is a multi

function display. The gain of the display controller is

controlled by the CURSORS control. The position of the

display is controlled by the CH 1 and CH 2 POSITION

controls. If the VERTICAL POSITION and CURSORS

controls are not turned for about 5 seconds, the display is

automatically moved through its gain (CURSORS) and

POSITION ranges.

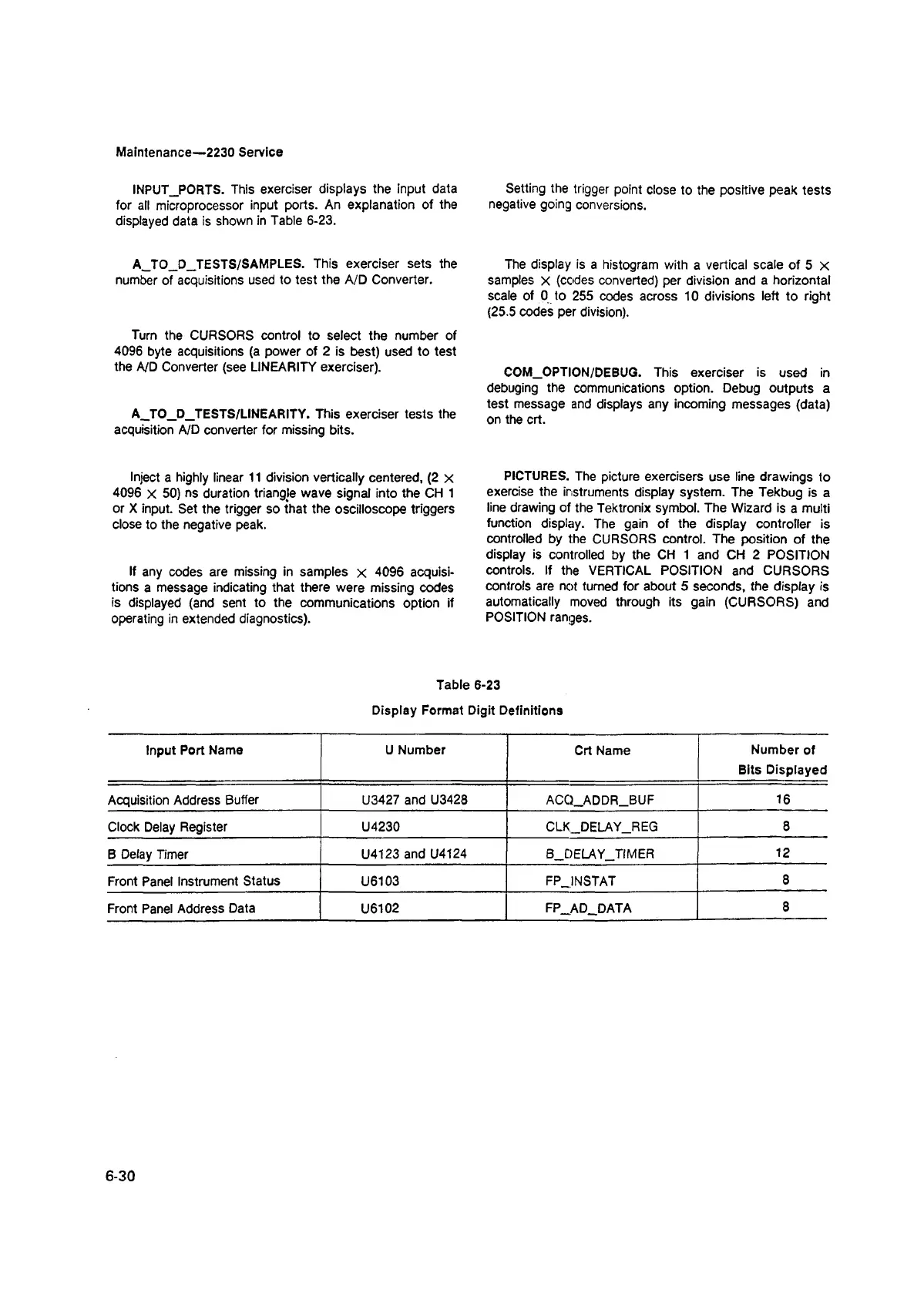

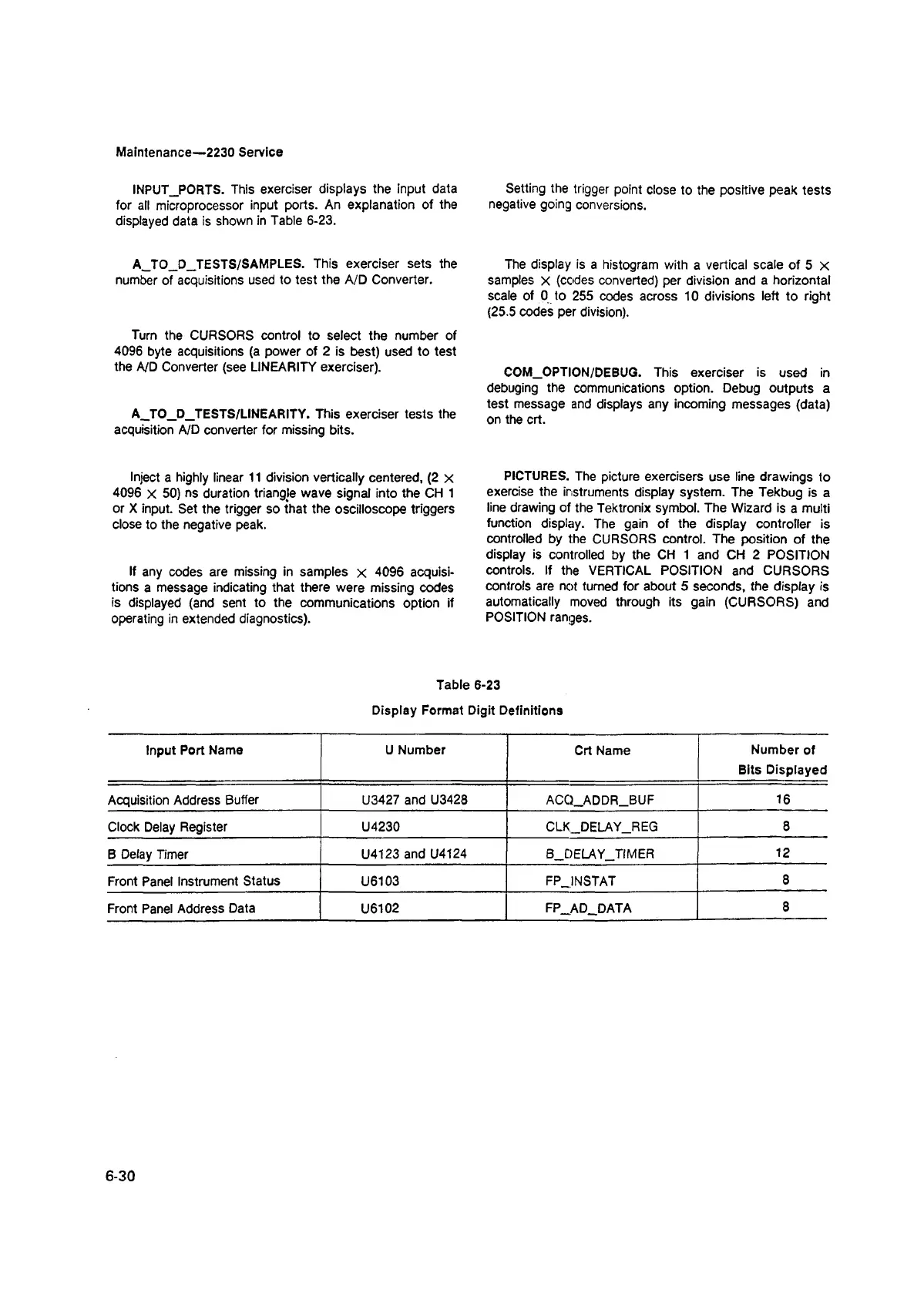

Table 6-23

Display Format Digit Definitions

Input Port Name

U Number

Crt Name

Number of

Bits Displayed

Acquisition Address Buffer U3427 and U3428 ACQ_ADDR_BUF

16

Clock Delay Register

U4230 CLK_DELAY_REG

8

B Delay Timer

U4123 and U4124

B_DELAY_TIMER

12

Front Panel Instrument Status

U6103 FPJNSTAT

8

Front Panel Address Data

U6102

FP_AD_DATA

8

6-30

Loading...

Loading...