LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

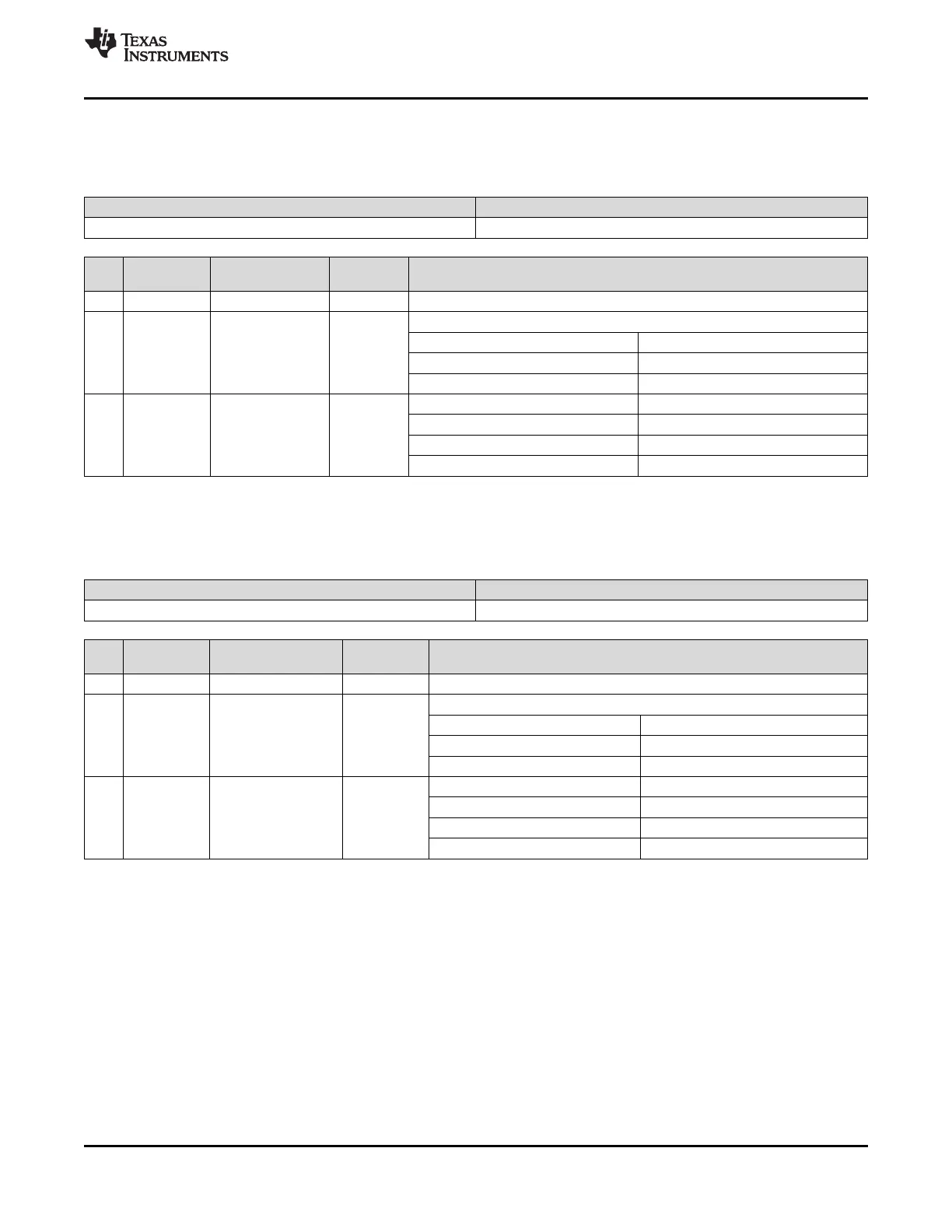

9.7.3.3 SYSREF_DIV[12:8], SYSREF_DIV[7:0]

These registers set the value of the SYSREF output divider.

Table 25. Registers 0x13A, 0x13B

MSB LSB

0x13A[4:0] 0x13B[7:0]

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

7:5 0x13A NA 0 Reserved

Divide value for the SYSREF outputs.

Field Value Divide Value

4:0 0x13A SYSREF_DIV[12:8] 12

0x00 to 0x07 Reserved

8 (0x08) 8

9 (0x09) 9

... ...

7:0 0x13B SYSREF_DIV[7:0] 0

8190 (0x1FFE) 8190

8191 (0X1FFF) 8191

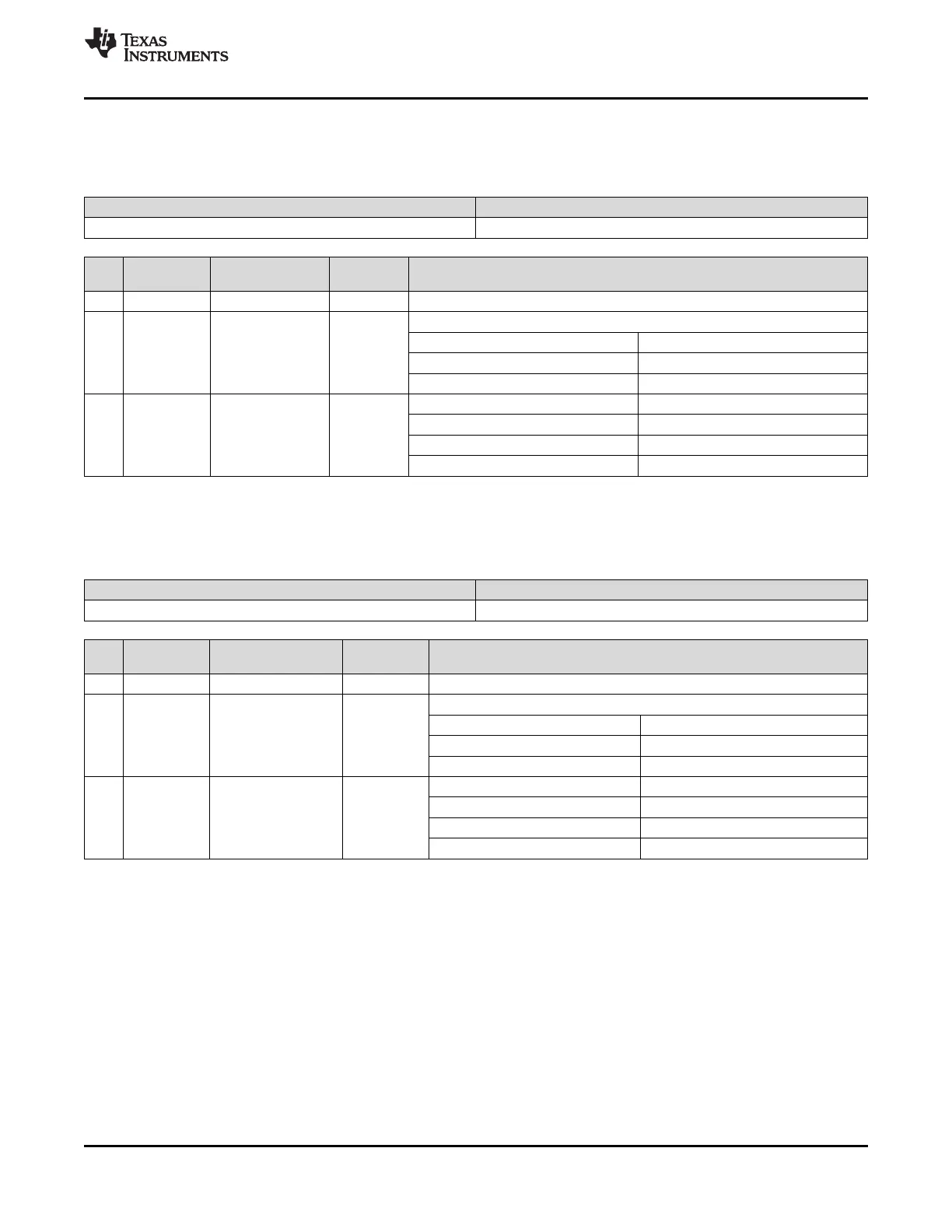

9.7.3.4 SYSREF_DDLY[12:8], SYSREF_DDLY[7:0]

These registers set the delay of the SYSREF digital delay value.

Table 26. SYSREF Digital Delay Register Configuration, SYSREF_DDLY[12:0]

MSB LSB

0x13C[4:0] 0x13D[7:0]

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

7:5 0x13C NA 0 Reserved

Sets the value of the SYSREF digital delay.

Field Value Delay Value

4:0 0x13C SYSREF_DDLY[12:8] 0

0x00 to 0x07 Reserved

8 (0x08) 8

9 (0x09) 9

... ...

7:0 0x13D SYSREF_DDLY[7:0] 8

8190 (0x1FFE) 8190

8191 (0X1FFF) 8191

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 63

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...