LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

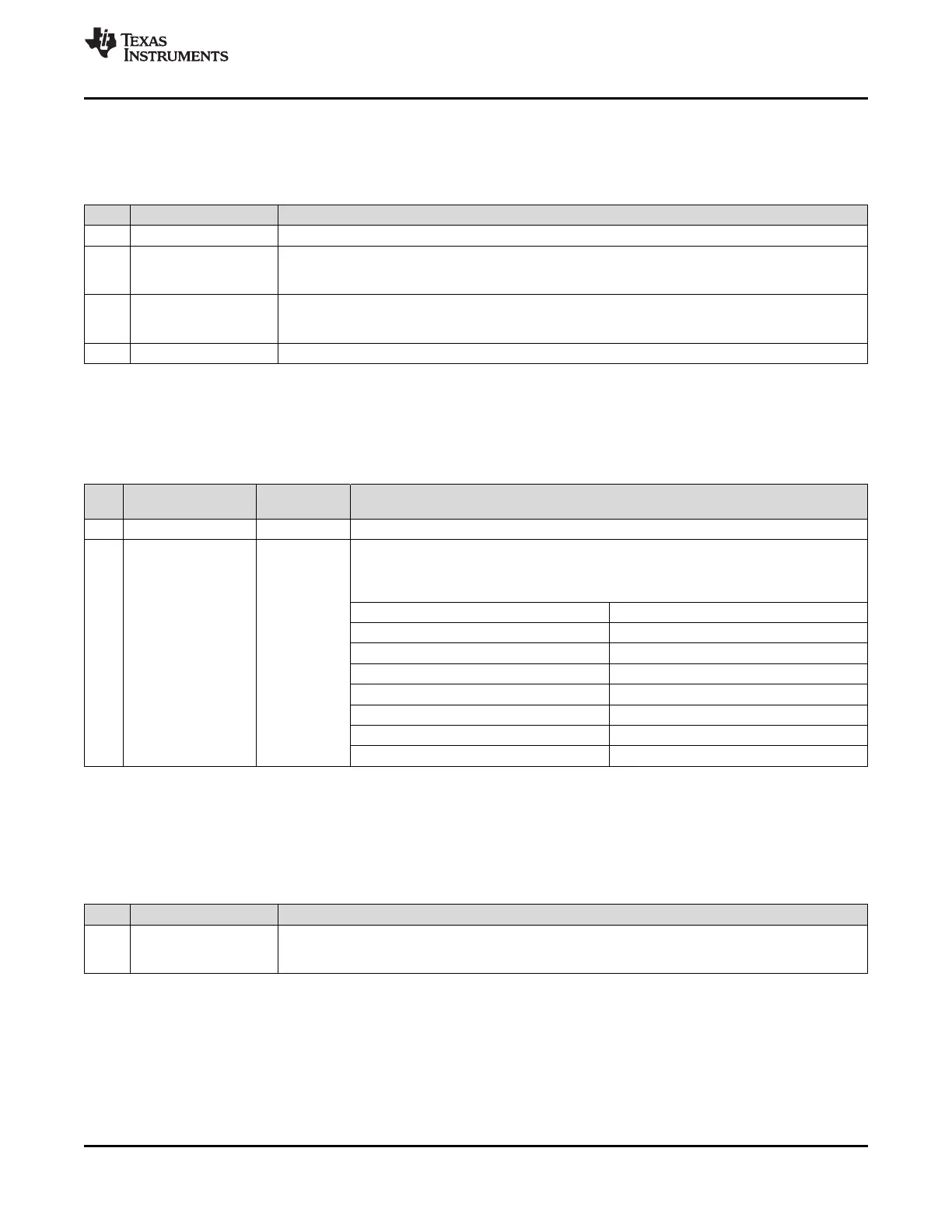

9.7.9 (0x16F - 0x1FFF) Misc Registers

9.7.9.1 PLL2_PRE_PD, PLL2_PD

Table 74. Register 0x173

BIT NAME DESCRIPTION

7 N/A Reserved

Powerdown PLL2 prescaler

6 PLL2_PRE_PD 0: Normal Operation

1: Powerdown

Powerdown PLL2

5 PLL2_PD 0: Normal Operation

1: Powerdown

4:0 N/A Reserved

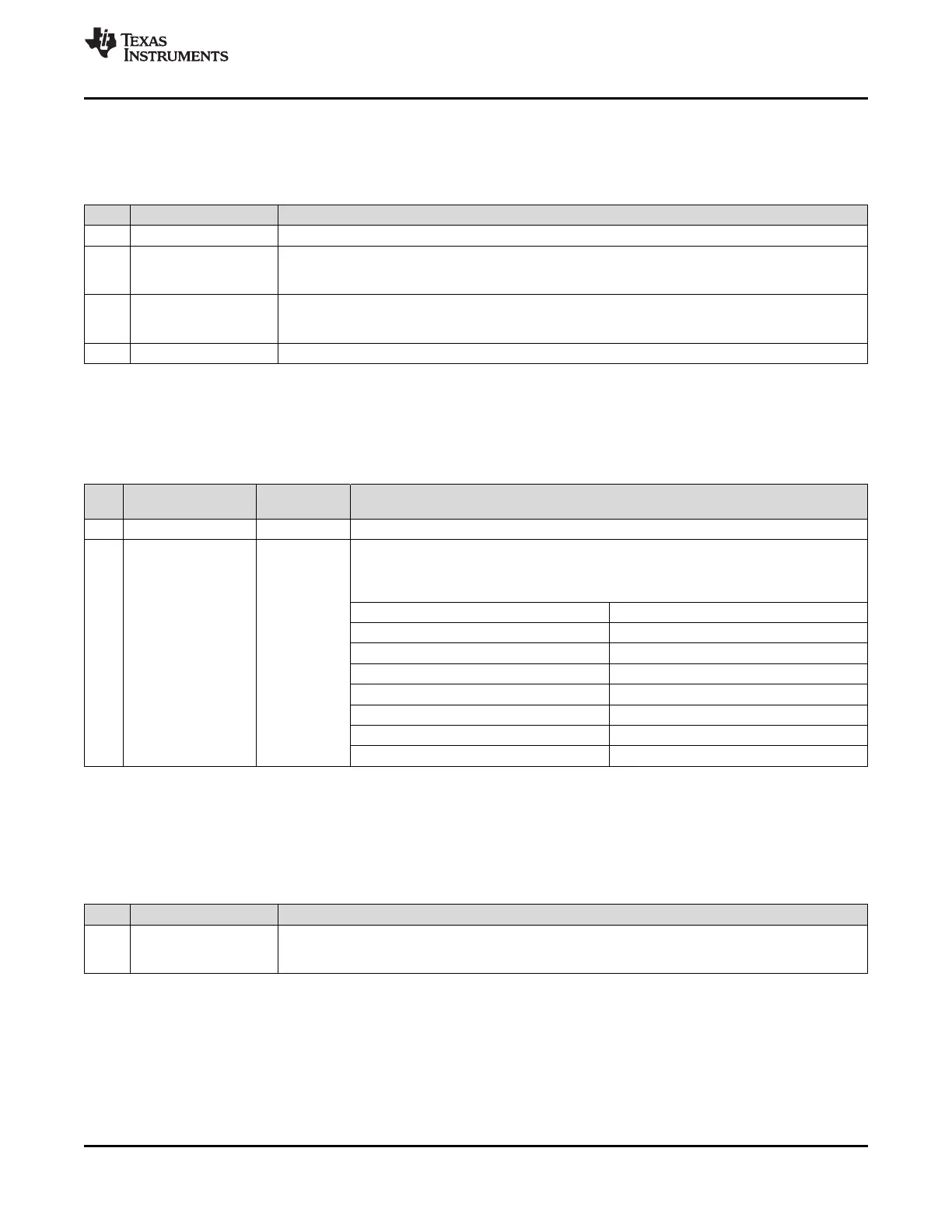

9.7.9.2 VCO1_DIV

Sets VCO1 VCO divider value. This divider cannot be bypassed and has a minimum value of 2. This register is

reserved for LMK04826 and LMK04828 and should be left unprogrammed.

Table 75. Register 0x174

POR

BIT NAME DESCRIPTION

DEFAULT

7:5 N/A 0 Reserved

When VCO_MUX selects VCO1 for LMK04821, the clock distribution frequency will be

equal to VCO1 frequency divided by this divide value. Note this divider is also on the PLL2

feedback path and will impact PLL2 N divider value.

Unlisted field values are reserved.

Field Value Divide Value

0 (0x00) 2

VCO1_DIV

4:0 0

5 (0x05) 3

(LMK04821 only)

10 (0x0A) 8

20 (0x14) 4

23 (0x17) 5

27 (0x1B) 7

30 (0x1E) 6

9.7.9.3 OPT_REG_1

This register must be written with the following value depending on which LMK0482x family part is used to

optimize VCO1 phase noise performance over temperature. This register must be written before writing register

0x168 when using VCO1.

Table 76. Register 0x17C

BIT NAME DESCRIPTION

21: LMK04821

7:0 OPT_REG_1 24: LMK04826

21: LMK04828

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 91

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...