LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

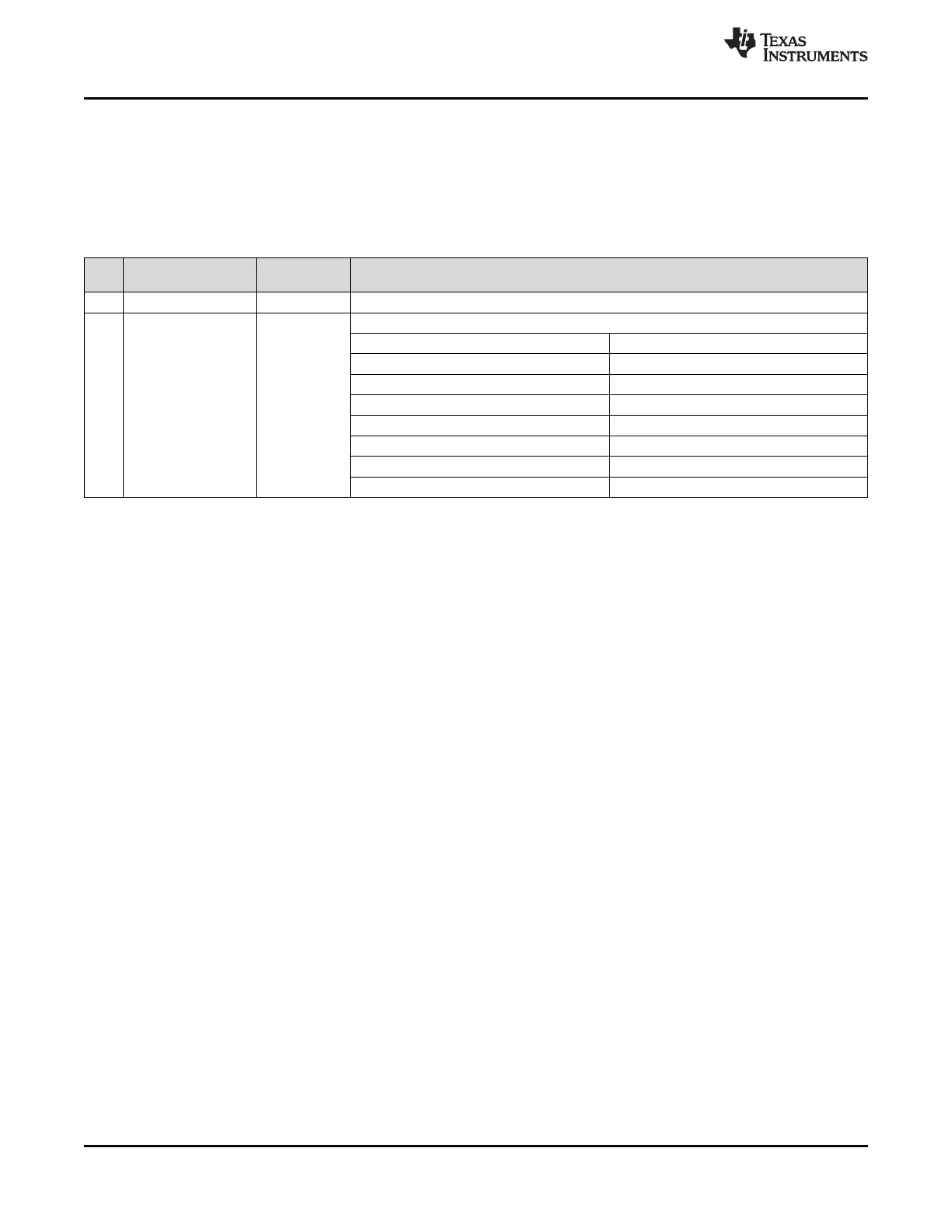

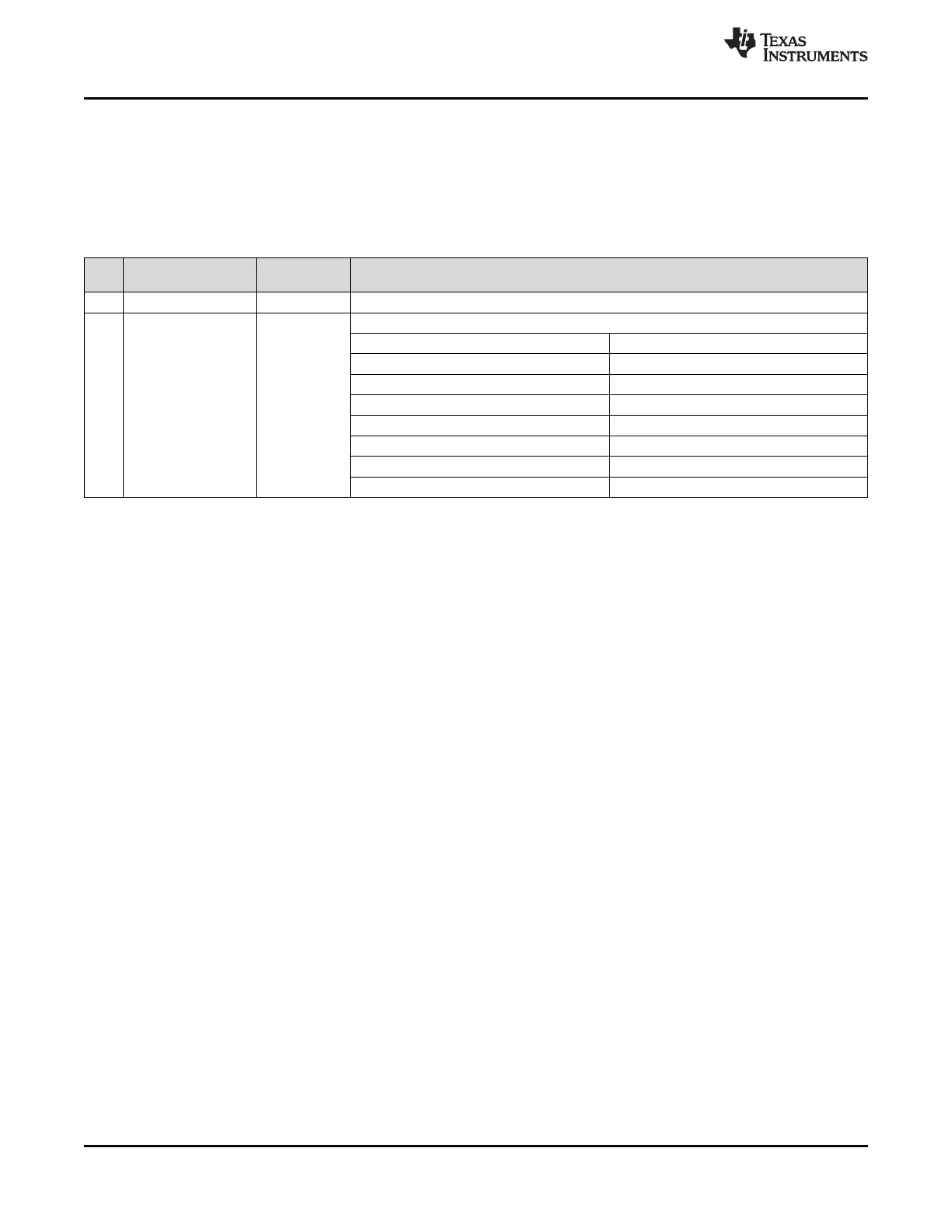

9.7.3.9 DDLYd_STEP_CNT

This register sets the number of dynamic digital delay adjustments occur. Upon programming, the dynamic digital

delay adjustment begins for each clock output with dynamic digital delay enabled. Dynamic digital delay can only

be started by SPI.

Other registers must be set: SYNC_MODE = 3

Table 31. Register 0x142

POR

BIT NAME DESCRIPTION

DEFAULT

7:4 NA 0 Reserved

Sets the number of dynamic digital delay adjustments that will occur.

Field Value SYNC Generation

0 (0x00) No Adjust

1 (0x01) 1 step

3:0 DDLYd_STEP_CNT 0 2 (0x02) 2 steps

3 (0x03) 3 steps

... ...

14 (0x0E) 14 steps

15 (0x0F) 15 steps

66 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...