41

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

SpecificationsCopyright © 2013–2016, Texas Instruments Incorporated

5.8 Timing and Switching Characteristics

5.8.1 SYSCLK (Frequencies)

5.8.1.1 Switching Characteristics over Recommended Operating Conditions for Clock Domains

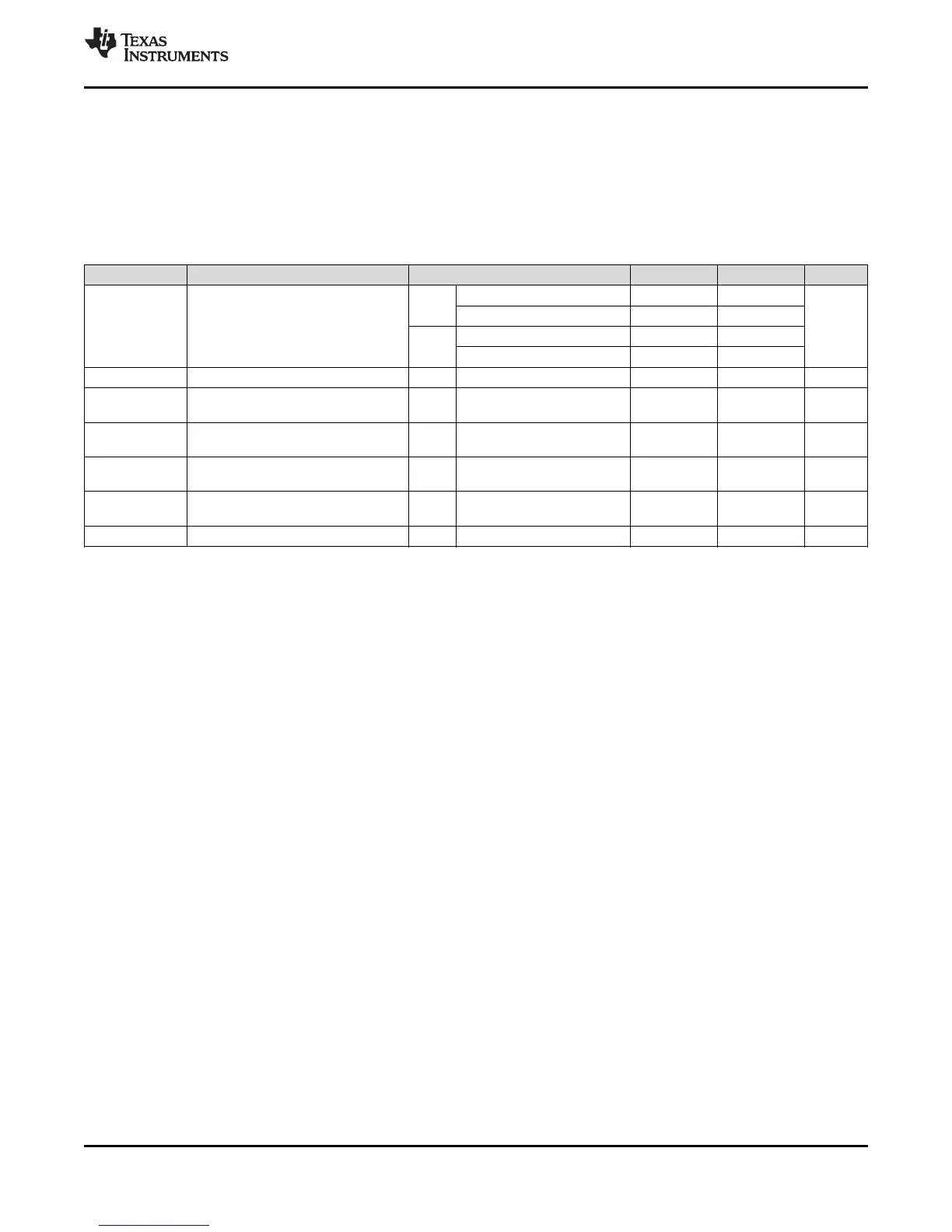

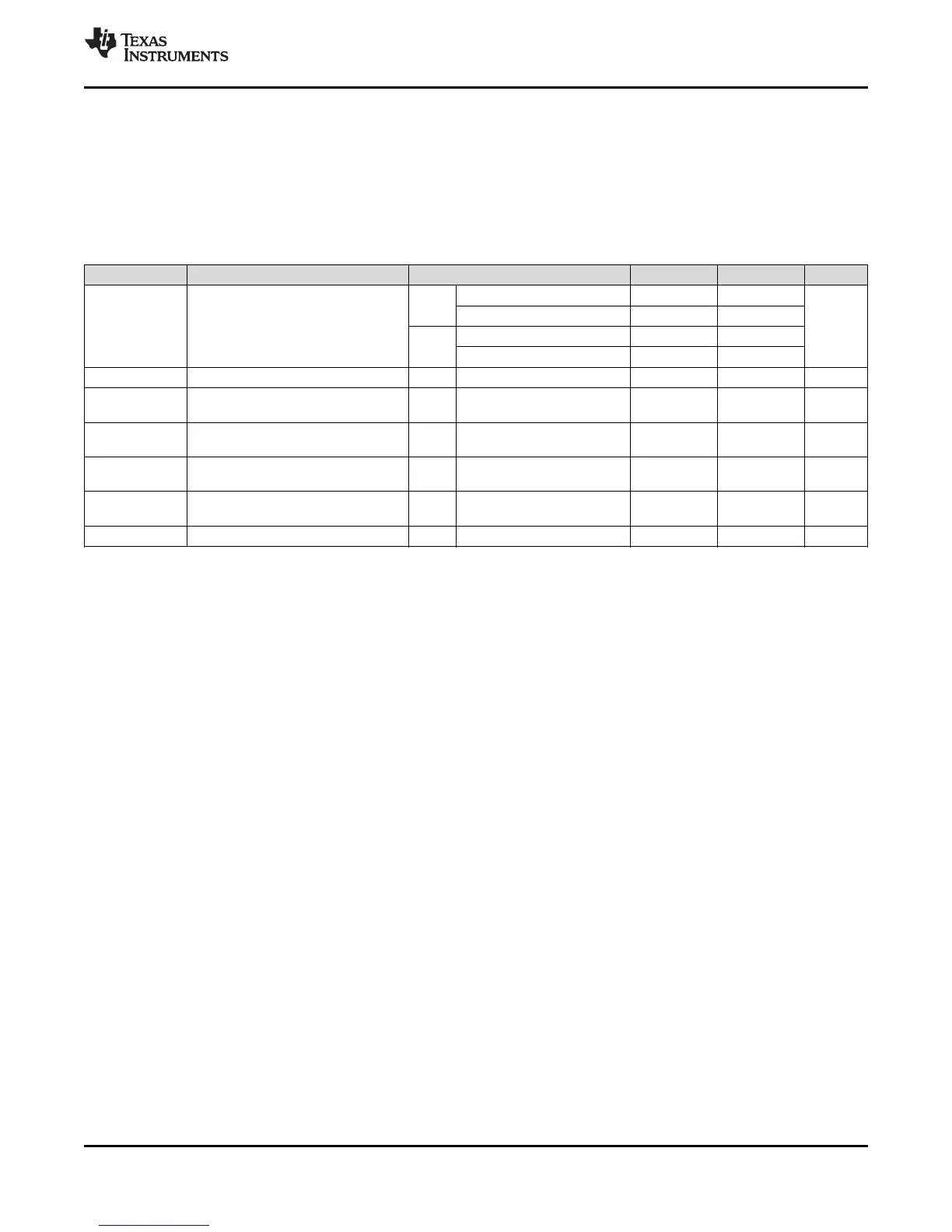

Table 5-3. Clock Domain Timing Specifications

PARAMETER DESCRIPTION CONDITIONS MIN MAX UNIT

f

HCLK

HCLK - System clock frequency

PZ

Pipeline mode enabled 100

MHz

Pipeline mode disabled 45

PGE

Pipeline mode enabled 160

Pipeline mode disabled 50

f

GCLK

GCLK - CPU clock frequency f

HCLK

MHz

f

VCLK

VCLK - Primary peripheral clock

frequency

100 MHz

f

VCLK2

VCLK2 - Secondary peripheral clock

frequency

100 MHz

f

VCLK4

VCLK4 - Secondary peripheral clock

frequency

150 MHz

f

VCLKA1

VCLKA1 - Primary asynchronous

peripheral clock frequency

100 MHz

f

RTICLK

RTICLK - Clock frequency f

VCLK

MHz

Loading...

Loading...