RAM

Address Wait States

0 MHz f

HCLK(max)

Data Wait States

0 MHz f

HCLK(max)

Flash (Main Memory)

Address Wait States

0 MHz f

HCLK(max)

RWAIT Setting 0

0 MHz 50MHz f

HCLK(max)

Flash (Data Memory)

EWAIT Setting

2 3 4 5

0 MHz 45MHz 60MHz 75MHz 90MHz f

HCLK(max)

0

0

1

1

0

RAM

Address Wait States

0 MHz f

HCLK(max)

Data Wait States

0 MHz f

HCLK(max)

Flash (Main Memory)

Address Wait States

0 MHz 150MHz f

HCLK(max)

RWAIT Setting 0

0 MHz 50MHz f

HCLK(max)

Flash (Data Memory)

EWAIT Setting 2

3

4 5 6 7 8 9

0 MHz 45MHz 60MHz 75MHz 90MHz 105MHz 120MHz 135MHz 150MHz

0

0

1

0 1

2 31

100MHz 150MHz

f

HCLK(max)

42

TMS570LS0714

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

Specifications Copyright © 2013–2016, Texas Instruments Incorporated

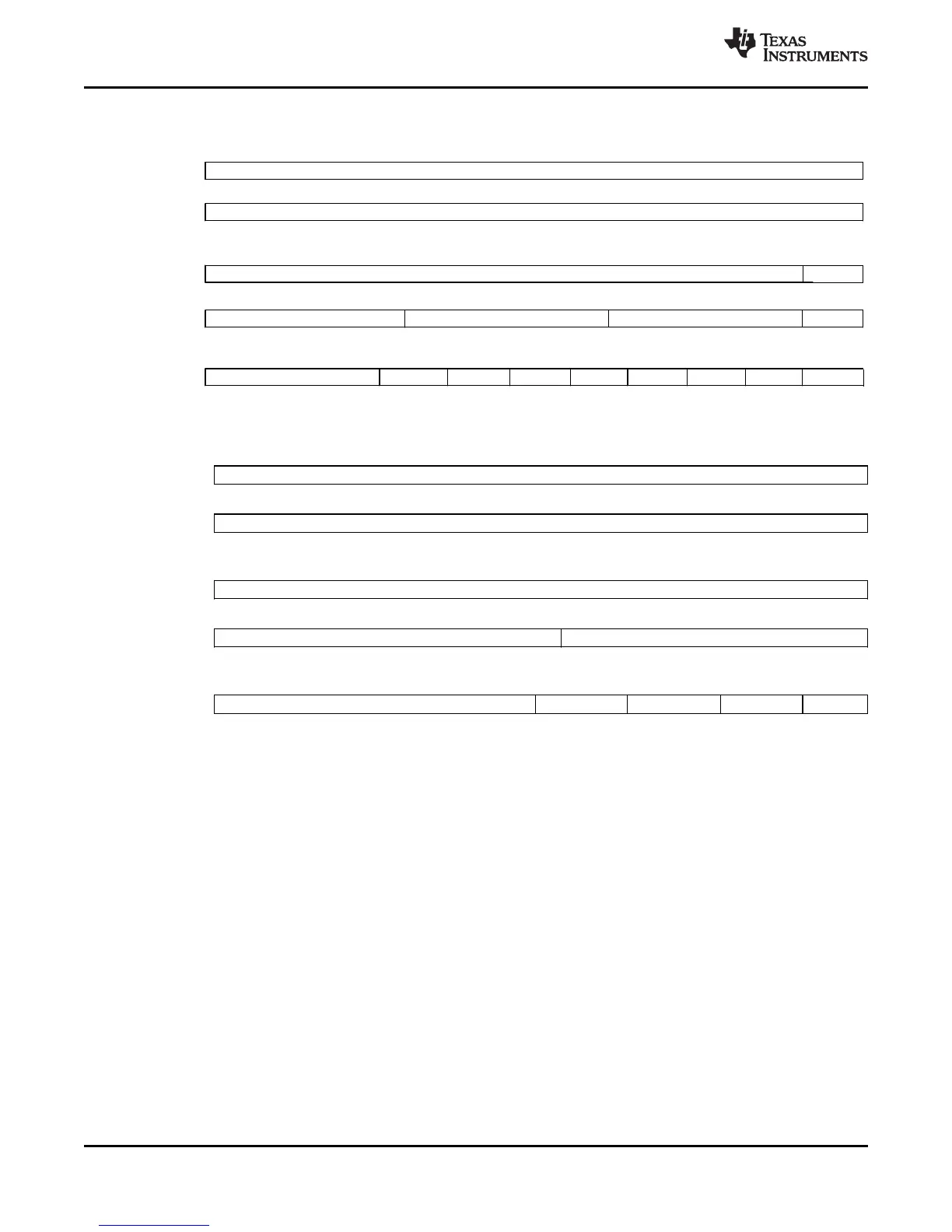

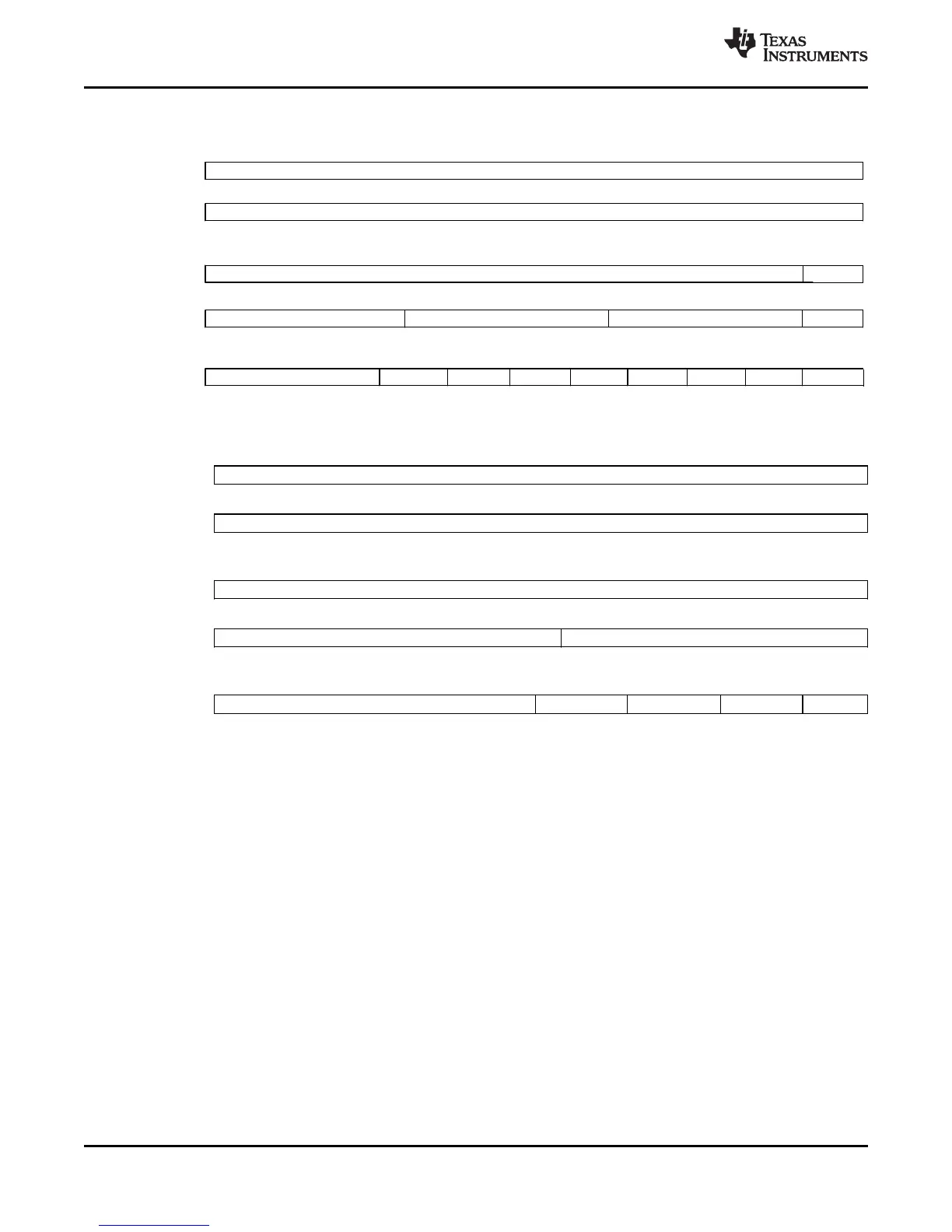

5.8.1.2 Wait States Required - PGE and PZ Packages

Figure 5-1. Wait States Scheme — PGE, 160 MHz

Figure 5-2. Wait States Scheme — PZ, 100 MHz

As shown in Figure 5-1 and Figure 5-2, the TCM RAM can support program and data fetches at full CPU

speed without any address or data wait states required.

The TCM flash can support zero address and data wait states up to a CPU speed of 50 MHz in

nonpipelined mode. The flash supports a maximum CPU clock speed of 160 MHz in pipelined mode for

the PGE Package, and 100 MHz for the PZ package.

The flash wrapper defaults to nonpipelined mode with zero address wait state and one random-read data

wait state.

Loading...

Loading...