30 www.xilinx.com Spartan-3E Starter Kit Board User Guide

UG230 (v1.0) March 9, 2006

Chapter 4:

FPGA Configuration Options

R

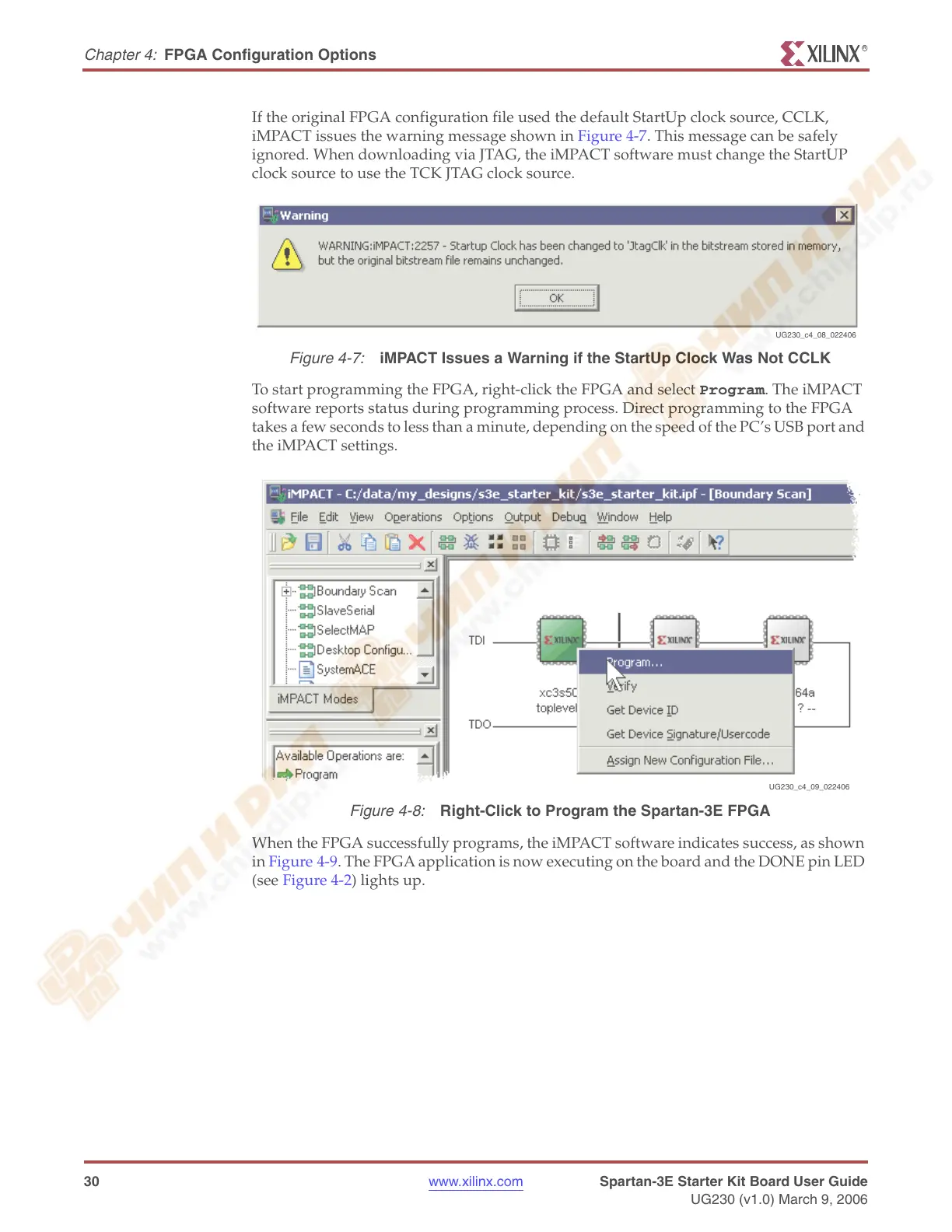

If the original FPGA configuration file used the default StartUp clock source, CCLK,

iMPACT issues the warning message shown in Figure 4-7. This message can be safely

ignored. When downloading via JTAG, the iMPACT software must change the StartUP

clock source to use the TCK JTAG clock source.

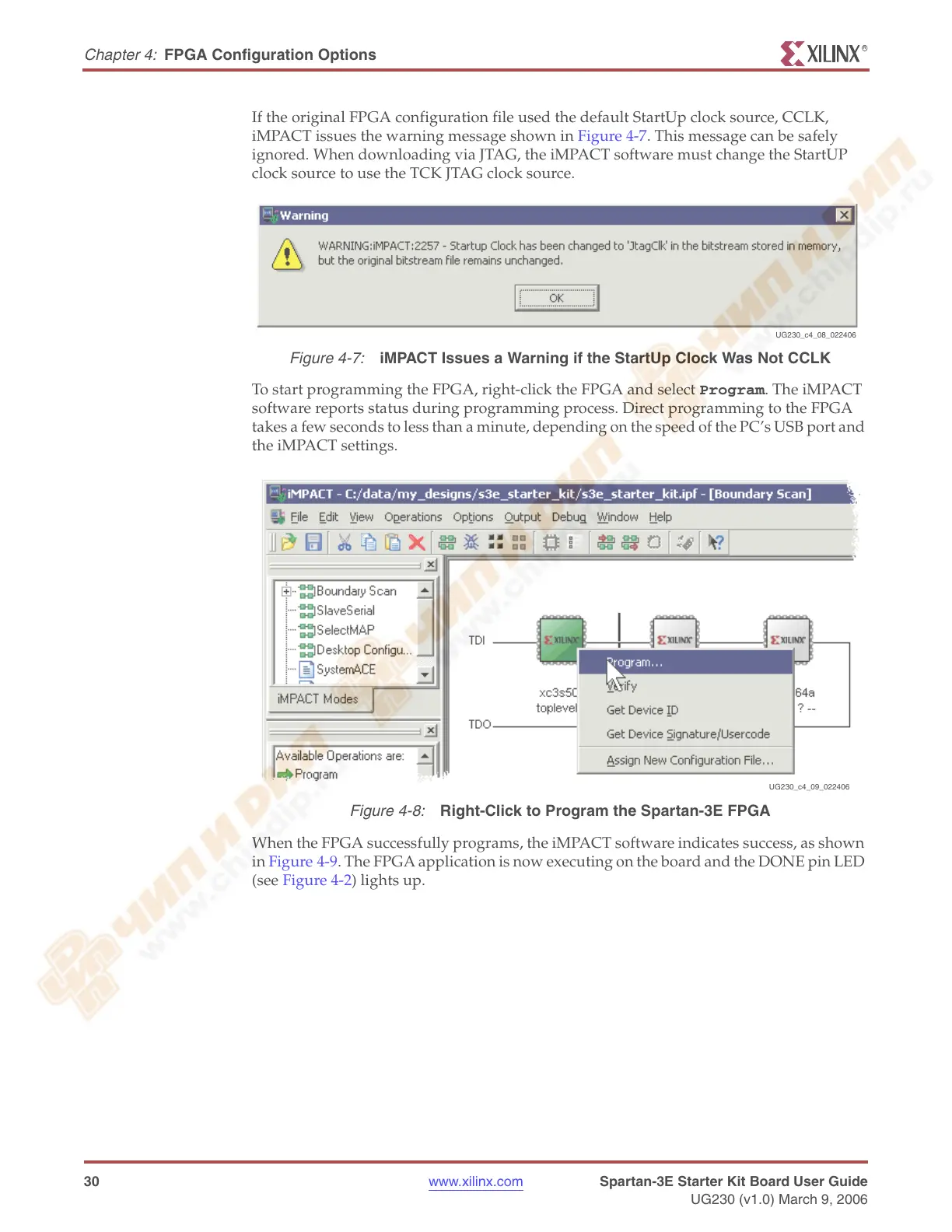

To start programming the FPGA, right-click the FPGA and select Program. The iMPACT

software reports status during programming process. Direct programming to the FPGA

takes a few seconds to less than a minute, depending on the speed of the PC’s USB port and

the iMPACT settings.

When the FPGA successfully programs, the iMPACT software indicates success, as shown

in Figure 4-9. The FPGA application is now executing on the board and the DONE pin LED

(see Figure 4-2) lights up.

Figure 4-7:

iMPACT Issues a Warning if the StartUp Clock Was Not CCLK

Figure 4-8:

Right-Click to Program the Spartan-3E FPGA

UG230_c4_08_022406

UG230_c4_09_022406

Loading...

Loading...