84 www.xilinx.com Spartan-3E Starter Kit Board User Guide

UG230 (v1.0) March 9, 2006

Chapter 11:

Intel StrataFlash Parallel NOR Flash PROM

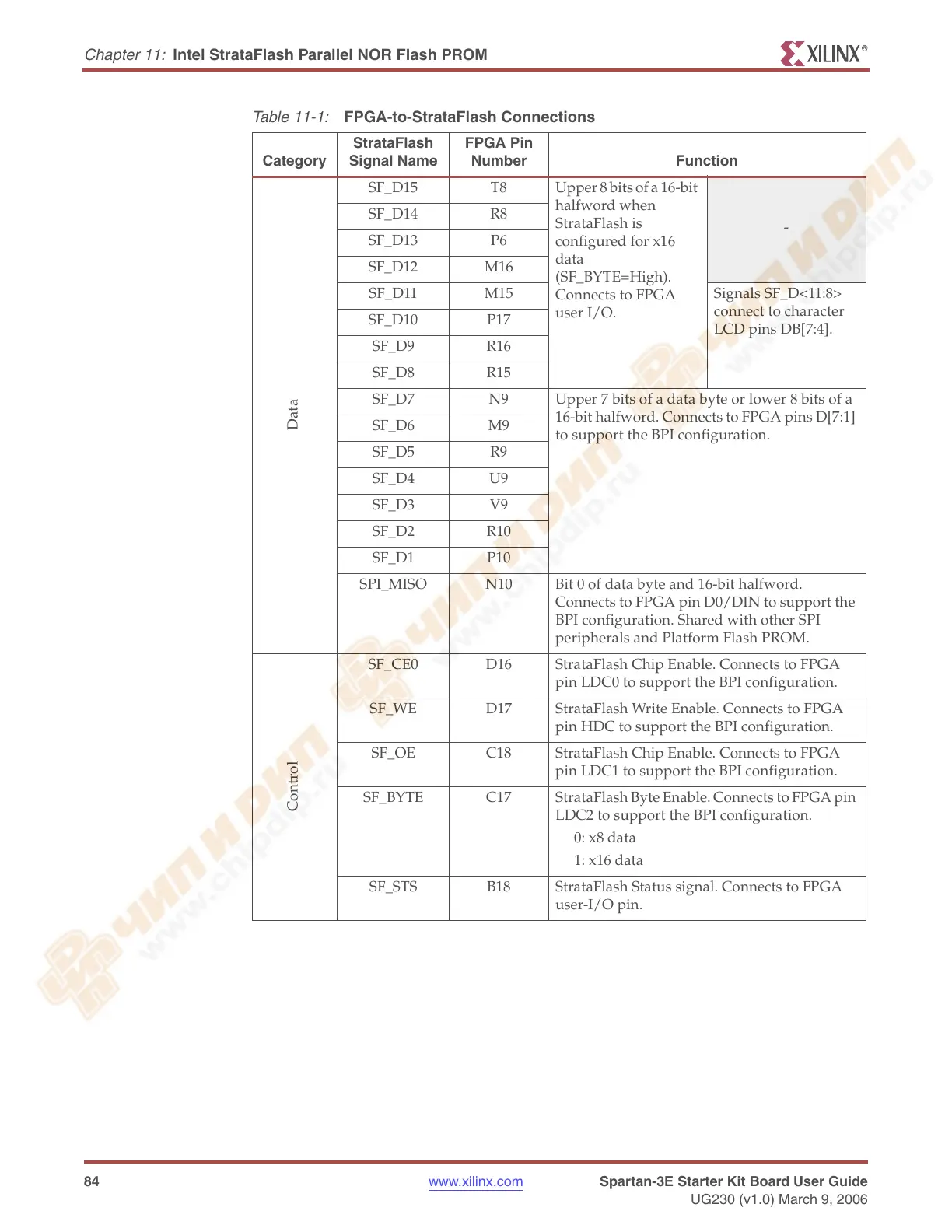

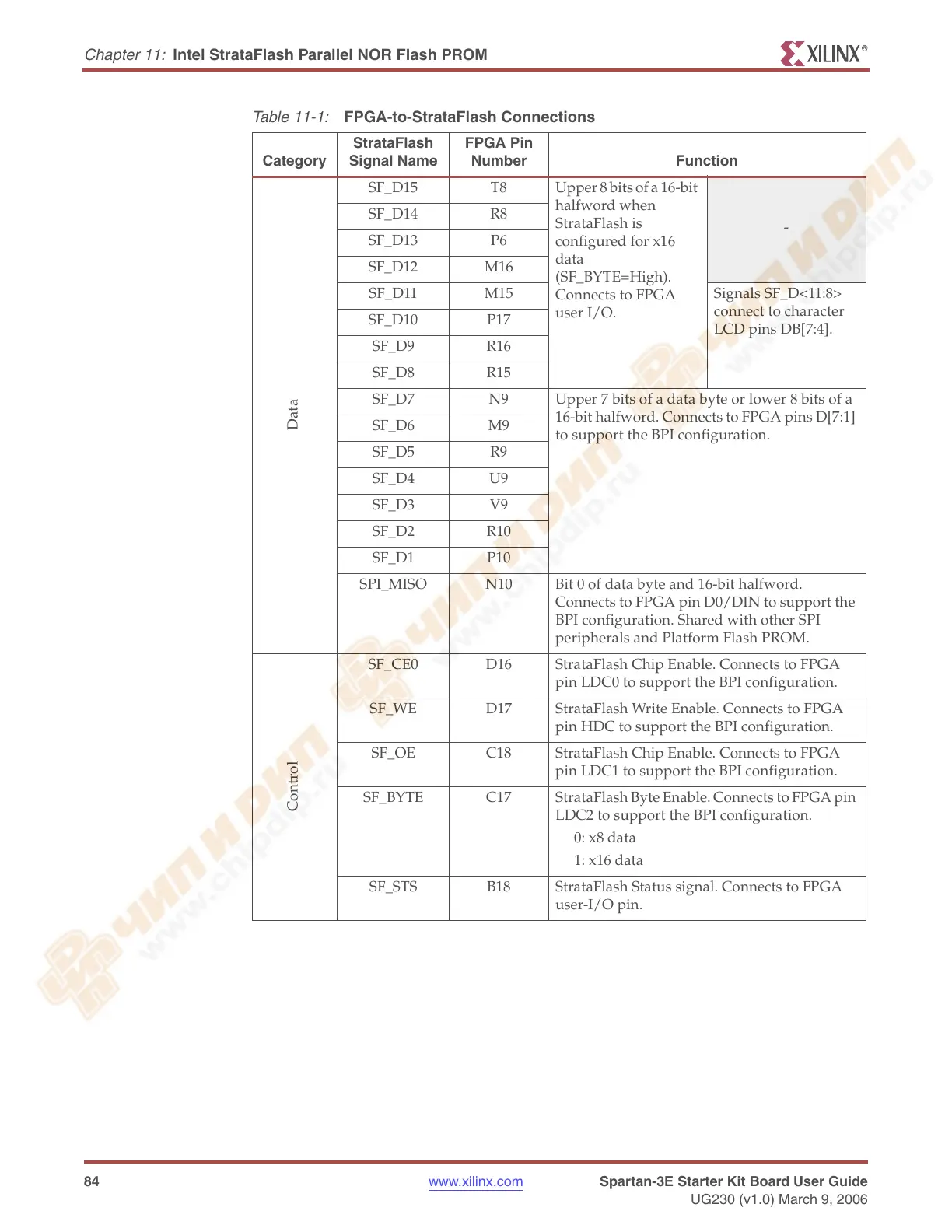

R

Data

SF_D15 T8 Upper 8 bits of a 16-bit

halfword when

StrataFlash is

configured for x16

data

(SF_BYTE=High).

Connects to FPGA

user I/O.

-

SF_D14 R8

SF_D13 P6

SF_D12 M16

SF_D11 M15 Signals SF_D<11:8>

connect to character

LCD pins DB[7:4].

SF_D10 P17

SF_D9 R16

SF_D8 R15

SF_D7 N9 Upper 7 bits of a data byte or lower 8 bits of a

16-bit halfword. Connects to FPGA pins D[7:1]

to support the BPI configuration.

SF_D6 M9

SF_D5 R9

SF_D4 U9

SF_D3 V9

SF_D2 R10

SF_D1 P10

SPI_MISO N10 Bit 0 of data byte and 16-bit halfword.

Connects to FPGA pin D0/DIN to support the

BPI configuration. Shared with other SPI

peripherals and Platform Flash PROM.

Control

SF_CE0 D16 StrataFlash Chip Enable. Connects to FPGA

pin LDC0 to support the BPI configuration.

SF_WE D17 StrataFlash Write Enable. Connects to FPGA

pin HDC to support the BPI configuration.

SF_OE C18 StrataFlash Chip Enable. Connects to FPGA

pin LDC1 to support the BPI configuration.

SF_BYTE C17 StrataFlash Byte Enable. Connects to FPGA pin

LDC2 to support the BPI configuration.

0: x8 data

1: x16 data

SF_STS B18 StrataFlash Status signal. Connects to FPGA

user-I/O pin.

Table 11-1:

FPGA-to-StrataFlash Connections

Category

StrataFlash

Signal Name

FPGA Pin

Number Function

Loading...

Loading...