44 www.xilinx.com Spartan-6 FPGA PCB Design and Pin Planning

UG393 (v1.1) April 29, 2010

Chapter 4: PCB Materials and Traces

A good PCB manufacturer understands controlled impedance and allows fine adjustments

for line widths to produce a Z

0O

of 50Ω . The PCB manufacturer also provides the

parameters necessary for the specific PCB layout. Some parameters can be calculated or

simulated from the guideline outlined in the example. Although ±10% tolerance on Z

0O

is

typical and can provide adequate performance, the additional cost of a tighter tolerance

results in better channel performance.

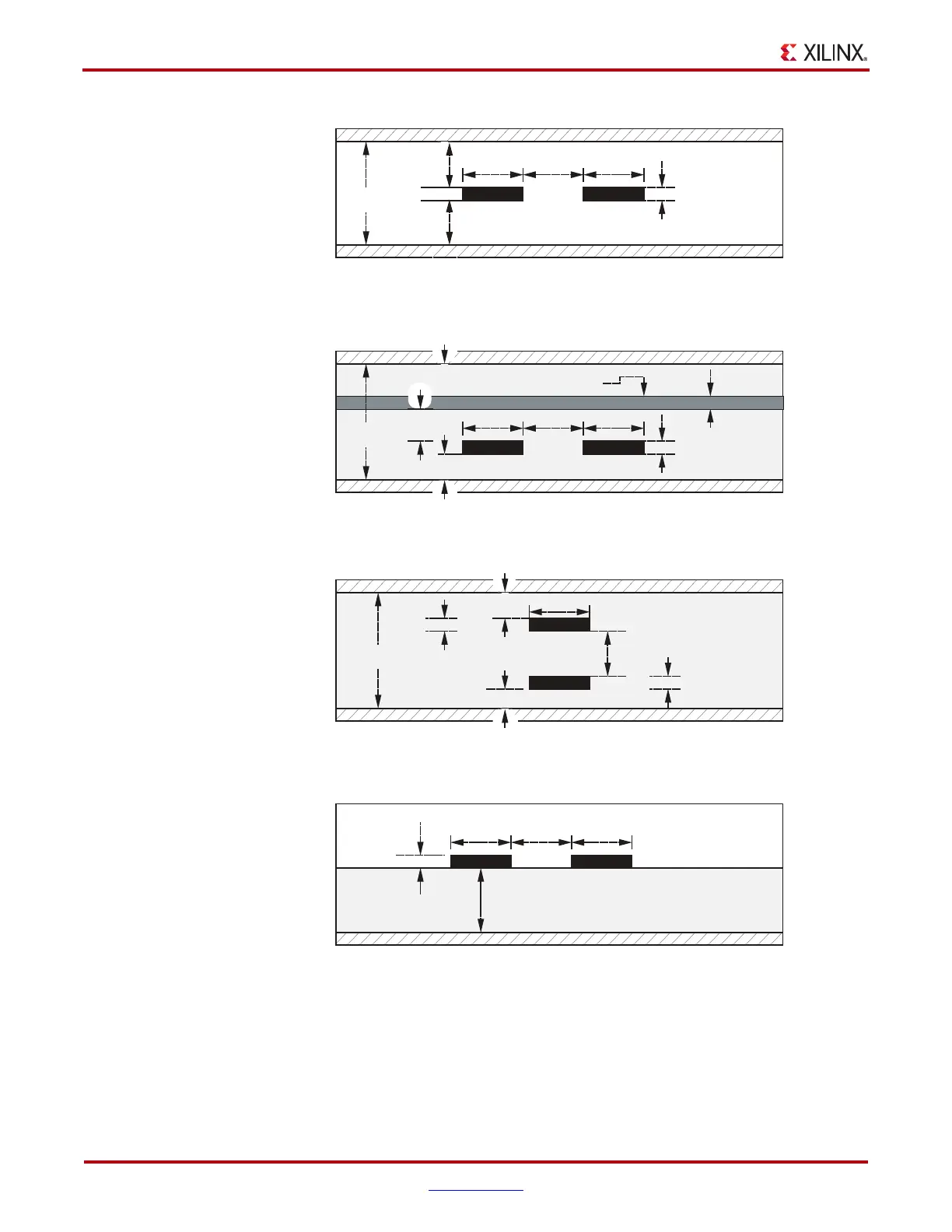

X-Ref Target - Figure 4-1

Figure 4-1: Differential Edge-Coupled Centered Stripline

X-Ref Target - Figure 4-2

Figure 4-2: Differential Edge-Coupled Offset Stripline

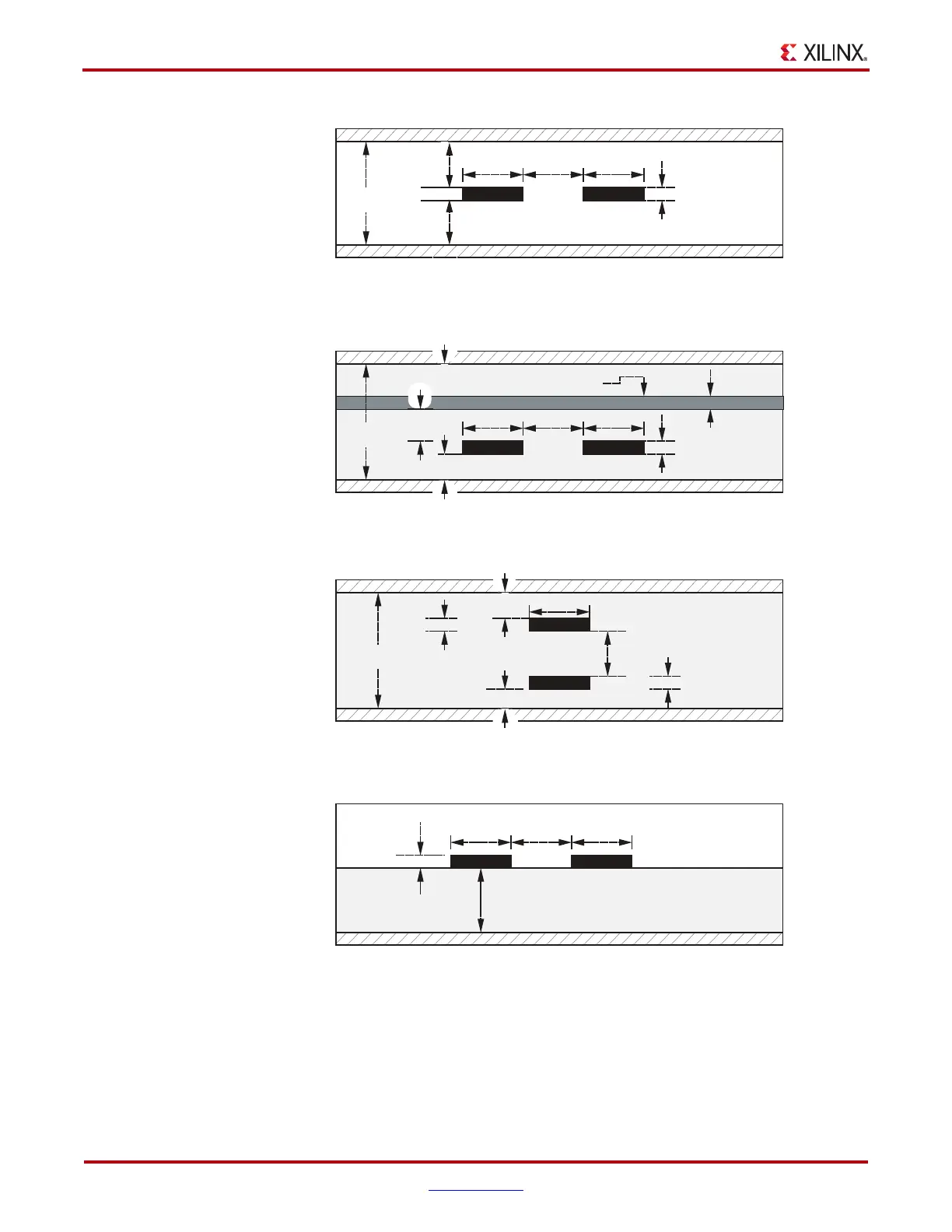

X-Ref Target - Figure 4-3

Figure 4-3: Centered Broadside-Coupled Stripline

X-Ref Target - Figure 4-4

Figure 4-4: Differential Microstrip

UG393_c4_01_091809

h

h

wws

Er

t

d=2h+t

h

h

wws

Er

t

t

d=3h+2t

h

orthogonal lines

UG393_c4_02_091809

t

t

Er

h

h

w

2h

d=4h+2t

UG393_c4_03_091809

wws

t

Er

Er = 1

h

UG393_c4_04_091809

Loading...

Loading...