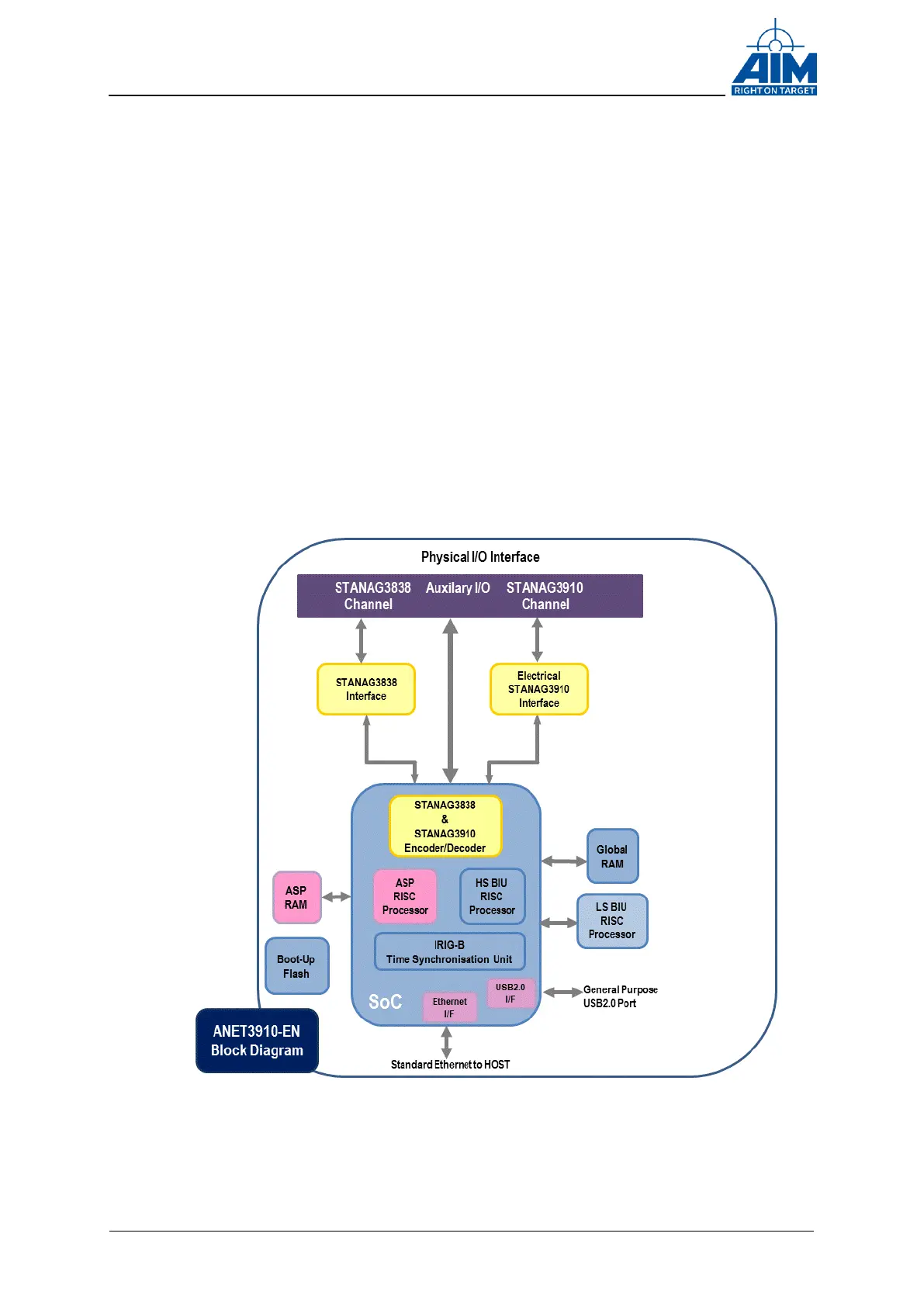

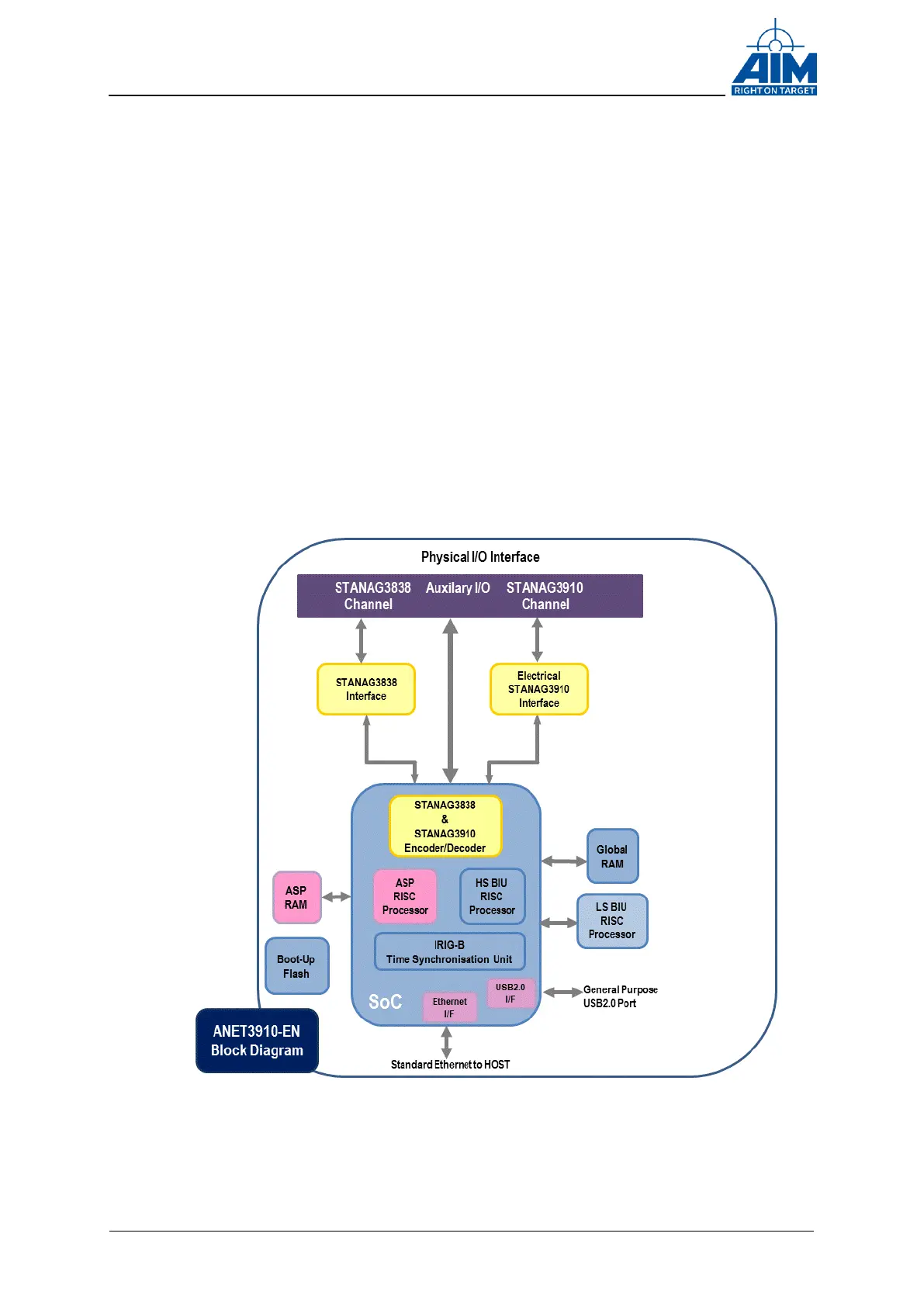

4. Structure of the ANET3910-EN

4 STRUCTURE OF THE ANET3910-EN

The ANET3910-EN comprises the following main sections:

System FPGA/SoC

Global RAM

LS-BIU Section

Physical I/O Interface

ASP Section

IRIG-B-122 – Time Code Processor with Free Wheeling Function

4.1 System FPGA/SoC

Includes the 3838- and 3910-Core, the Global RAM I/F, the LS-BIU I/F, the HS-BIU

Processor and the Application Support Processor (ASP).

Figure 4-1 ANET3910-EN Blockdiagram

Loading...

Loading...