106 Rockwell Automation Publication 1756-RM003N-EN-P - October 2011

Chapter 2 Bit Instructions (XIC, XIO, OTE, OTL, OTU, ONS, OSR, OSF, OSRI, OSFI)

Execution:

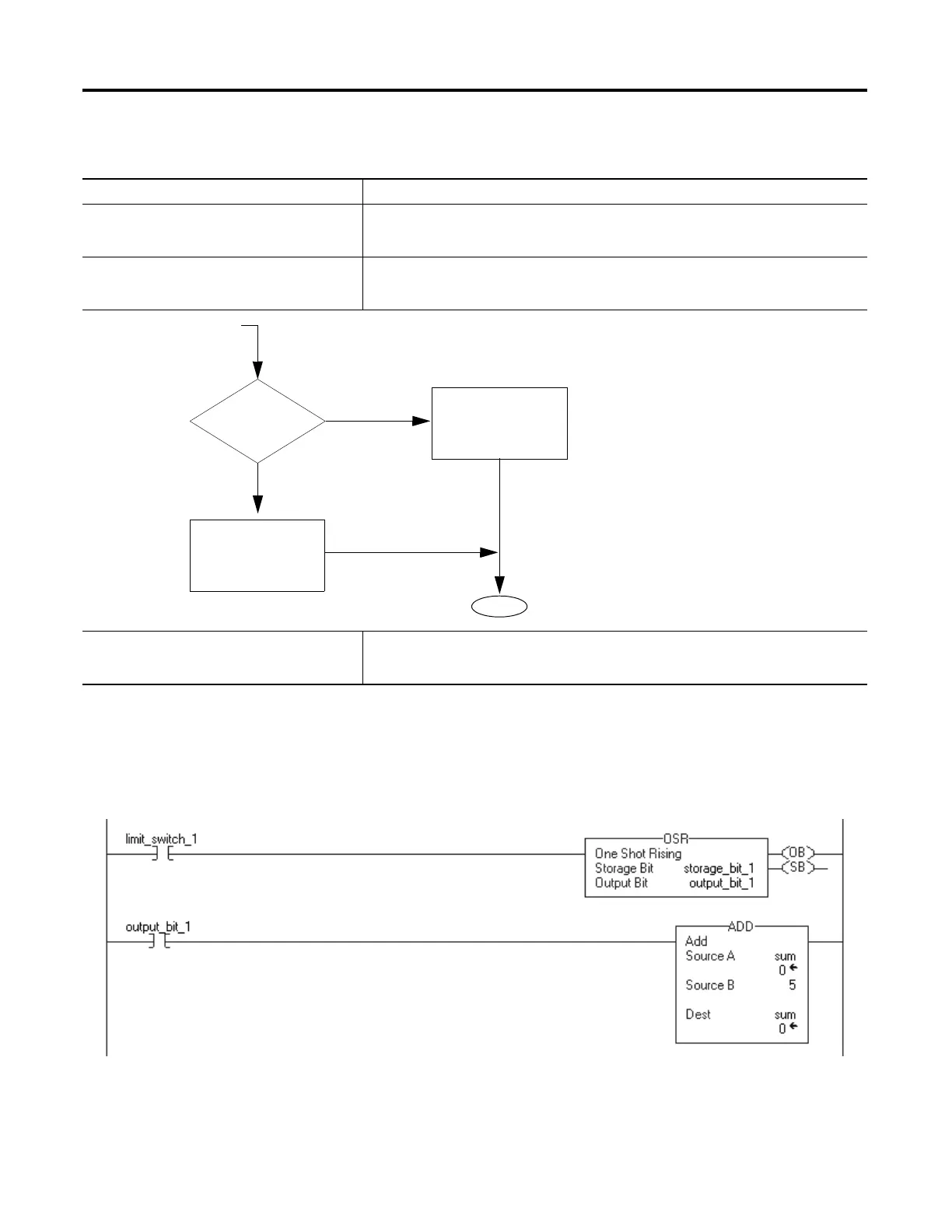

Example: Each time limit_switch_1 goes from cleared to set, the OSR instruction sets

output_bit_1 and the ADD instruction increments sum by five. As long as

limit_switch_1 stays set, sum stays the same value. The limit_switch_1 must go

from cleared to set again for sum to be incremented again. You can use

output_bit_1 on multiple rungs to trigger other operations

Condition Relay Ladder Action

Prescan. The storage bit is set to prevent an invalid trigger during the first scan.

The output bit is cleared.

The rung-condition-out is set to false.

Rung-condition-in is false. The storage bit is cleared.

The output bit is not modified.

The rung-condition-out is set to false.

Postscan The storage bit is cleared.

The output bit is not modified.

The rung-condition-out is set to false.

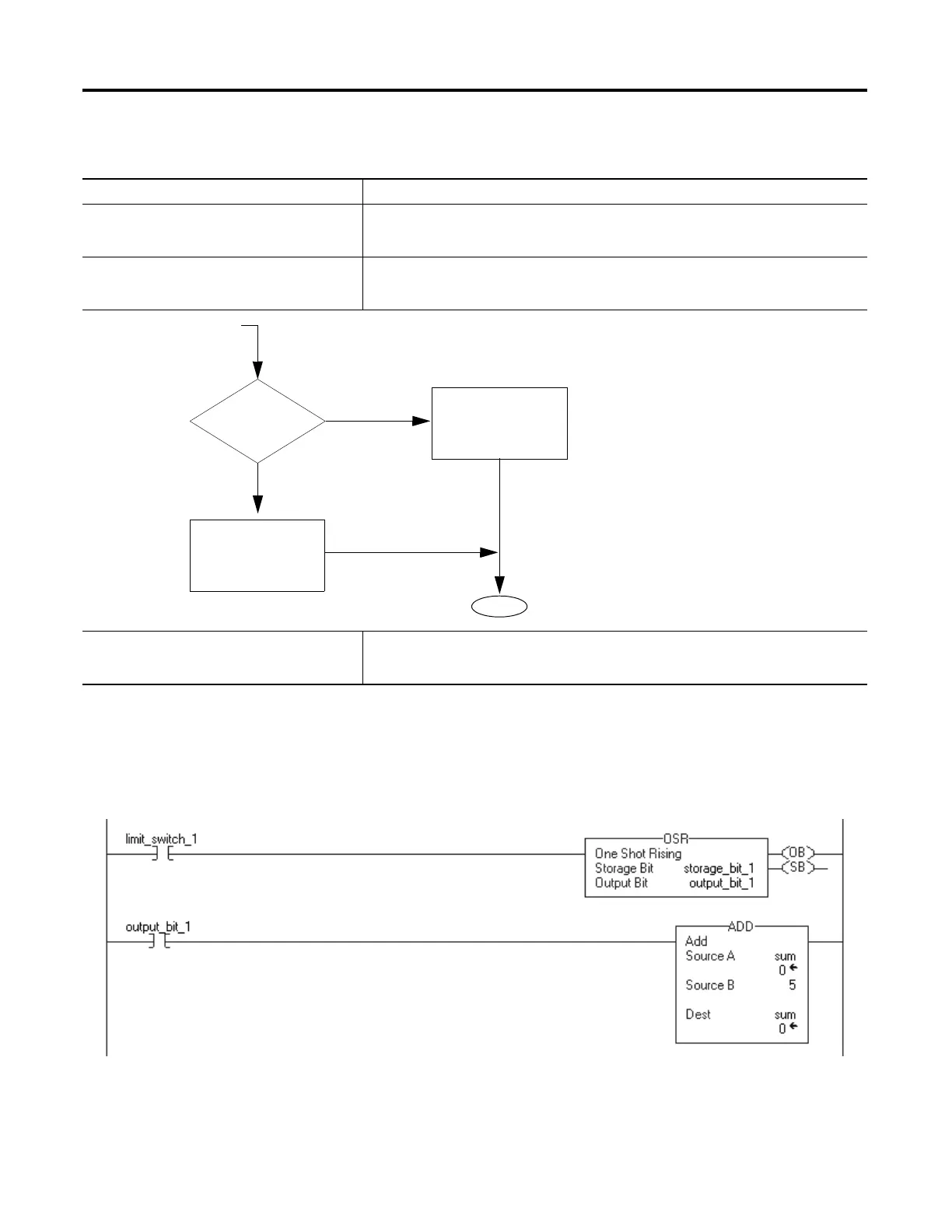

Rung-condition-in is true.

End

Examine

storage bit.

Storage Bit = 0

Storage Bit = 1

Storage bit is set.

Output bit is set.

Rung-condition-out

is set to true.

Storage bit remains set.

Output bit is cleared.

Rung-condition-out is

set to true.

Loading...

Loading...