Rockwell Automation Publication 1756-RM003N-EN-P - October 2011 411

Array (File)/Shift Instructions (BSL, BSR, FFL, FFU, LFL, LFU) Chapter 9

CONTROL Structure

Description: Use the FFL instruction with the FFU instruction to store and retrieve data in a

first-in/first-out order. When used in pairs, the FFL and FFU instructions

establish an asynchronous shift register.

Typically, the Source and the FIFO are the same data type.

When enabled, the FFL instruction loads the Source value into the position in

the FIFO identified by the .POS value. The instruction loads one value each time

the instruction is enabled, until the FIFO is full.

Arithmetic Status Flags: Not affected

Fault Conditions:

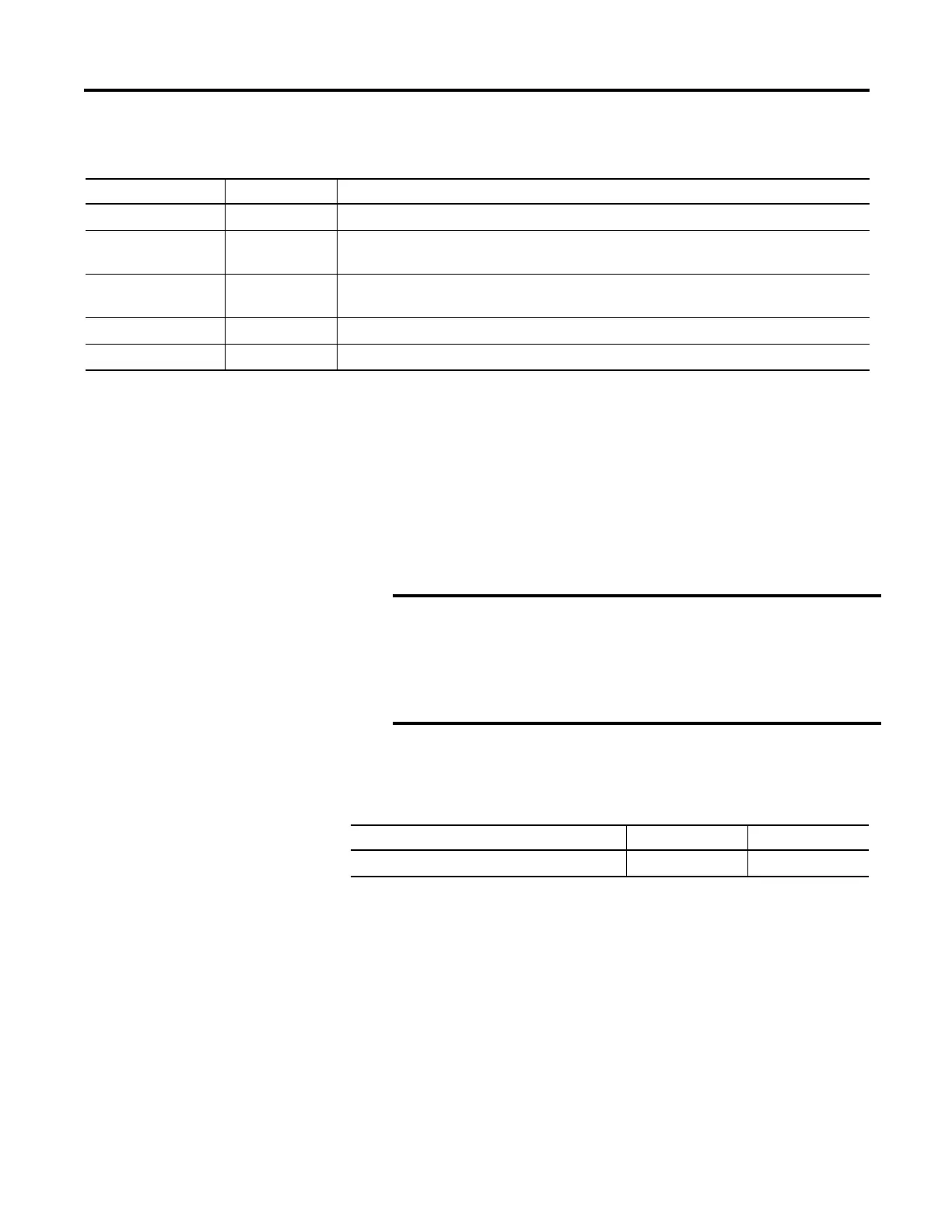

Mnemonic Data Type Description

.EN BOOL The enable bit indicates that the FFL instruction is enabled.

.DN BOOL The done bit is set to indicate that the FIFO is full (.POS = .LEN). The .DN bit inhibits loading

the FIFO until .POS < .LEN.

.EM BOOL The empty bit indicates that the FIFO is empty. If .LEN ≤ 0 or .POS < 0, both the .EM bit and

.DN bit are set.

.LEN DINT The length specifies the maximum number of elements the FIFO can hold at one time.

.POS DINT The position identifies the location in the FIFO where the instruction will load the next value.

You must test and confirm that the instruction doesn’t

change data that you don’t want it to change.

The FFL instruction operates on contiguous memory. In

some cases, the instruction loads data past the array into

other members of the tag. This happens if the length is too

big and the tag is a user-defined data type.

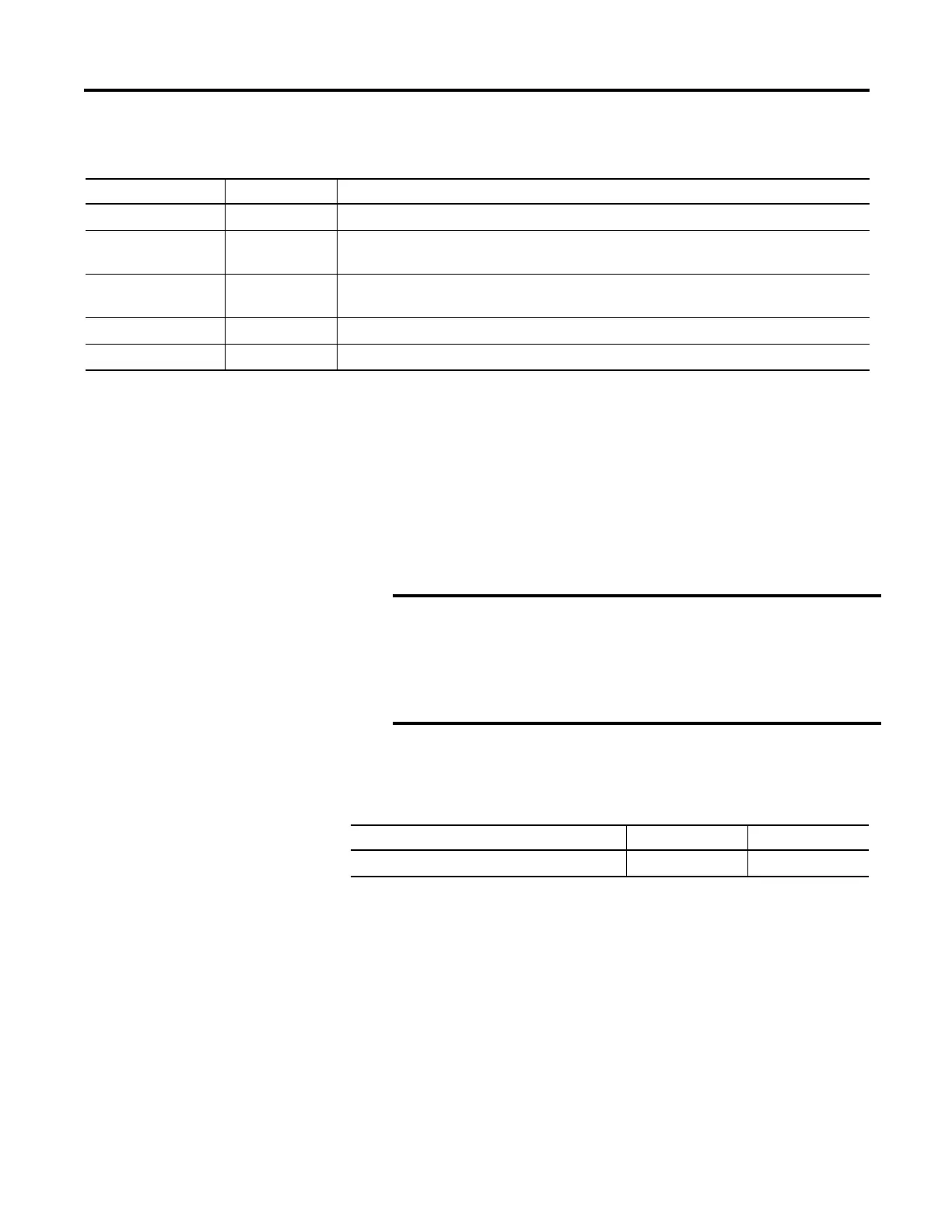

A major fault will occur if Fault type Fault code

(starting element + .POS) > FIFO array size 4 20

Loading...

Loading...