• SMBus Interface (p. 34)

• PLL Interface (p. 35)

• AMD PowerXpress Interface (p. 36)

• Power and Ground Descriptions and Operating Conditions (p. 36)

• Configuration Straps (p. 37)

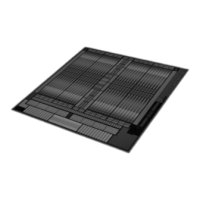

3.1 Pin Assignments

Table 3–1 Pin Assignments (Left Half)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

A

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

B RSVD

DFTIO_2

9

VSS

DFTIO_4

4

DFTIO_3

1

DFTIO_4

8

VSS

DFTIO_5

8

DFTIO_6

8

VDDCR_

SOC

VSS RSVD

DFTIO_8

6

DFTIO_9

1

VDDCR_

SOC

DFTIO_9

7

DFTIO_1

07

DFTIO_1

09

VDDCR_

SOC

DFTIO_1

12

DFTIO_1

20

DFTIO_1

21

VDDCR_

SOC

C

DFTIO_1

7

DFTIO_9

DFTIO_2

1

DFTIO_2

2

VSS

DFTIO_3

2

DFTIO_4

9

DFTIO_5

2

VSS

DFTIO_7

5

DFTIO_8

7

RSVD VSS

DFTIO_7

4

DFTIO_8

2

DFTIO_8

5

VSS

DFTIO_9

6

DFTIO_1

02

DFTIO_1

04

VSS

DFTIO_1

15

DFTIO_1

19

D VSS

DFTIO_1

8

DFTIO_2

7

DFTIO_1

3

DFTIO_3

3

DFTIO_3

9

VSS

DFTIO_3

6

DFTIO_4

7

DFTIO_7

0

VSS RSVD

DFTIO_6

5

DFTIO_7

7

VDDCR_

SOC

DFTIO_9

2

DFTIO_1

01

DFTIO_1

05

VDDCR_

SOC

DFTIO_1

08

DFTIO_1

10

DFTIO_1

16

VDDCR_

SOC

E VSS DFTIO_5 DFTIO_2 VSS

DFTIO_1

2

DFTIO_1

6

DFTIO_3

4

VSS

DFTIO_6

4

DFTIO_5

6

DFTIO_5

5

VSS

DFTIO_6

2

DFTIO_7

9

DFTIO_8

4

VSS

DFTIO_9

4

DFTIO_1

11

DFTIO_1

17

VSS

DFTIO_1

06

DFTIO_1

26

F VSS

TXCFP_D

PF3P

TXCFM_

DPF3N

VSS

DDC1DA

TA

DDC1CL

K

VSS

DFTIO_2

5

DFTIO_5

3

DFTIO_3

8

VSS

DFTIO_4

6

DFTIO_5

0

DFTIO_6

1

VDDCR_

SOC

DFTIO_8

9

DFTIO_9

5

DFTIO_1

03

VDDCR_

SOC

DFTIO_1

27

DFTIO_1

38

DFTIO_1

22

VDDCR_

SOC

G

TX0P_DP

F2P

TX0M_D

PF2N

VSS AUX1P AUX1N VSS HPD1

DFTIO_2

8

VSS

DFTIO_4

2

DFTIO_5

7

DFTIO_4

5

VSS

DFTIO_6

3

DFTIO_8

3

DFTIO_8

0

VSS

DFTIO_7

6

DFTIO_8

8

DFTIO_9

8

VSS

DFTIO_8

1

DFTIO_1

14

H VSS

TX1P_DP

F1P

TX1M_D

PF1N

VSS

VDDAN_

33

VDDAN_

33

VSS

DFTIO_2

0

DFTIO_4

3

DFTIO_3

0

VSS

DFTIO_5

9

DFTIO_6

9

DFTIO_7

3

VDDCR_

SOC

DFTIO_6

0

DFTIO_7

1

DFTIO_6

7

VDDCR_

SOC

DFTIO_6

6

DFTIO_7

2

DFTIO_7

8

VDDCR_

SOC

J

TX2P_DP

F0P

TX2M_D

PF0N

VSS

DDC2DA

TA

DDC2CL

K

VSS DFTIO_0

DFTIO_2

6

VSS

DFTIO_3

5

DFTIO_3

7

DFTIO_4

1

VDDCR_

SOC

DFTIO_4

0

DFTIO_5

4

DFTIO_5

1

VDDCR_

SOC

DFTIO_9

0

DFTIO_1

00

DFTIO_9

9

VDDCR_

SOC

DFTIO_1

25

DFTIO_1

50

K VSS AUX2P AUX2N VSS

GENERIC

C_HPD2

VDDAN_

33

VSS

DFTIO_2

3

DFTIO_1

4

DFTIO_1

9

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

L

TXCEP_D

PE3P

TXCEM_

DPE3N

VSS RSVD VSS

VDDAN_

33

DFTIO_7 DFTIO_3 VSS

DFTIO_2

4

DFTIO_1 VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

M VSS

TX3P_DP

E2P

TX3M_D

PE2N

VSS

VDDAN_

18

VDDAN_

18

VSS

DFTIO_1

1

DFTIO_6 DFTIO_4 VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

N

TX4P_DP

E1P

TX4M_D

PE1N

VSS

VDDAN_

18

VSS

VDDAN_

18

RSVD DFTIO_8 VSS

DFTIO_1

0

RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

P VSS

TX5P_DP

E0P

TX5M_D

PE0N

VSS

AUX_ZVS

S

GENERIC

D_HPD3

VSS RSVD

DFTIO_1

5

RSVD VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

R

TXCDP_

DPD3P

TXCDM_

DPD3N

VSS

DDCAUX

3P

DDCAUX

3N

VSS

GENLK_C

LK

GENLK_V

SYNC

VSS RSVD RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

T VSS

TX0P_DP

D2P

TX0M_D

PD2N

VSS

SWAPLO

CKA

SWAPLO

CKB

VSS GPIO_0

GPIO_SV

D0

RSVD VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

U

TX1P_DP

D1P

TX1M_D

PD1N

VSS RSVD RSVD VSS GPIO_1

GPIO_SV

T0

VSS RSVD RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

V VSS

TX2P_DP

D0P

TX2M_D

PD0N

VSS

GENERIC

E_HPD4

GPIO_9_

ROMSO

GPIO_2 VSS

GPIO_SV

C0

INTCRAC

KMONGL

L

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

W

TXCCP_D

PC3P

TXCCM_

DPC3N

VSS

DDCAUX

4P

DDCAUX

4N

VSS

GPIO_7_

ROMSCK

GPIO_8_

ROMSI

VSS RSVD RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

Y VSS

TX3P_DP

C2P

TX3M_D

PC2N

VSS VDD_18 VDD_18

GPIO_10

_ROMCS

B

VSS RSVD

INTCRAC

KMONGL

R

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

AA

TX4P_DP

C1P

TX4M_D

PC1N

VSS RSVD VDD_18 VSS RSVD TRST_L VSS RSVD RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

AB VSS

TX5P_DP

C0P

TX5M_D

PC0N

VSS VDD_18 VDD_18 VSS TDO TDI RSVD VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS

AC

TXCBP_D

PB3P

TXCBM_

DPB3N

VSS

GENERIC

F_HPD5

VSS VDD_18 TMS TCK VSS RSVD RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

AD VSS

TX0P_DP

B2P

TX0M_D

PB2N

VSS

DDCAUX

5P

DDCAUX

5N

VSS TESTEN XTRIG6 RSVD VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

AE

TX1P_DP

B1P

TX1M_D

PB1N

VSS

GENERIC

G_HPD6

VSS VDD_18 GPIO_5 GPIO_6 VSS

INTCRAC

KMONDA

RSVD VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS VSS VSS VSS

AF VSS

TX2P_DP

B0P

TX2M_D

PB0N

VSS

DDCAUX

6P

DDCAUX

6N

VSS

VDDAN_

Q_EFUSE

VDDAN_

Q_EFUSE

RSVD VSS VSS VSS VSS VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VSS VSS VSS VSS VSS

AG

TXCAP_D

PA3P

TXCAM_

DPA3N

VSS VDD_18 VDD_18 DP_ZVSS GPIO_4 GPIO_3 XTRIG7

VDDCR_

BACO

VDDCR_

BACO

VSS VSS VSS VSS VSS

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

AH VSS

TX3P_DP

A2P

TX3M_D

PA2N

VSS VDD_18

DP_ZVD

D_08

VSS VSS

VDDCR_

BACO

VDDCR_

BACO

VSS VSS VSS VSS VSS VSS

FB_VDD

CR_SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

VDDCR_

SOC

AJ

TX4P_DP

A1P

TX4M_D

PA1N

VSS RSVD RSVD VSS

ANALOGI

O

RSVD VSS RSVD TEST_PG VSS VSS RSVD

HBMA_D

AP_49

FB_VSS_

A

HBMA_D

AP_32

HBMA_D

AP_28

VSS

HBMA_D

AP_12

HBMA_D

AP_7

VSS

HBMA_D

AP_17

AK VSS

TX5P_DP

A0P

TX5M_D

PA0N

VSS

PCIE_ZV

SS

VSS RSVD

VDD_08

0_EFUSE

VDD_08

0_EFUSE

RSVD VSS VSS VSS

HBMA_D

AP_59

HBMA_D

AP_46

FB_VDD

CI_MEM

HBMA_D

AP_38

VSS

HBMA_D

AP_23

HBMA_D

AP_21

VSS

HBMA_D

AP_14

HBMA_D

AP_19

AL VSS

GENERIC

A

VSS GPIO_11 GPIO_12 RSVD

VDD_08

0

RSVD VSS TS_A RSVD VSS VSS

HBMA_D

AP_58

RSVD VSS

VDDCI_M

EM

HBMA_D

AP_26

HBMA_D

AP_41

VDDCI_M

EM

HBMA_D

AP_13

HBMA_D

AP_11

VDDCI_M

EM

AM XTALIN VSS

XTALOU

T

VSS GPIO_14 GPIO_13 VSS

VDD_08

0

DBREQ_

L

SDA VSS VSS VSS RSVD MTESTA VSS

HBMA_D

AP_39

HBMA_D

AP_40

VDDCI_M

EM

HBMA_D

AP_27

HBMA_D

AP_22

VDDCI_M

EM

HBMA_D

AP_35

AN RSVD RSVD RSVD RSVD RSVD RSVD VSS RSVD VSS SCL RSVD RSVD VSS RSVD

HBMA_D

AP_52

VSS

HBMA_D

AP_51

VSS

HBMA_D

AP_50

HBMA_D

AP_34

VSS

HBMA_D

AP_15

HBMA_D

AP_42

AP

OSC_GAI

N0

OSC_GAI

N1

OSC_GAI

N2

RSVD RSVD RSVD VSS

VDD_08

0

RSVD RSVD VSS VSS VSS

HBMA_D

AP_53

HBMA_D

AP_56

VDDIO_

MEM

VSS

VDDCR_

HBM

VDDCR_

HBM

VSS

VDDCR_

HBM

VDDCR_

HBM

VSS

AR BP_0 BP_1 VSS GPIO_15 GPIO_16 GPIO_17 VSS RSVD VSS RSVD RSVD VSS VSS

HBMA_D

AP_57

VREFEXT

A

VSS

HBMA_D

AP_43

HBMA_D

AP_54

VDDIO_

MEM

HBMA_D

AP_31

HBMA_D

AP_44

VDDIO_

MEM

HBMA_D

AP_36

AT BP_3 BP_2 VSS GPIO_18 GPIO_19 GPIO_20 VSS

VDD_08

0

RSVD RSVD VSS

MACO_E

N

VSS

HBMA_D

AP_55

VSS

VDDCR_

HBM

VDDIO_

MEM

VDDIO_

MEM

HBMA_D

AP_48

HBMA_D

AP_47

VDDIO_

MEM

HBMA_D

AP_45

HBMA_D

AP_37

AU RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD VSS RSVD VSS VSS

BL_ENAB

LE

RSVD PX_EN VSS

VDDCR_

HBM

VDDIO_

MEM

VSS

VDDCR_

HBM

VDDCR_

HBM

VSS

AV RSVD RSVD RSVD

VDD_08

0

VSS VSS

VDD_08

0

RSVD VSS

VDD_08

0

VSS RSVD RSVD

GENERIC

B

TEST_PG

_BACO

BL_PWM

_DIM

DIGON RSVD RSVD RSVD RSVD RSVD RSVD

AW RSVD RSVD

VDD_08

0

VSS VSS

VDD_08

0

RSVD VSS

VDD_08

0

RSVD VSS RSVD RSVD VSS RSVD RSVD VSS VSS VSS VSS VSS VSS RSVD

AY

PINSTRA

P_7

PINSTRA

P_6

PINSTRA

P_5

VSS

PCIE_RE

FCLKP

PCIE_RE

FCLKN

VSS

PCIE_TX

2P

PCIE_TX

2N

VSS

PCIE_TX

5P

PCIE_TX

5N

VSS

PCIE_TX

8P

PCIE_TX

8N

VSS

PCIE_TX

11P

PCIE_TX

11N

VSS

PCIE_TX

14P

PCIE_TX

14N

VSS RSVD

BA

PINSTRA

P_4

PINSTRA

P_3

RSVD VSS VSS

PCIE_TX

1P

PCIE_TX

1N

VSS

PCIE_TX

4P

PCIE_TX

4N

VSS

PCIE_TX

7P

PCIE_TX

7N

VSS

PCIE_TX

10P

PCIE_TX

10N

VSS

PCIE_TX

13P

PCIE_TX

13N

VSS VSS RSVD

BB

PINSTRA

P_2

PINSTRA

P_1

PINSTRA

P_0

VSS VSS

PCIE_TX

0P

PCIE_TX

0N

VSS

PCIE_TX

3P

PCIE_TX

3N

VSS

PCIE_TX

6P

PCIE_TX

6N

VSS

PCIE_TX

9P

PCIE_TX

9N

VSS

PCIE_TX

12P

PCIE_TX

12N

VSS

PCIE_TX

15P

PCIE_TX

15N

VSS

BC SMBDAT SMBCLK RSVD VSS

PCIE_RX

0P

PCIE_RX

0N

VSS

PCIE_RX

3P

PCIE_RX

3N

VSS

PCIE_RX

6P

PCIE_RX

6N

VSS

PCIE_RX

9P

PCIE_RX

9N

VSS

PCIE_RX

12P

PCIE_RX

12N

VSS

PCIE_RX

15P

PCIE_RX

15N

VSS RSVD

BD VSS WAKEB PERSTB RSVD VSS VSS

PCIE_RX

2P

PCIE_RX

2N

VSS

PCIE_RX

5P

PCIE_RX

5N

VSS

PCIE_RX

8P

PCIE_RX

8N

VSS

PCIE_RX

11P

PCIE_RX

11N

VSS

PCIE_RX

14P

PCIE_RX

14N

VSS RSVD VSS

BE VSS

CLKREQ

B

VSS

PCIE_RX

1P

PCIE_RX

1N

VSS

PCIE_RX

4P

PCIE_RX

4N

VSS

PCIE_RX

7P

PCIE_RX

7N

VSS

PCIE_RX

10P

PCIE_RX

10N

VSS

PCIE_RX

13P

PCIE_RX

13N

VSS VSS REFCLKP REFCLKN

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

20 Signal Descriptions

"Vega 10" Databook

56006_1.00

© 2017 Advanced Micro Devices, Inc.

AMD Confidential - Do not duplicate.