2. VME Interface

The V2718 provides all of the addressing and data transfer modes documented in the

VME64 specification (except A64 and those intended to improve 3U applications, i.e. A40

and MD32). The V2718 is also compatible with all VME bus modules compliant to pre-

VME64 specifications. As VME bus master, the V2718 supports Read-Modify-Write

(RMW), and Address-Only-with-Handshake (ADOH) but does not accept RETRY* as a

termination from the VME bus slave. The ADOH cycle is used to implement the VME bus

Lock command allowing the PC Host to lock VME bus resources.

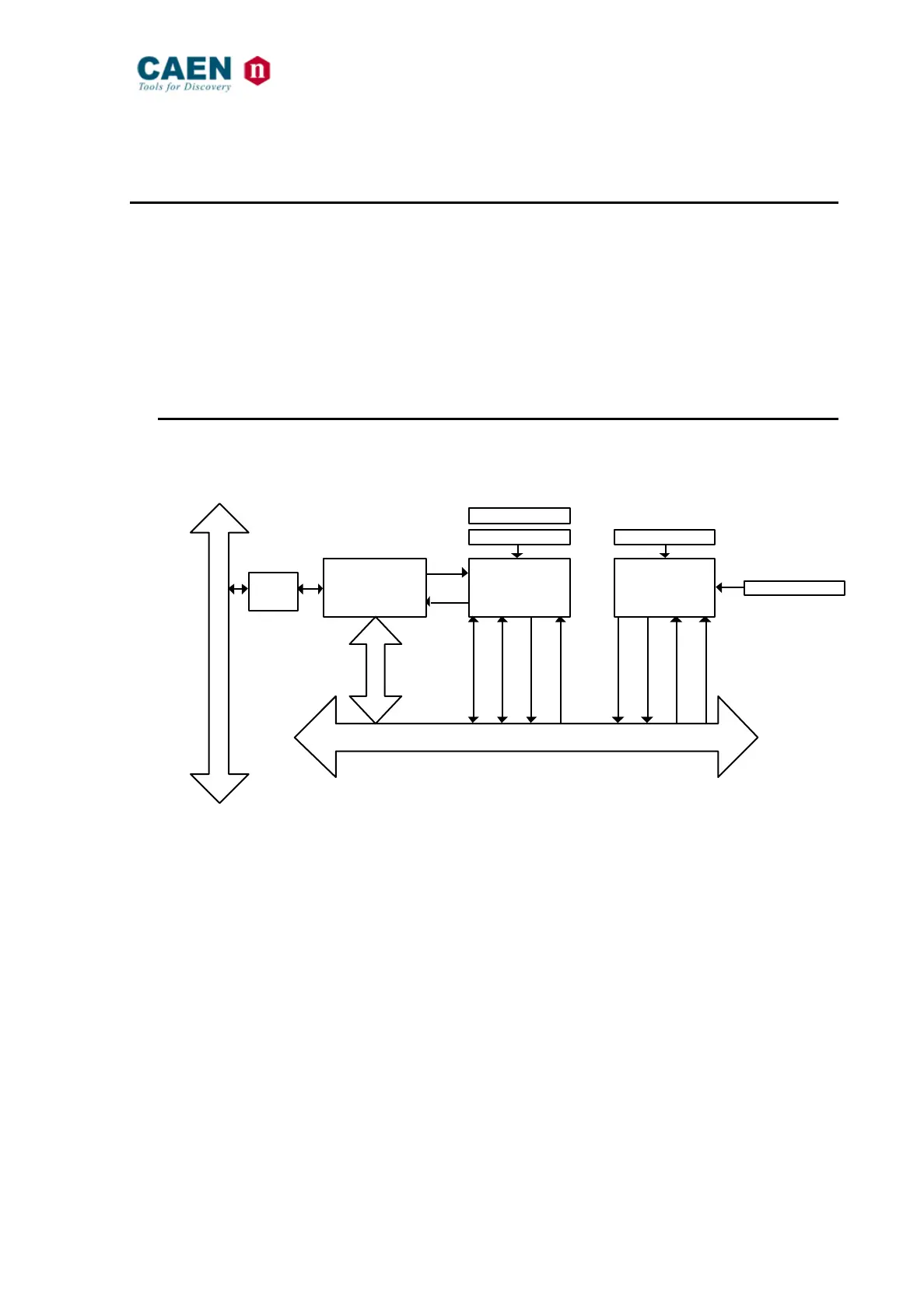

2.1. VME bus Requester

Fig. 3: Internal Arbitration for VME bus Requests

When the V2718 operates as VME bus Requester, the functional sequence is the

following:

− The PCI bus sends a VME bus access request

− The Master asserts DWB (Device Want Bus), and waits for DGB (Device Grant Bus)

− The Requester requests the bus to the Arbiter, via VME (whether the Arbiter is the

V2718 itself or not); when the Arbiter has granted the bus, the Requester asserts

DGB and BBSY (on the bus)

− The Master performs the the VME cycle, then releases DWB

− If REL_TYPE is RWD (Release When Done), then the Requester releases BBSY

Loading...

Loading...