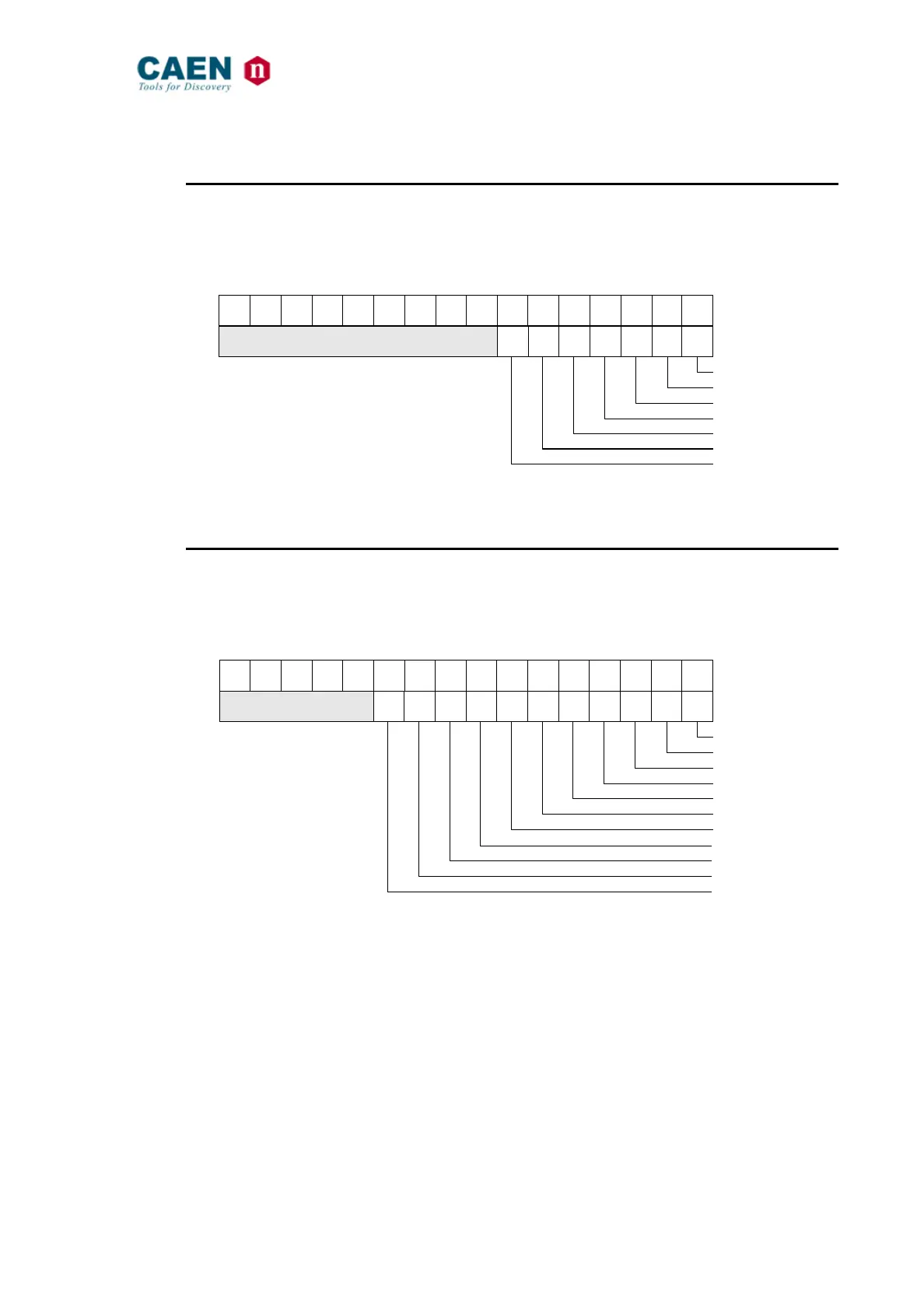

2.13.8. Input register

(Base Address + 0x08, D16, read/write)

This register carries the input register pattern.

Fig. 11: Input register

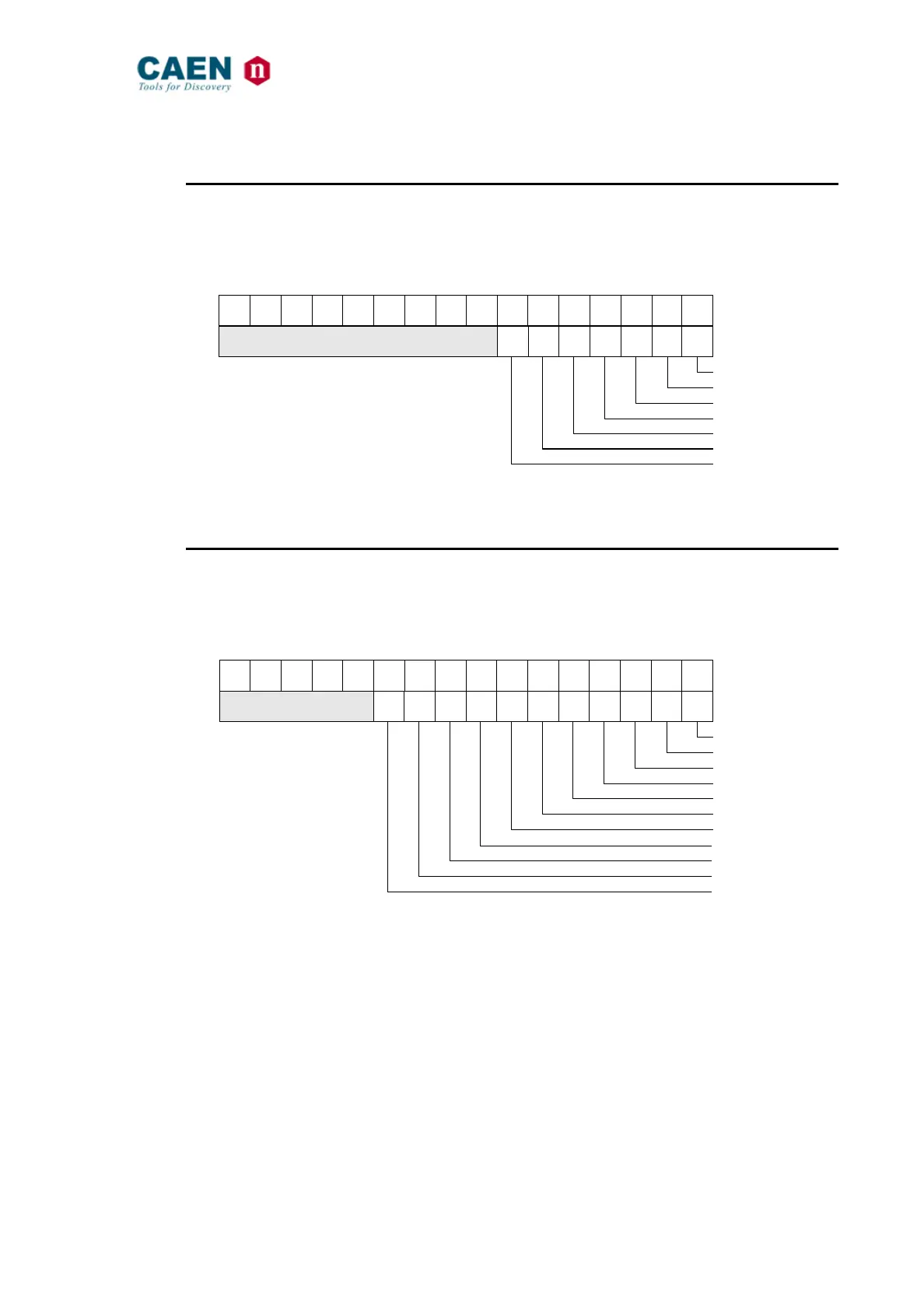

2.13.9. Output set register

(Base Address + 0x0A, D16, read/write)

This register allows to set the output register pattern: 1 = set; 0 = leave previous setting

Fig. 12: Output set register

Loading...

Loading...