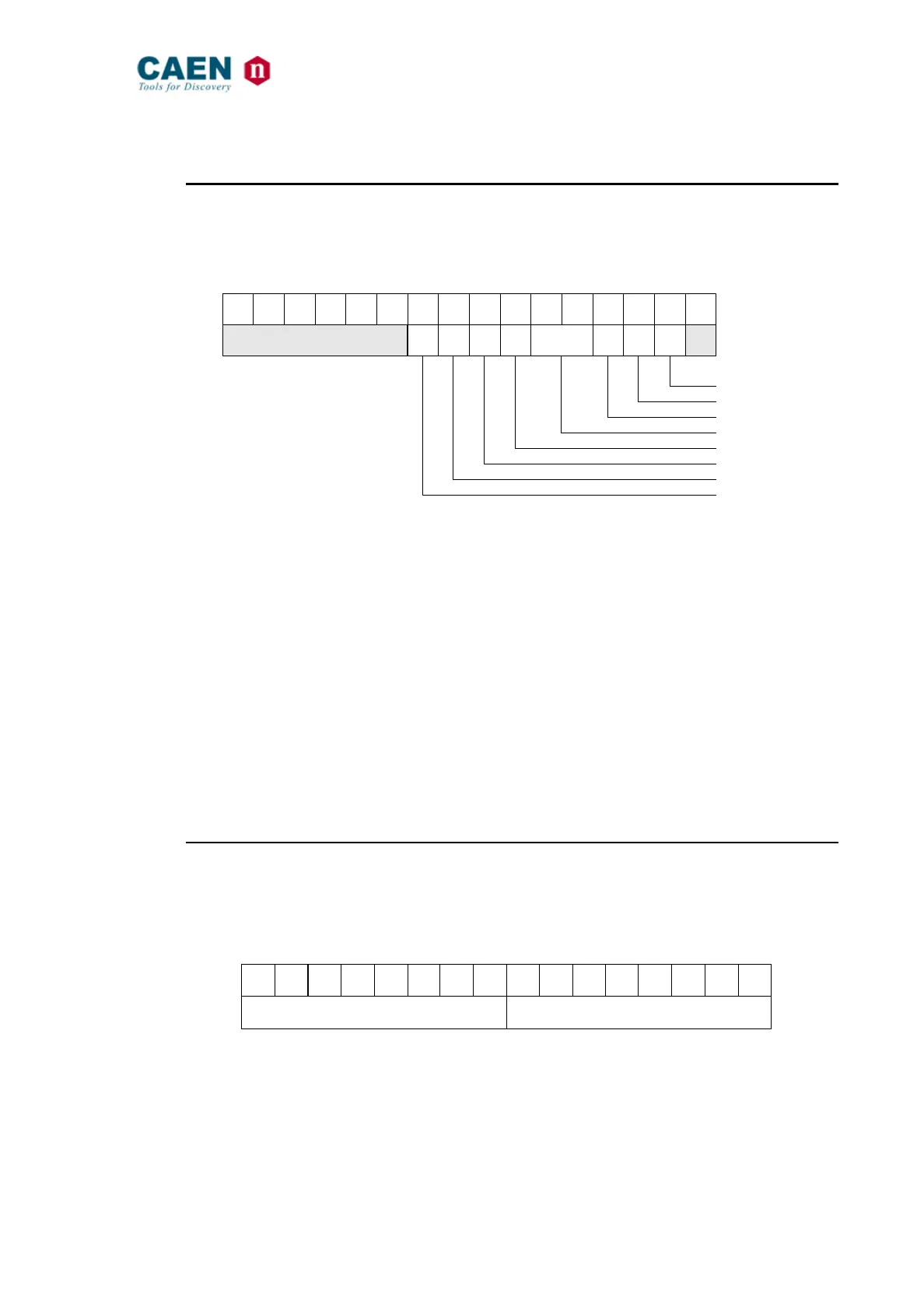

2.13.2. Control register

(Base Address + 0x01, D16, read/write)

This register allows performing some general settings of the module.

Fig. 7: Control Register

Arbiter Type: 0 = Fixed Priority

1 = Round Robin

Requester Type: 0 = Fair

1 = Demand

Release Type: 0 = Release when done

1 = Release on request

Bus Timeout: 0 = 50 µs

1 = 1400 µs

Address Increment: 0 = Enabled

1 = Disabled (FIFO mode)

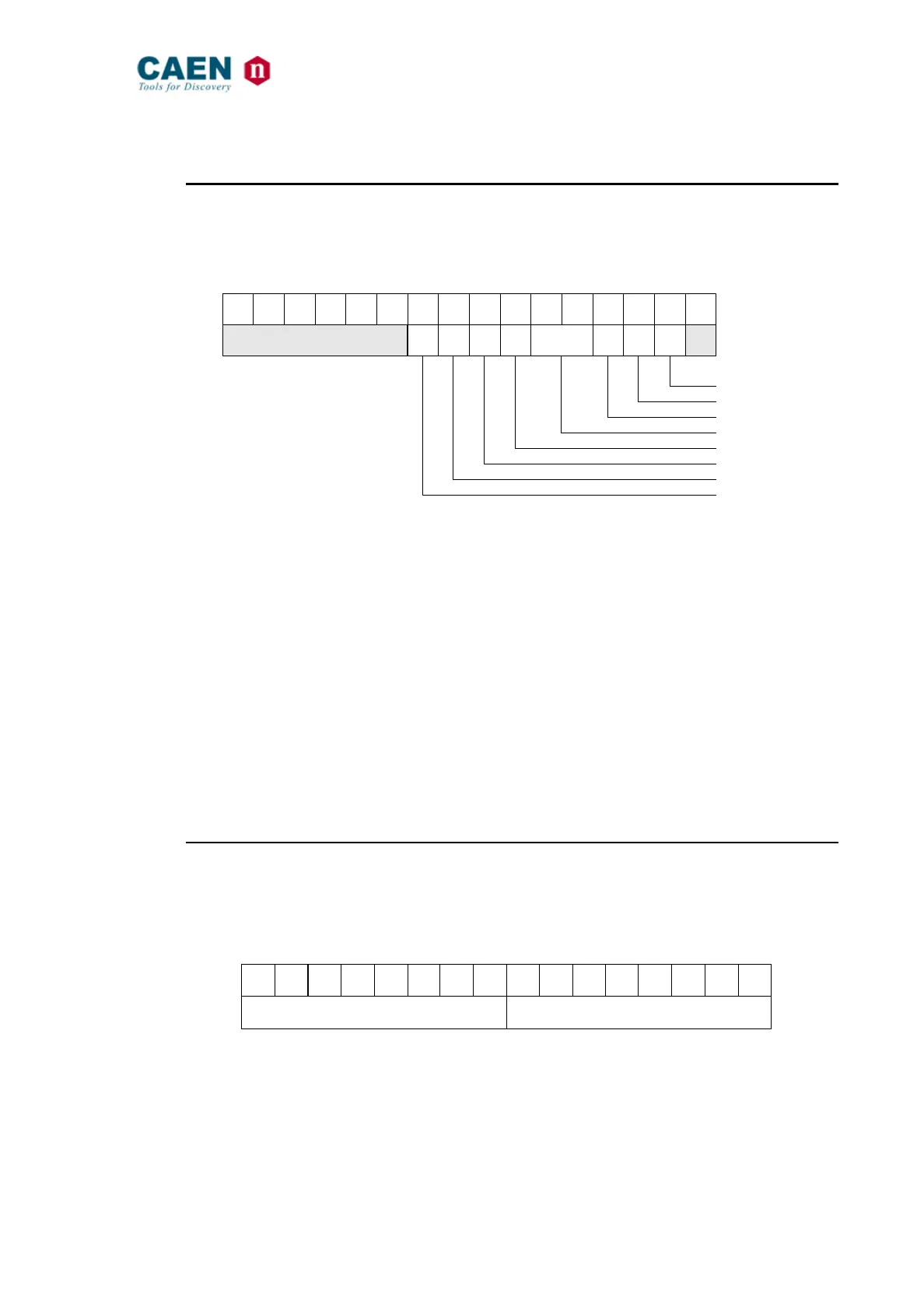

2.13.3. Firmware Revision register

(Base Address + 0x02, D16, read only)

This register contains the firmware revision number coded on 16 bit. For example the

REV. X.Y would feature:

Fig. 8: Firmware Revision Register

Loading...

Loading...