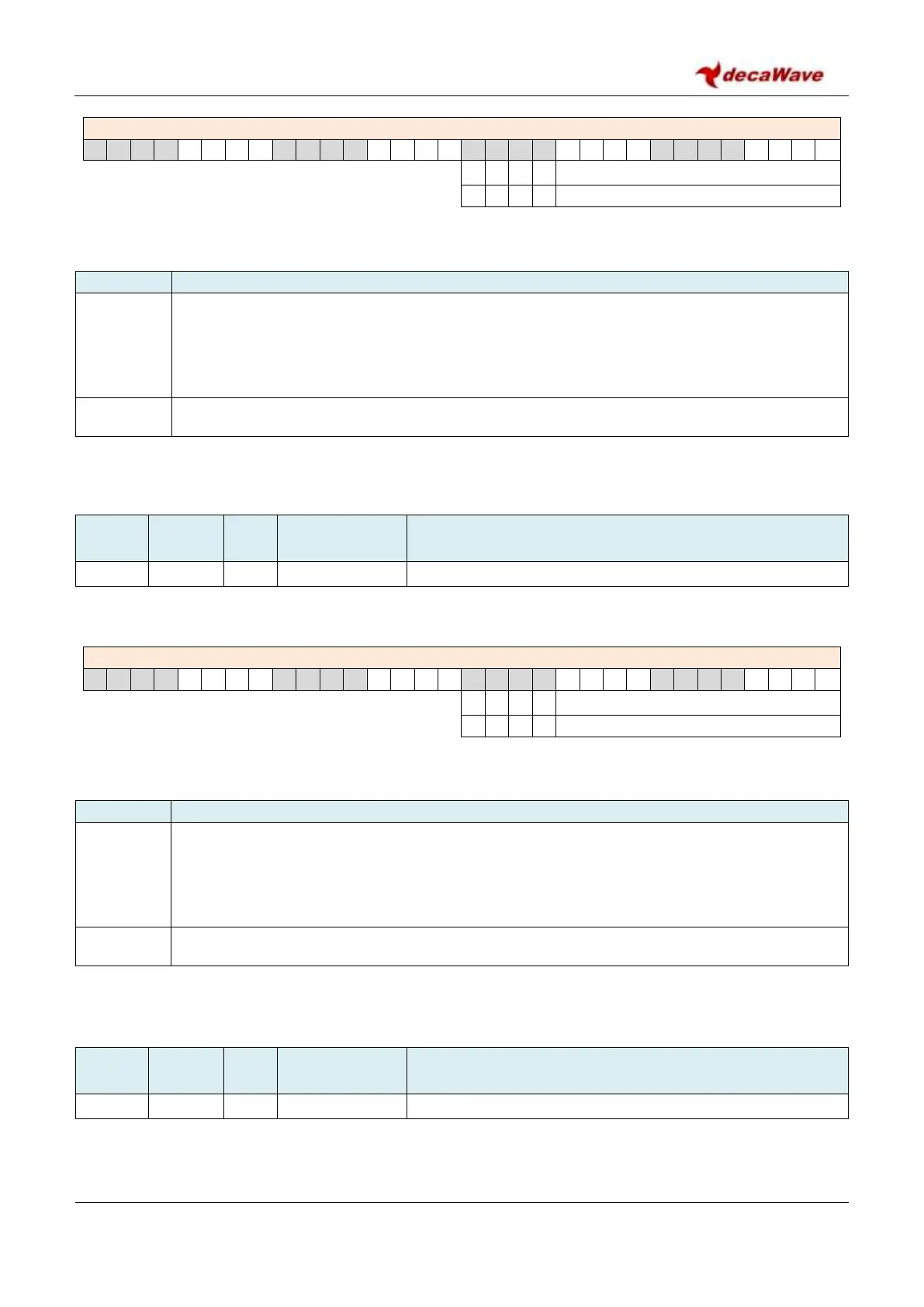

REG:2F:14 – EVC_FWTO – RX Frame Wait Timeout Event Counter

The bits of the EVC_FWTO register are described below:

Description of fields within Sub-Register 0x2F:14 – RX Frame Wait Timeout Event Counter

EVC_FWTO

reg:2F:14

bits:11–0

RX Frame Wait Timeout Event Counter. The EVC_FWTO field is a 12-bit counter of receive

frame wait timeout events. This is essentially a count of the reporting of the RXRFTO events in

Register file: 0x0F – System Event Status Register.

NB: For this counter to be active, counting needs to be enabled by the setting the EVC_EN bit

in Sub-Register 0x2F:00 – Event Counter Control.

The remaining bits of this register are reserved.

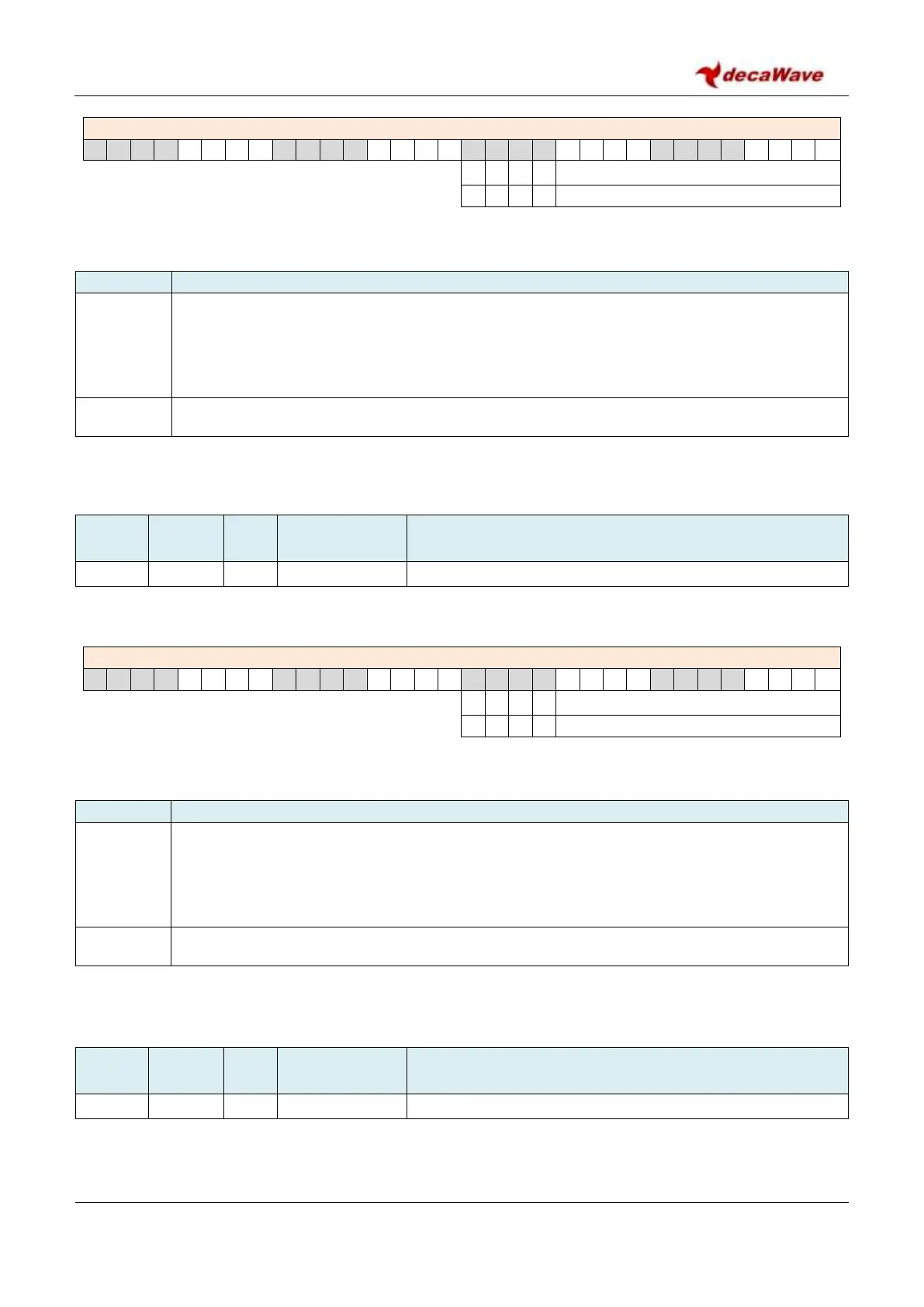

7.2.48.11 Sub-Register 0x2F:16 – TX Frame Sent Counter

Register file: 0x2F – Digital Diagnostics Interface, sub-register 0x16 is the TX Frame Sent Counter.

REG:2F:16 – EVC_TXFS – TX Frame Sent Counter

The bits of the EVC_TXFS register are described below:

Description of fields within Sub-Register 0x2F:16 – TX Frame Sent Counter

EVC_TXFS

reg:2F:16

bits:11–0

TX Frame Sent Event Counter. The EVC_TXFS field is a 12-bit counter of transmit frames sent.

This is incremented every time a frame is sent. It is essentially a count of the reporting of the

TXFRS events in Register file: 0x0F – System Event Status Register.

NB: For this counter to be active, counting needs to be enabled by the setting the EVC_EN bit

in Sub-Register 0x2F:00 – Event Counter Control.

The remaining bits of this register are reserved.

7.2.48.12 Sub-Register 0x2F:18 – Half Period Warning Counter

Half Period Warning Counter

Register file: 0x2F – Digital Diagnostics Interface, sub-register 0x18 is the Half Period Warning Counter.

Loading...

Loading...