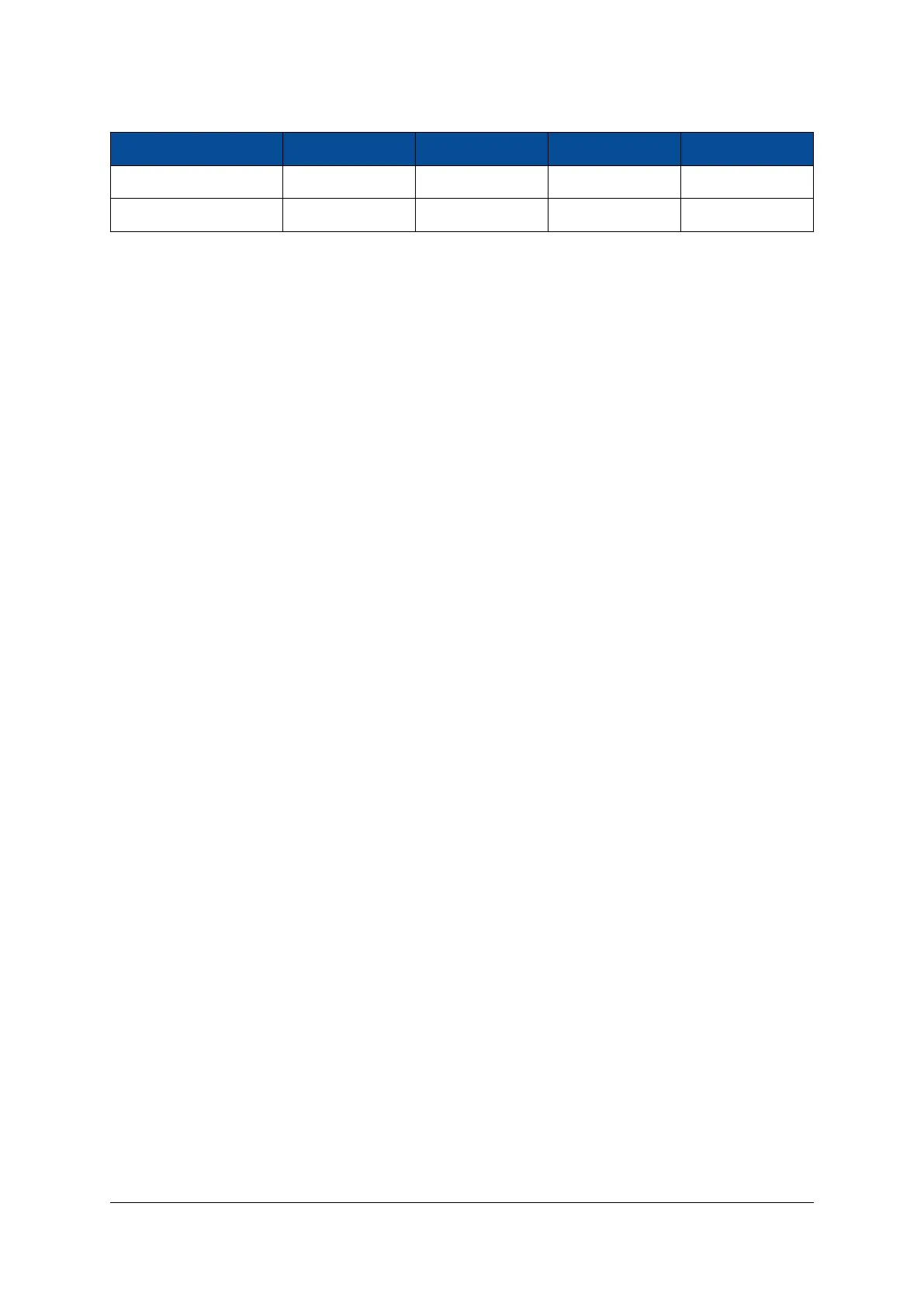

Parameter Byte 3 Byte 2 Byte 1 Byte 0

DQS to clock delay (ns) 0.061 0.043 0.000 -0.032

Board delay (ns) 0.243 0.255 0.272 0.285

Table 23: DDR3 (PS) Board Timing

2.15.5 DDR3 Low Voltage Operation

The default voltage of the DDR3 is 1.5 V. In order to enable low voltage mode (1.35 V), DDR3_VSEL (pin AD10)

must be driven logic 0, DDR3L memory type must be selected in the PS configuration parameters and a

memory voltage of 1.35 V must be selected in the Memory Interface Generator (MIG) parameters in Vivado.

For 1.5 V operation, DDR3_VSEL must be set to high impedance (not driven logic 1).

Note that the configuration for the DDR3_VSEL pin affects both memory channels (DDR3 SDRAM PS and PL).

On Mercury ZX1 SoC modules revision 1 the Fast Ethernet ports are not enabled when DDR3 SDRAM is

operated in low power mode. This is because the Ethernet ports are fed by the same supply as the DDR3

memory and require a voltage of 1.5 V to work properly. This issue has been fixed for modules from revision

2 and newer.

2.16 DDR3 SDRAM (PL)

The DDR3 SDRAM connected to the PL on the Mercury ZX1 SoC module is operated at 1.35 V (low power

mode) or at 1.5 V, depending on a selection signal. The DDR bus width is 16-bit.

The DDR3 SDRAM memory connected to the PL supports different bandwidths depending on the equipped

SoC device:

• FBG package, speedgrade 1: up to 800 Mbit/s (400 MHz)

• FBG package, speedgrade 2: up to 1066 Mbit/s (533 MHz)

• FFG package, speedgrade 1 and 2: up to 1600 Mbit/s (800 MHz)

Hence, the maximum memory bandwidth on the Mercury ZX1 SoC module for the DDR3 SDRAM (PL) is:

• FBG package, speedgrade 1: 800 Mbit/s × 16 bit = 1600 MB/sec

• FBG package, speedgrade 2: 1066 Mbit/s × 16 bit = 2133 MB/sec

• FFG package, speedgrade 1 and 2: 1600 Mbit/s × 16 bit = 3200 MB/sec

For DDR3 low power mode (DDR3L) the speed can be lower than mentioned above. Details are available in

the Zynq DC and AC Switching Characteristics document [23].

2.16.1 DDR3 SDRAM Type

Table 24 describes the memory availability and configuration on the Mercury ZX1 SoC module.

D-0000-403-002 31 / 56 Version 05, 25.07.2019

Loading...

Loading...