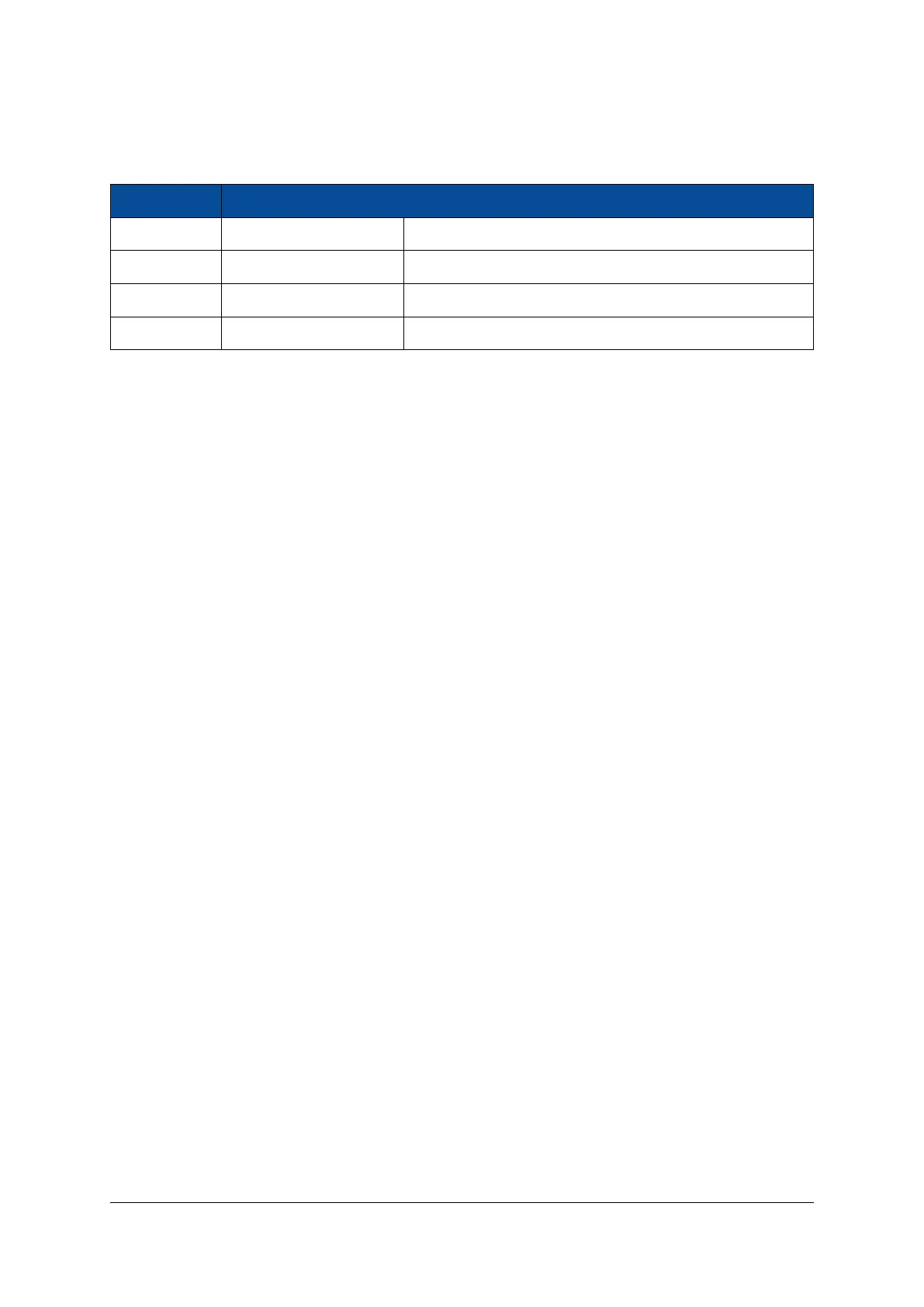

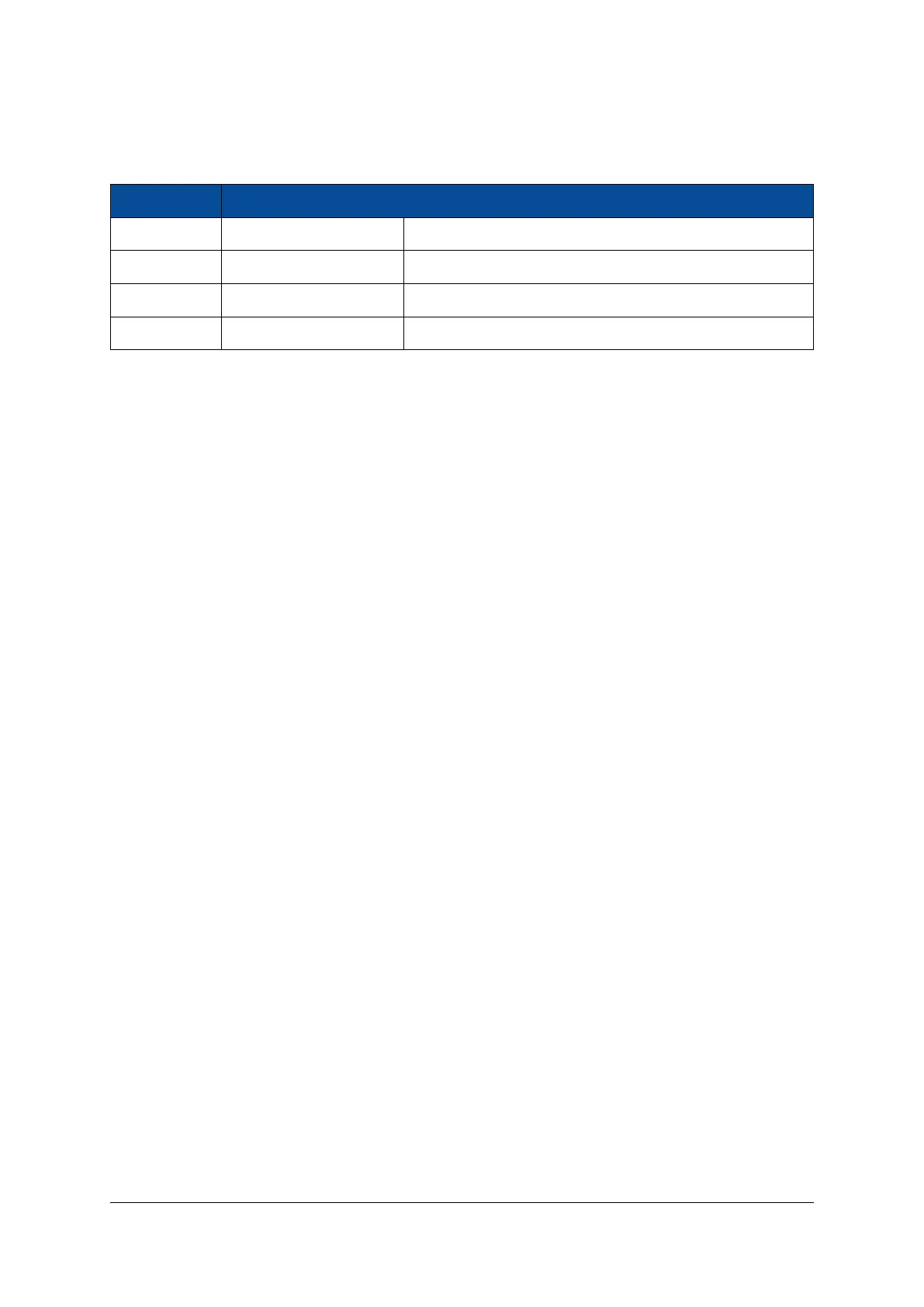

3.4.1 JTAG on Module Connector

Signal Name Module Connector Pin Resistor

JTAG_TCK A-123 10 kΩ pull-up to VCC_CFG_MIO_B12

JTAG_TMS A-119 SoC internal pull-up

JTAG_TDI A-117 SoC internal pull-up

JTAG_TDO A-121 -

Table 39: JTAG Interface

3.4.2 External Connectivity

JTAG signals can be connected directly on the base board to a JTAG connector. No pull-up/pull-down re-

sistors are necessary. The VREF pin of the programmer must be connected to VCC_CFG_MIO_B12.

It is recommended to add 22 Ω series termination resistors between the module and the JTAG header, close

to the source. Please refer to the Enclustra Module Pin Connection Guidelines for details on JTAG interface.

3.5 QSPI Boot Mode

In the QSPI boot mode, the PS boots from the QSPI flash located on the module. The flash device is con-

nected to the PS MIO pins 1-6.

In order to boot from the QSPI flash, the user must enable the QSPI flash controller in the Vivado block

design and generate a new FSBL to be used for the Zynq boot image creation.

3.6 SD Card Boot Mode

In the SD card boot mode the PS boots from the SD card located on the base board.

For this operation, the following requirements must be met:

• The SD card must be connected to MIO pins 40-45

• A Zynq boot image must be generated from an SoC design having the SDIO controller enabled

• The boot image must be named “boot.bin” and then copied to the SD card

• In software versions older than Vivado 2014.4, the card detect check in the Xilinx FSBL must be disabled.

For details, please contact Enclustra Support team.

• The SDIO controller must be fed with a reasonable clock frequency. Please refer to the reference

design for guidelines on SDIO settings.

For details on SD card boot, please refer to the Xilinx Zynq documentation [18] [20].

3.7 NAND Boot Mode

In the NAND boot mode, the PS boots from the NAND flash located on the module. The flash device is

connected to the PS MIO pins 0 and 2-14.

In order to boot from the NAND flash, the user must enable the NAND controller in the Vivado block design

and set the timing parameters as described in Section 2.18.3. After these changes, a new FSBL must be

generated and used for the Zynq boot image creation.

D-0000-403-002 44 / 56 Version 05, 25.07.2019

Loading...

Loading...