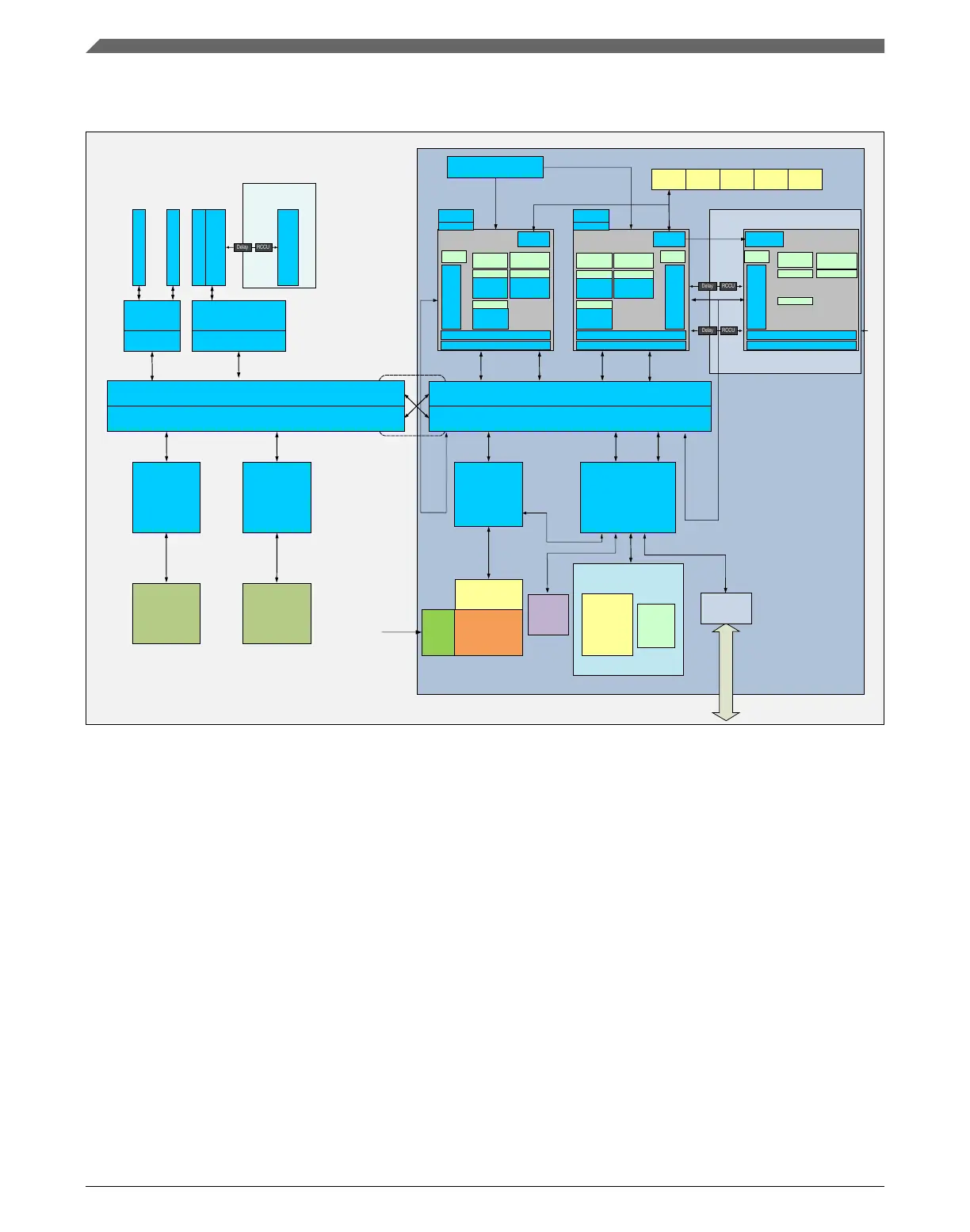

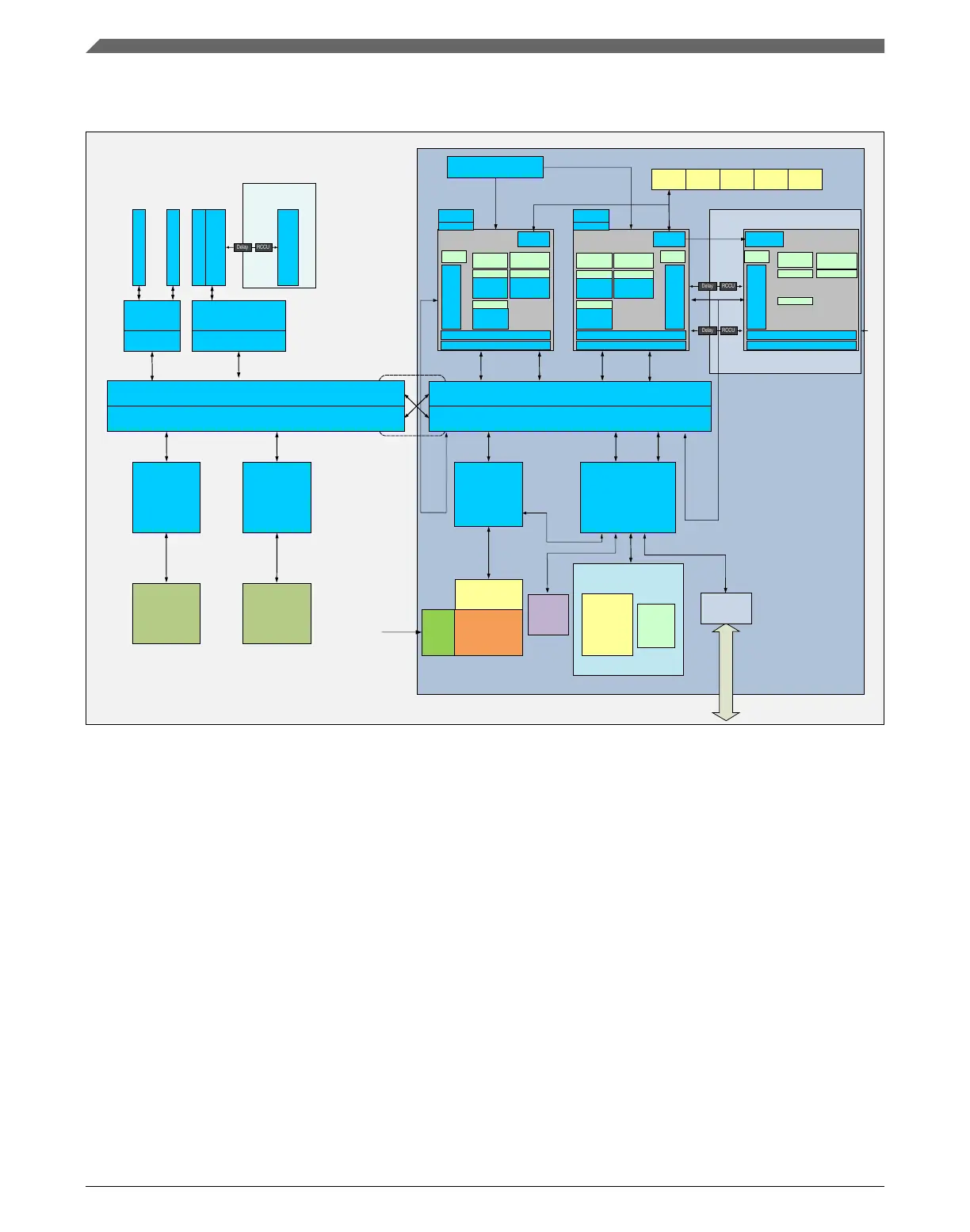

MPC5746R

Safety Lake

Ethernet

LFAST & SIPI

64ch. eDMA

w/ E2E Ecc

DMACHMUX

w/ E2E Ecc

64ch. eDMA

Delay

RCCU

Concentrator

w/ E2E Ecc

50 MHz

Nexus Data

Trace

Concentrator

w/ E2E Ecc

100 MHz

Nexus Data Trace

32 ADD

32 DATA

32 ADD

32 DATA

Slow Cross Bar Switch (AMBA 2.0 v6 AHB) - 32 bit - 100 MHz

System Memory Protection Unit (SMPU_1)

M3

M4

S0

S3

S7

M1M2

S2

S3

AIPS PBridge_0

E2E Ecc

Decorate Storage

50MHz

AIPS PBridge_1

E2E Ecc

Decorate Storage

50MHz

32 ADD

32 DATA

32 ADD

32 DATA

Peripheral

Cluster A

Peripheral

Cluster B

Peripherals allocation to the bridges is

based on safety and pinout

requirements

Double INTC

SWT_1

STM_1

E200 z425 - 200 MHz

Main Core_1

DSP

VLE

Scalar

SP-FPU

Nexus3p

I -Mem ctrl

I-Cache ctrl

16kB

IMEM

8kB - 2way

D -Mem ctrl

32kB

DMEM

Core Memory Protection Unit (CMPU)

BIU with E2E ECC

32 ADD

64 DATA

Instruction

32 ADD

64 DATA

Load/

Store

32 ADD

64 DATA

Instruction

Load/

Store

32 ADD

64 DATA

M2

S2

M3

M0

S0

M1

S1 S4

Fast Cross Bar Switch (AMBA 2.0 v6 AHB) - 64 bit - 200 MHz

System Memory Protection Unit (SMPU_0)

SWT_0

STM_0

E200 z425 - 200 MHz

Main Core_0

DSP

VLE

Scalar

SP-FPU

Nexus3p

I -Mem ctrl

I-Cache ctrl

16kB

IMEM

8kB - 2way

D -Mem ctrl

32kB

DMEM

Core Memory Protection Unit (CMPU)

BIU with E2E ECC

w/ E2E Ecc

Unified Backdoor I/F

w/ E2E Ecc

Unified Backdoor I/F

DSP

VLE

Scalar

SP-FPU

I -Mem ctrl

I-Cache ctrl

D -Mem ctrl

Core Memory Protection Unit (CMPU)

BIU with E2E ECC

w/ E2E Ecc

Unified Backdoor I/F

Nexus RWA

E200 z424 - 200 MHz

Checker Core_0s

Computational Shell - Fast Domain 200MHz

32 ADD

64 DATA

32 ADD

64 DATA

32 ADD

64 DATA

SRAM Ctrl

w/ E2E Ecc

Decorated

access

Intelligent

Bridging

Bus gasket

Standby

Supply

FLASH Controller

Dual Ported

Incl. Set-Associative

Prefetch Buffers

w/ E2E Ecc

Overlay

Backdoor

for

system

RAM

SRAM

224KB

Standby

SRAM

32KB

Standby

Regulator

Overlay

RAM

16kB

Flash

4MB

EEPROM

256k

256 Page Line

2 stage Pipeline

NVM (Single Module)

Calibration

Bus

Buddy

Device

Interface

JTAGM

JTAGC

DCI SPU

Nexus

Aurora

Router

Delayed Lock-step

with Redundnacy

Checkers

Delay

Delay

RCCU

RCCU

Safety Lake

Peripheral Domain - 50 MHz

Figure 1. Core block diagram

SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017

Loading...

Loading...