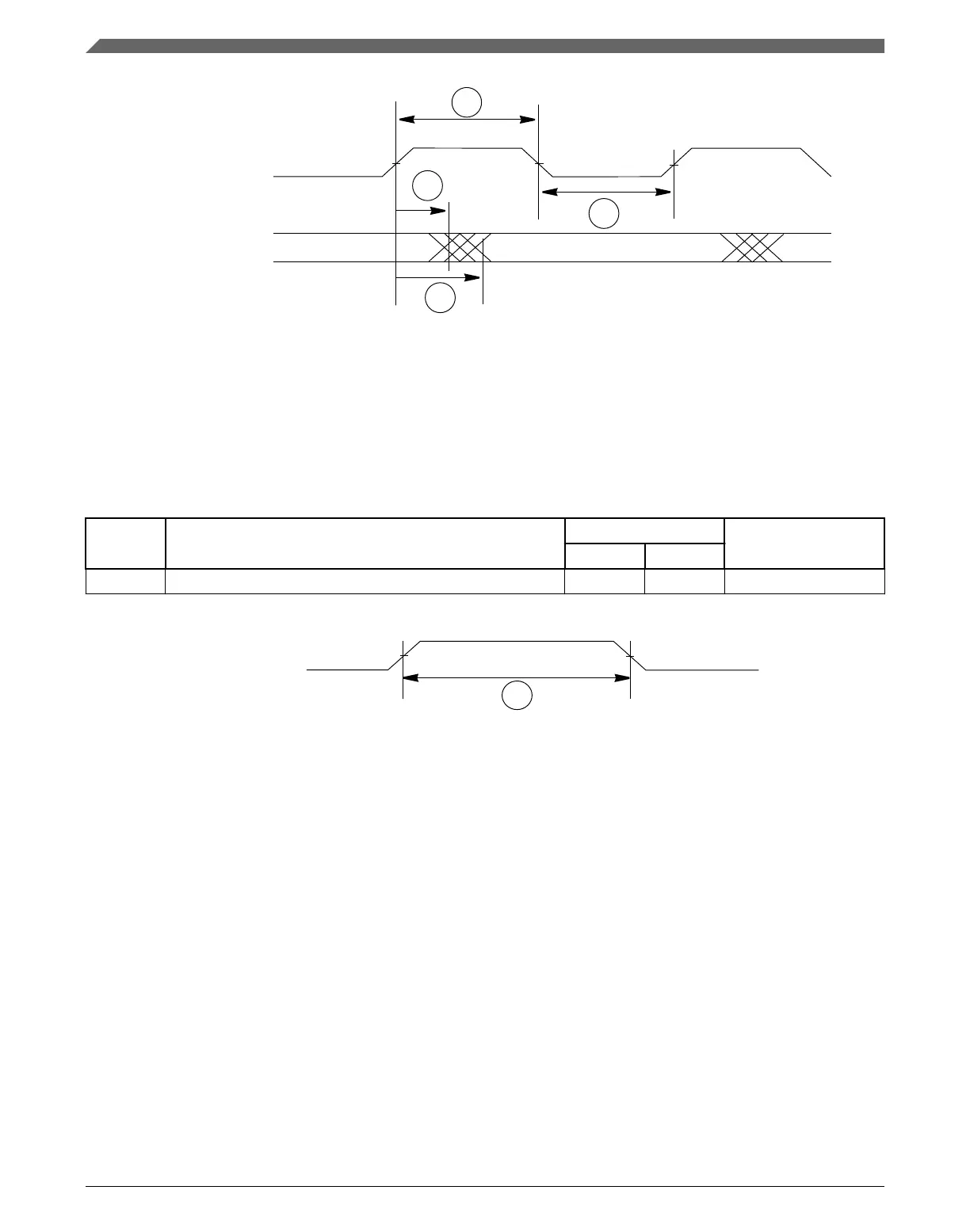

M5

M8

M7

M6

TX_CLK (input)

TXD[3:0] (outputs)

TX_

EN

TX_

ER

Figure 42. MII-lite transmit signal timing diagram

18.3.3 MII-lite async inputs signal timing (CRS and COL)

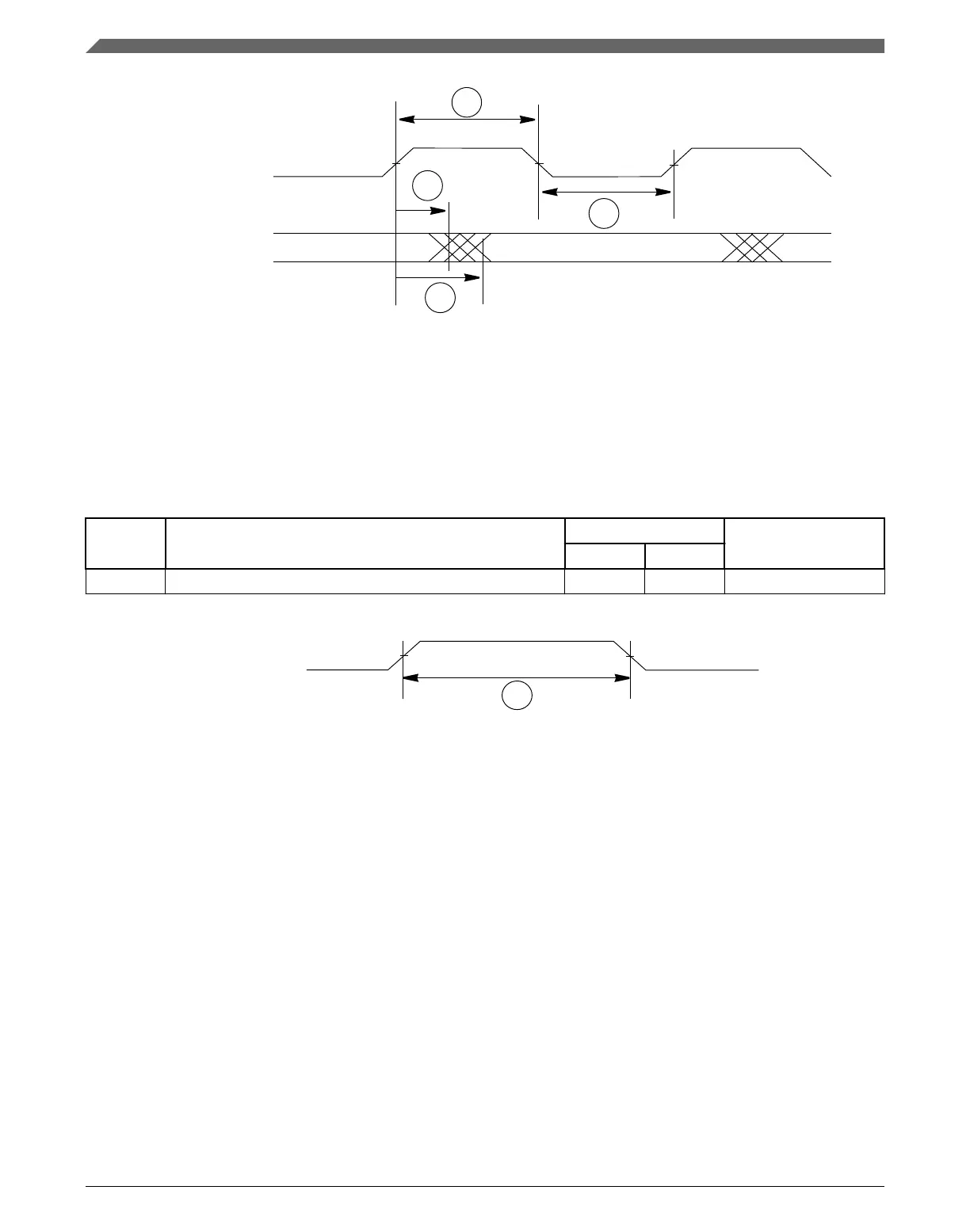

Table 48. MII-lite async inputs signal timing

Spec Characteristic

Value Unit

Min Max

M9 CRS, COL minimum pulse width 1.5 — TX_CLK period

Figure 43. MII-lite async inputs timing diagram

18.3.4

MII-lite serial management channel timing (MDIO and MDC)

The FEC functions correctly with a maximum MDC frequency of 2.5 MHz.

NOTE

All timing specifications are referenced from MDC = 1.4 V

(TTL levels) to the valid input and output levels, 0.8 V and 2.0

V (TTL levels). For 5 V operation, timing is referenced from

MDC = 50% to 2.2 V/3.5 V input and output levels.

AC specifications

SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017

82 NXP Semiconductors

Loading...

Loading...