1067

Instruction Execution Times and Number of Steps Section 4-1

Examples:

For a C-series PLC, the OUTPUT instruction requires 2 words per instruc-

tion, so 1 step (2

− 1) would be required for a CP-series PLC.

For a CV/CVM1-series PLC, the immediate refresh variation of the MOVE

instruction (!MOV) requires 4 words per instruction, so 7 steps (4 + 3)

would be required for a CP-series PLC.

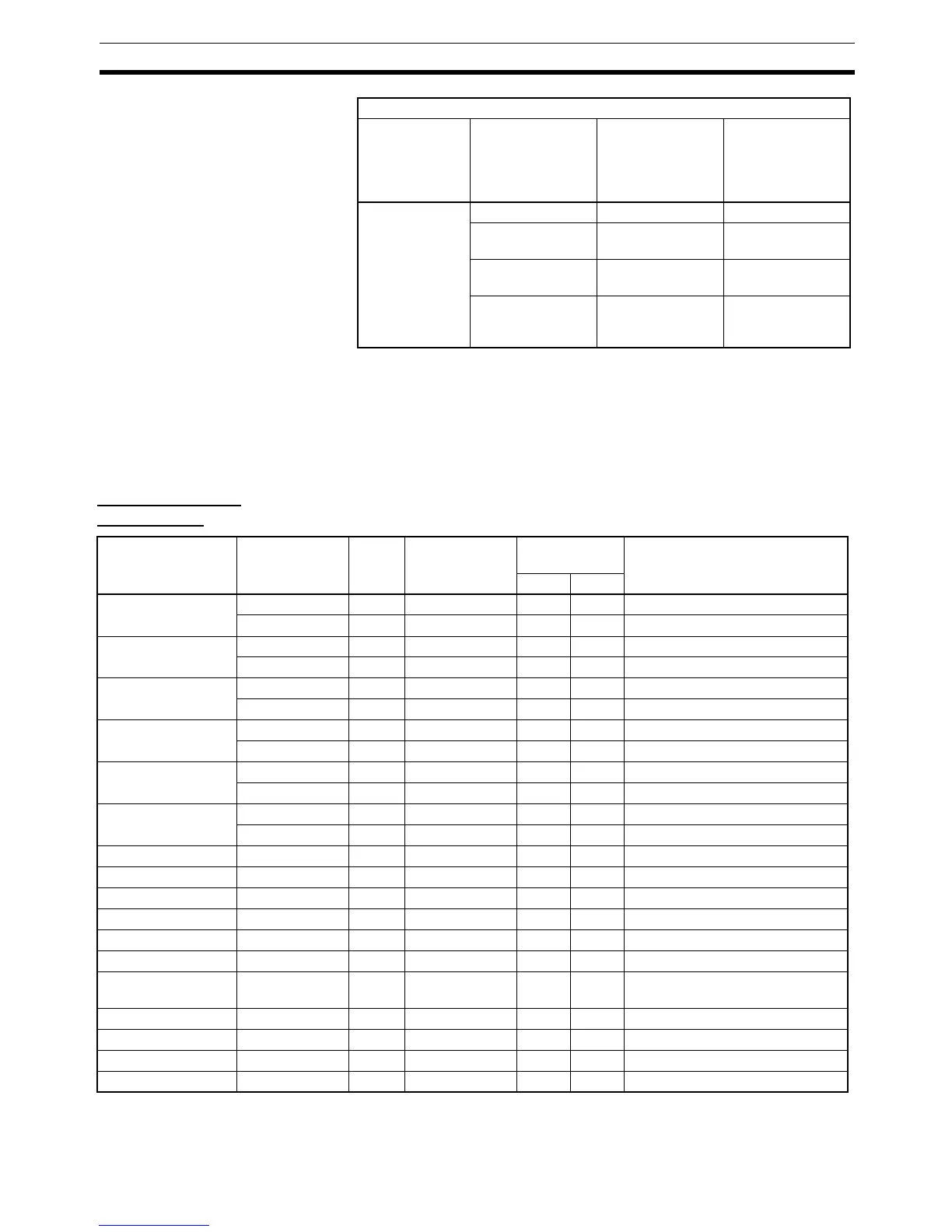

Sequence Input

Instructions

Note When a double-length operand is used, add 1 to the value shown in the length

column in the following table

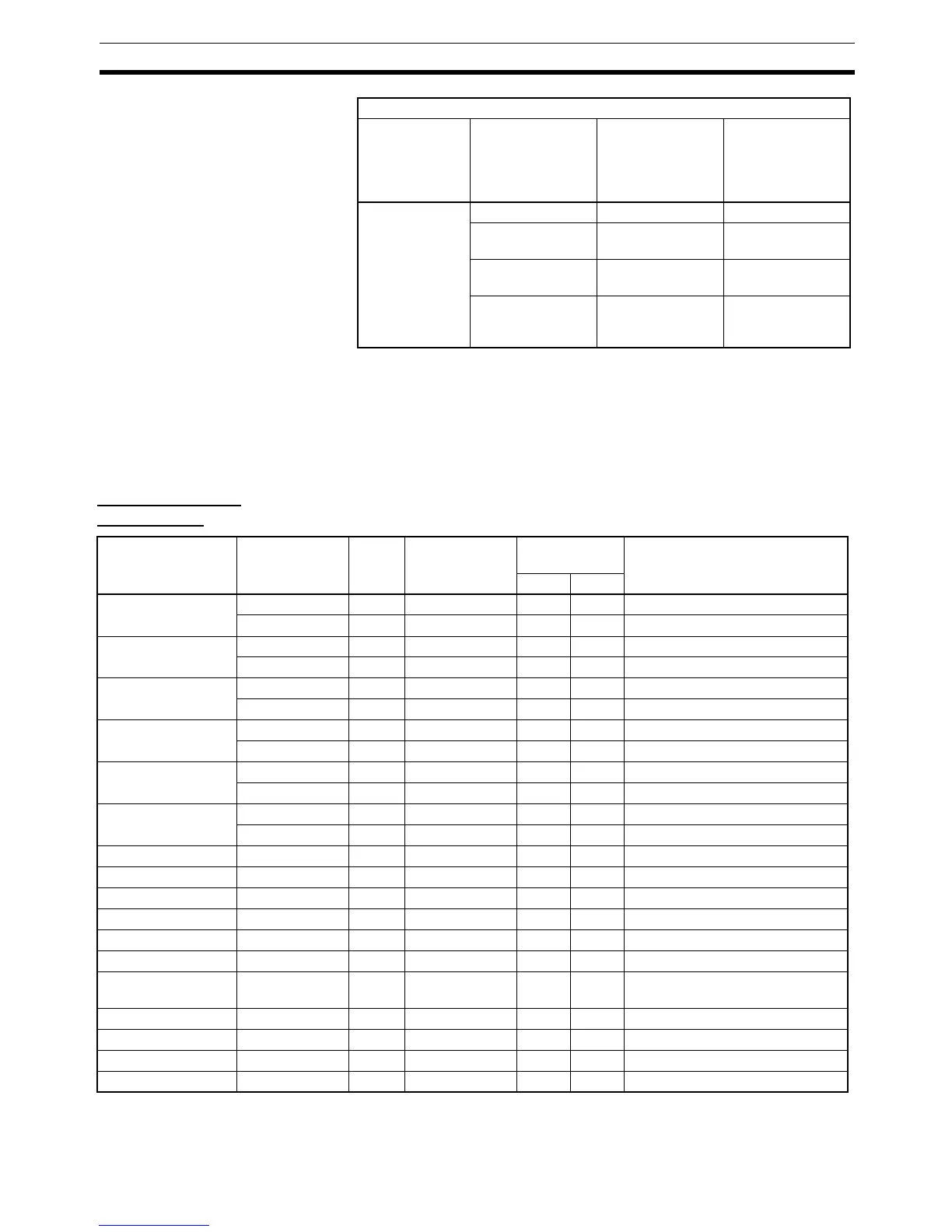

Special instruc-

tions

None 0 −1

Upward differentia-

tion

+1 0

Immediate refresh-

ing

--- +3

Upward differentia-

tion and immediate

refreshing

--- +4

Previous size in “a” words - CP1H size in “a+n” steps

Instruction

type

Instruction

options

Value of “n”

when converting

C-series PLC to

CP-series PLC

Value of “n”

when converting

CV/CVM1-series

PLC to CP-series

PLC

Instruction Mnemonic Code Length (steps)

(See note.)

ON execution

time (µs)

Conditions

CP1H CP1L

LOAD LD --- 1 0.10 0.55 ---

!LD --- 2 +24.10 +5.60 Increase for immediate refresh

LOAD NOT LD NOT --- 1 0.10 0.55 ---

!LD NOT --- 2 +24.10 +5.62 Increase for immediate refresh

AND AND --- 1 0.10 0.61 ---

!AND --- 2 +24.10 +5.60 Increase for immediate refresh

AND NOT AND NOT --- 1 0.10 0.65 ---

!AND NOT --- 2 +24.10 +5.62 Increase for immediate refresh

OR OR --- 1 0.10 0.68 ---

!OR --- 2 +24.10 +5.65 Increase for immediate refresh

OR NOT OR NOT --- 1 0.10 0.65 ---

!OR NOT --- 2 +24.10 +5.62 Increase for immediate refresh

AND LOAD AND LD --- 1 0.05 0.42 ---

OR LOAD OR LD --- 1 0.05 0.39 ---

NOT NOT 520 1 0.05 0.42 ---

CONDITION ON UP 521 3 0.50 2.37 ---

CONDITION OFF DOWN 522 4 0.50 2.89 ---

LOAD BIT TEST LD TST 350 4 0.35 4.22 ---

LOAD BIT TEST

NOT

LD TSTN 351 4 0.35 4.22 ---

AND BIT TEST AND TST 350 4 0.35 6.50 ---

AND BIT TEST NOT AND TSTN 351 4 0.35 4.29 ---

OR BIT TEST OR TST 350 4 0.35 4.31 ---

OR BIT TEST NOT OR TSTN 351 4 0.35 4.29 ---

Loading...

Loading...