173

Timer and Counter Instructions Section 3-5

The timer’s Completion Flag is refreshed only when TIM/TIMX(550) is exe-

cuted, so a delay of up to one cycle may be required for the Completion Flag

to be turned ON after the timer times out.

If online editing is used to convert a timer to another kind of timer with the

same timer number (such as TIM/TIMX(550)

↔ TIMH(015)/TIMHX(551) or

TIM/TIMX(550)

↔ TMHH(540)/TMHHX(552)), be sure to reset the Comple-

tion Flag. The timer will not operate properly unless the Completion Flag is

reset.

A TIM/TIMX(550) instruction’s PV and Completion Flag can be refreshed in

the following ways depending on the timer number that is used.

Timers Created with Timer Numbers 0000 to 2047

Timers Created with Timer Numbers T0016 to T4095

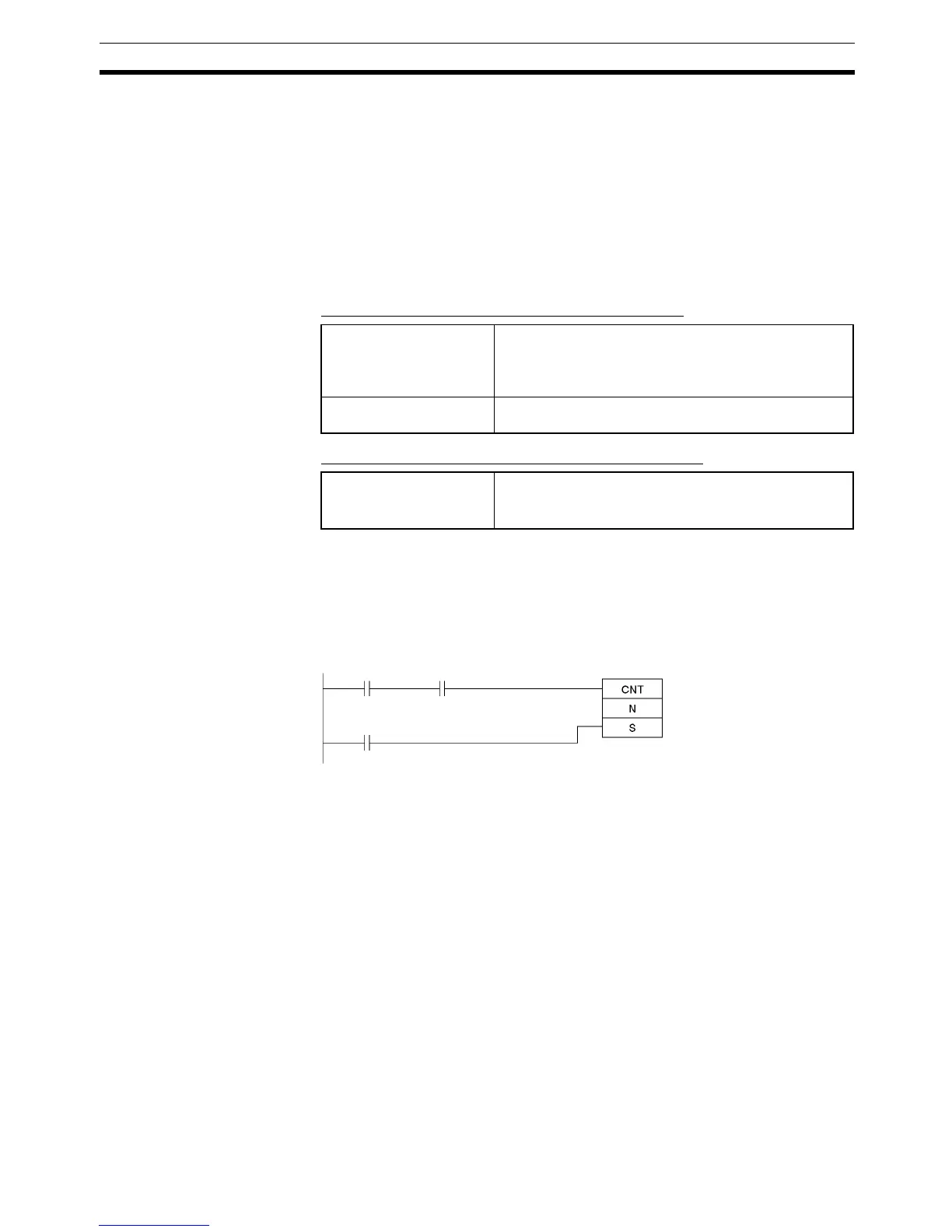

Timers are reset (PV = SV, Completion Flag OFF) by power interruptions

unless the IOM Hold Bit (A500.12) is ON and the bit is protected in the PLC

Setup. It is also possible use a clock pulse bit and a counter instruction to pro-

gram a timer that will retain its PV in the event of a power interruption, as

shown in the following diagram.

Execution of TIM/

TIMX(550)

The PV is updated every time that TIM/TIMX(550) is exe-

cuted.

The Completion Flag is turned ON if the PV is 0000.

The Completion Flag is turned OFF if the PV is not 0000.

100-ms interval refreshing If the cycle time exceeds 100 ms, the timer’s PV is

updated every 100 ms.

Execution of TIM The PV is updated every time that TIM is executed.

The Completion Flag is turned ON if the PV is 0.

The Completion Flag is turned OFF if the PV is not 0.

Count input

Reset input

Execution

condition

1-s clock

pulse bit

Loading...

Loading...