207

Timer and Counter Instructions Section 3-5

The timer or counter instruction will not be executed if the PLC memory

address in the specified Index Register is not the address of a timer or counter

PV.

Using Index Registers to indirectly address timers and counters can reduce

the size of the program and increase flexibility. For example, common subrou-

tines can be created.

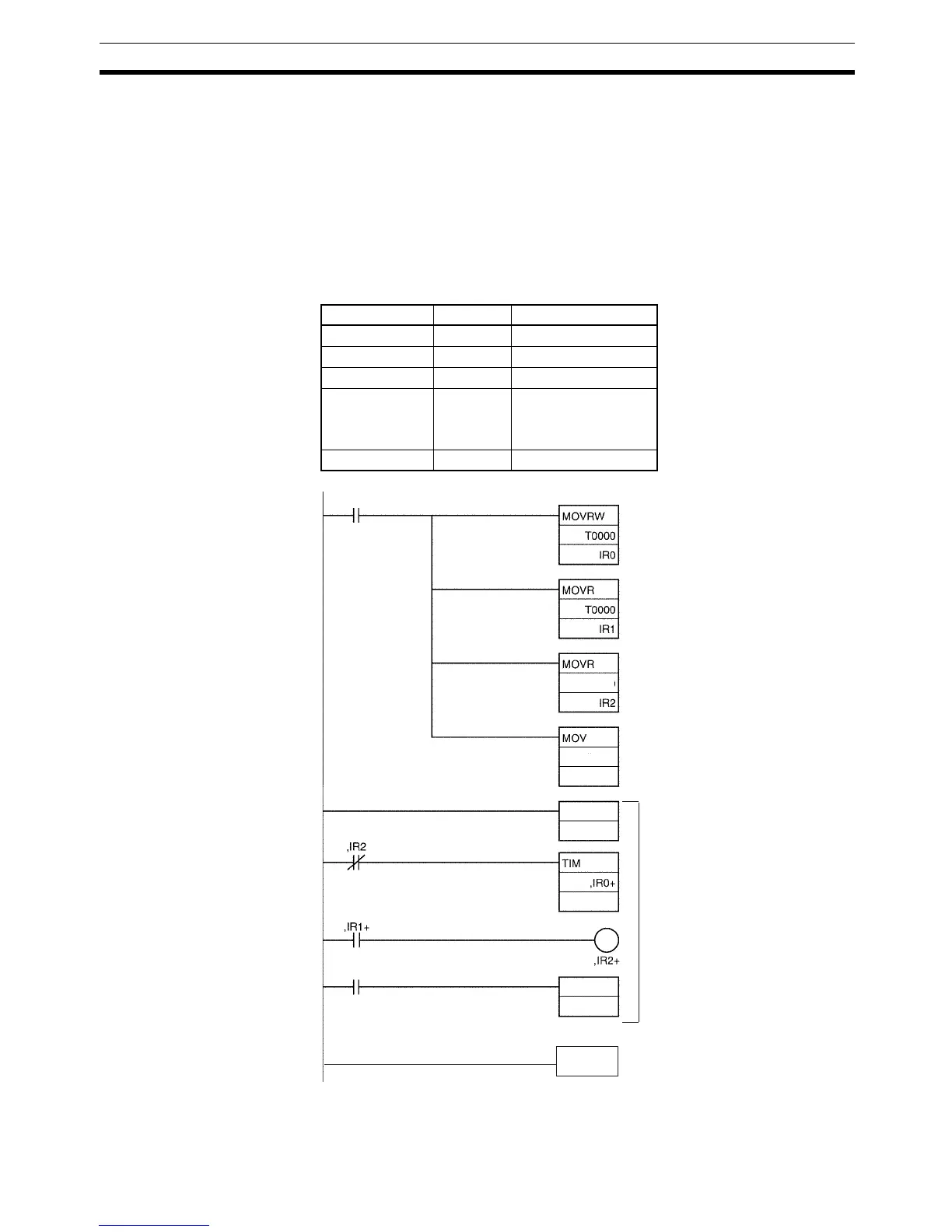

Example The following example shows a program section that uses indirect addressing

to define and start 100 timers with SVs contained in D100 through D199. IR0

contains the PLC memory address of the timer PV and IR1 contains the PLC

memory address of the timer Completion Flag.

1,2,3... 1. MOVRW(561) moves the PLC memory address of the PV for timer T0000

to IR0. Afterwards IR0 can be used in place of the timer number.

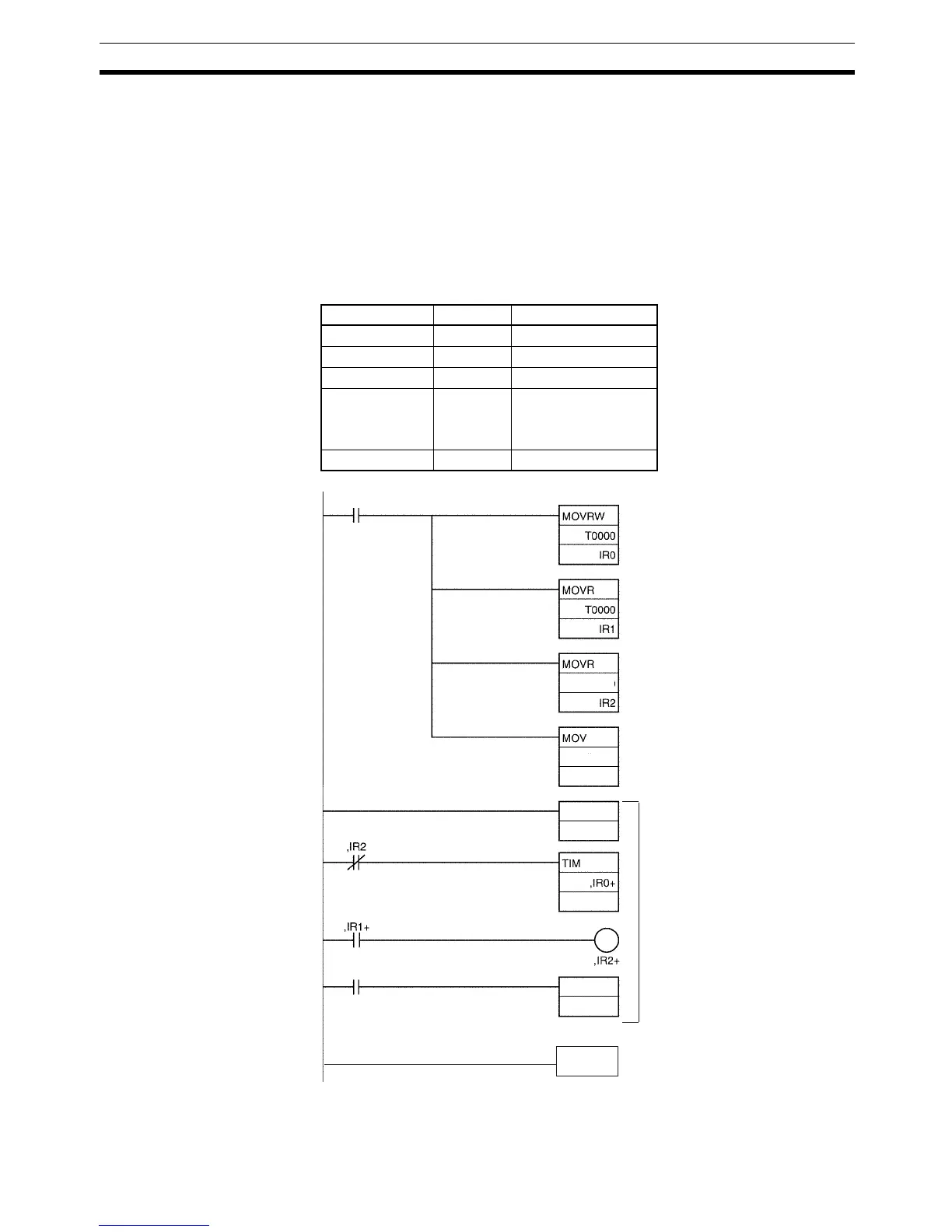

DM address Content Function

D100 0010 SV for T0000

D101 0100 SV for T0001

D102 0050 SV for T0002

.

.

.

.

.

.

.

.

.

D199 0999 SV for T0099

1

2

3

4

5

P

_

On

P

_

On

&100

FOR

&100

@D0

++

NEXT

2000.00

D0

D0

(Always ON

Flag)

(Always ON

Flag)

Loading...

Loading...