Principles of analog modules

5.6 Settling and response times of analog output channels

S7-300 Module data

Manual, 06/2017, A5E00105505-AJ

293

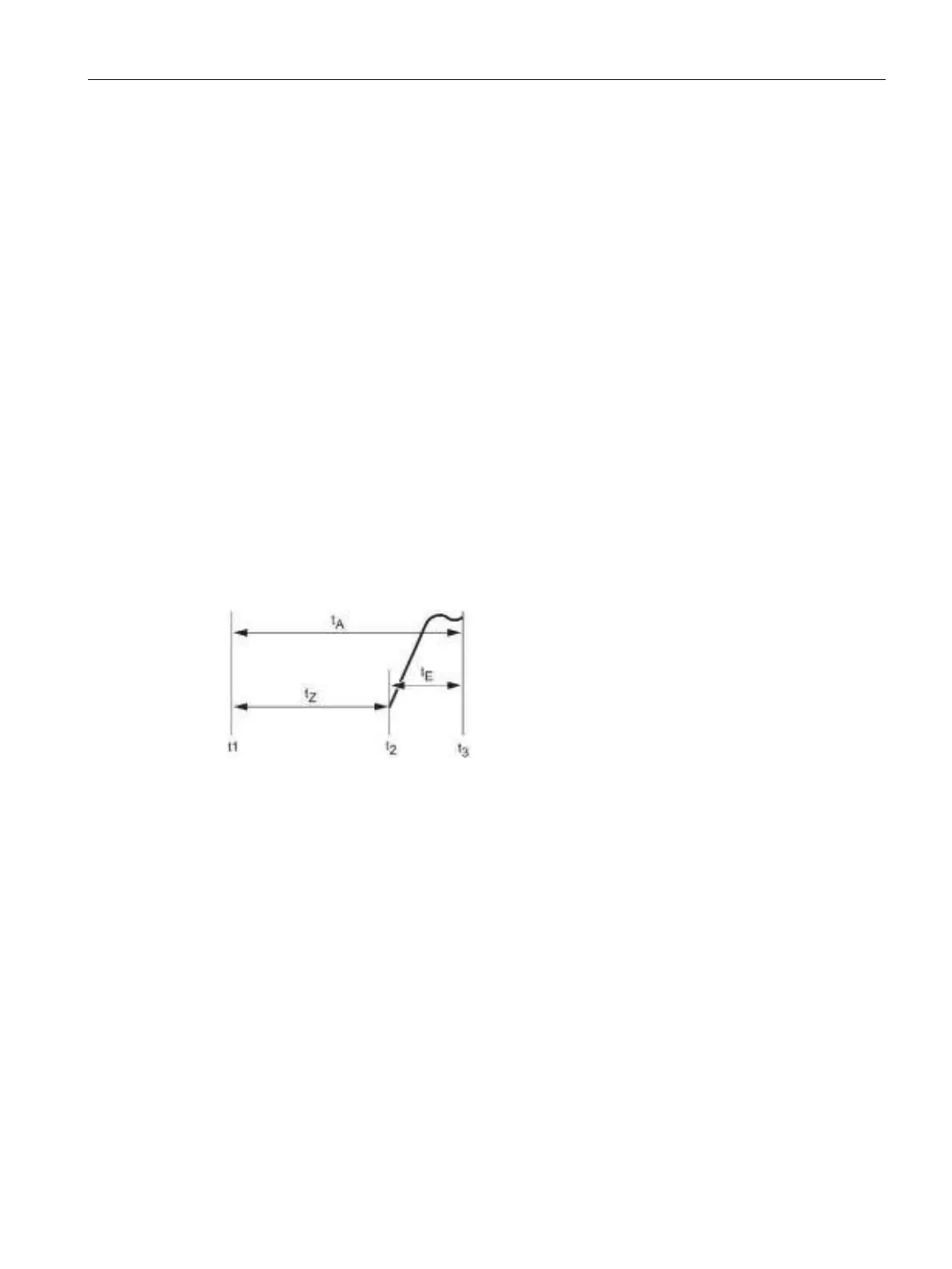

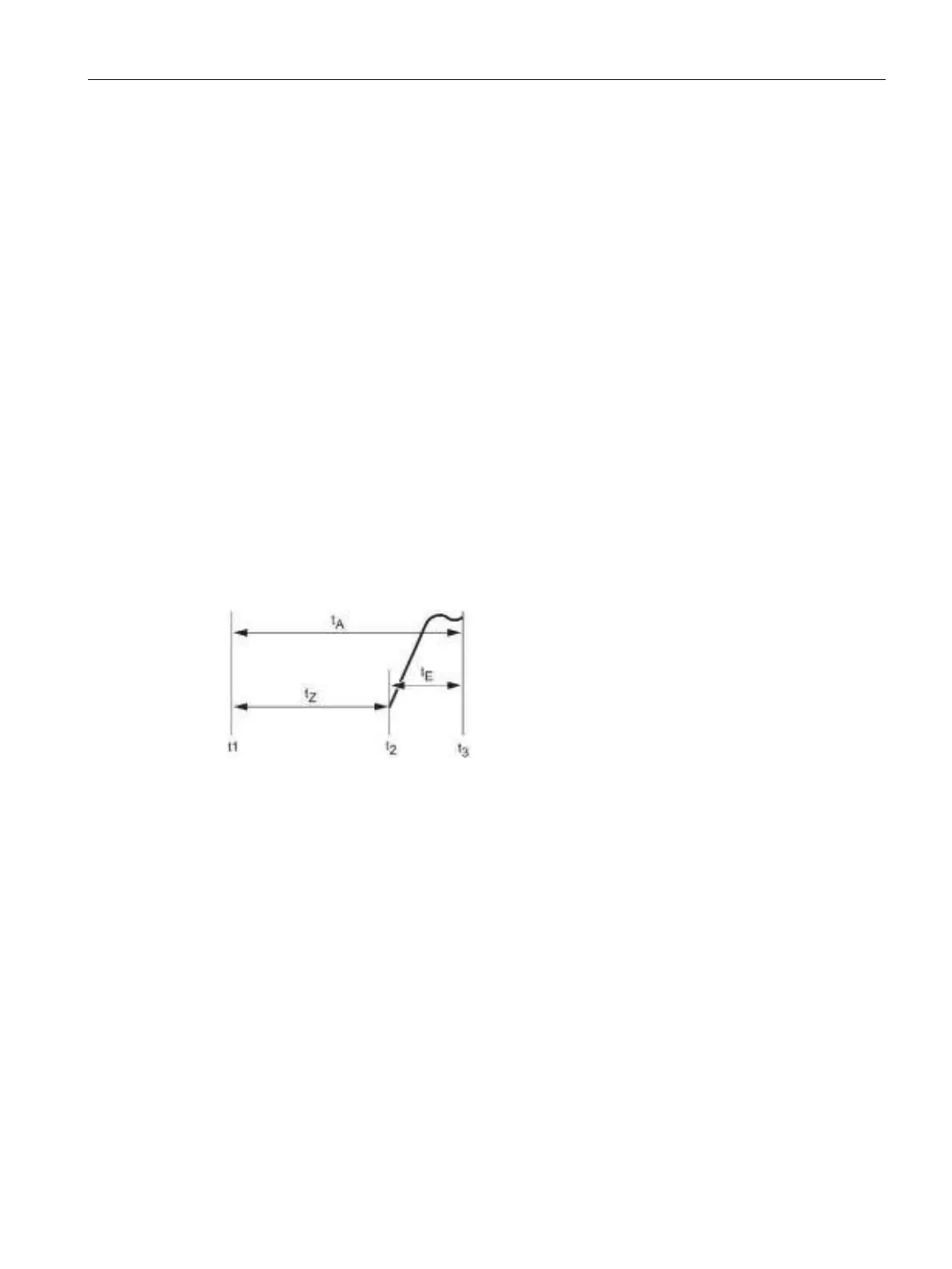

5.6 Settling and response times of analog output channels

Settling time

The settling time (t

2

to t

3

), i.e. the time expiring until a converted value has gained a specified

level at an analog output, is load-dependent. We therefore distinguish between resistive,

capacitive and inductive load.

For information on settling times as a function of load at the various analog output modules,

refer to the technical data of the relevant module.

Response time

The worst case response time (t

1

to t

3

), i.e. the time expiring between the input of digital

output values to internal memory, and the signal settling time at the analog output, may be

equivalent to the total of cycle time plus settling time.

The worst case scenario is given, when the analog channel has been converted immediately

before a new output value is transferred, and is not converted again until all other channels

have been converted (cycle time.)

Overview of the settling time and response time of analog output modules

tC = Cycle time, equivalent to n x conversion time (n = active channels)

new digital output value is set

Output value is applied and converted

specified output value is reached

Loading...

Loading...