DocID018909 Rev 11 1221/1731

RM0090 Ethernet (ETH): media access control (MAC) with DMA controller

1232

Ethernet DMA operation mode register (ETH_DMAOMR)

Address offset: 0x1018

Reset value: 0x0000 0000

The operation mode register establishes the Transmit and Receive operating modes and

commands. The ETH_DMAOMR register should be the last CSR to be written as part of

DMA initialization.

Bit 6 RS: Receive status

This bit indicates the completion of the frame reception. Specific frame status information

has been posted in the descriptor. Reception remains in the Running state.

Bit 5 TUS: Transmit underflow status

This bit indicates that the transmit buffer had an underflow during frame transmission.

Transmission is suspended and an underflow error TDES0[1] is set.

Bit 4 ROS: Receive overflow status

This bit indicates that the receive buffer had an overflow during frame reception. If the partial

frame is transferred to the application, the overflow status is set in RDES0[11].

Bit 3 TJTS: Transmit jabber timeout status

This bit indicates that the transmit jabber timer expired, meaning that the transmitter had

been excessively active. The transmission process is aborted and placed in the Stopped

state. This causes the transmit jabber timeout TDES0[14] flag to be asserted.

Bit 2 TBUS: Transmit buffer unavailable status

This bit indicates that the next descriptor in the transmit list is owned by the host and cannot

be acquired by the DMA. Transmission is suspended. Bits [22:20] explain the transmit

process state transitions. To resume processing transmit descriptors, the host should change

the ownership of the bit of the descriptor and then issue a Transmit Poll Demand command.

Bit 1 TPSS: Transmit process stopped status

This bit is set when the transmission is stopped.

Bit 0 TS: Transmit status

This bit indicates that frame transmission is finished and TDES1[31] is set in the first

descriptor.

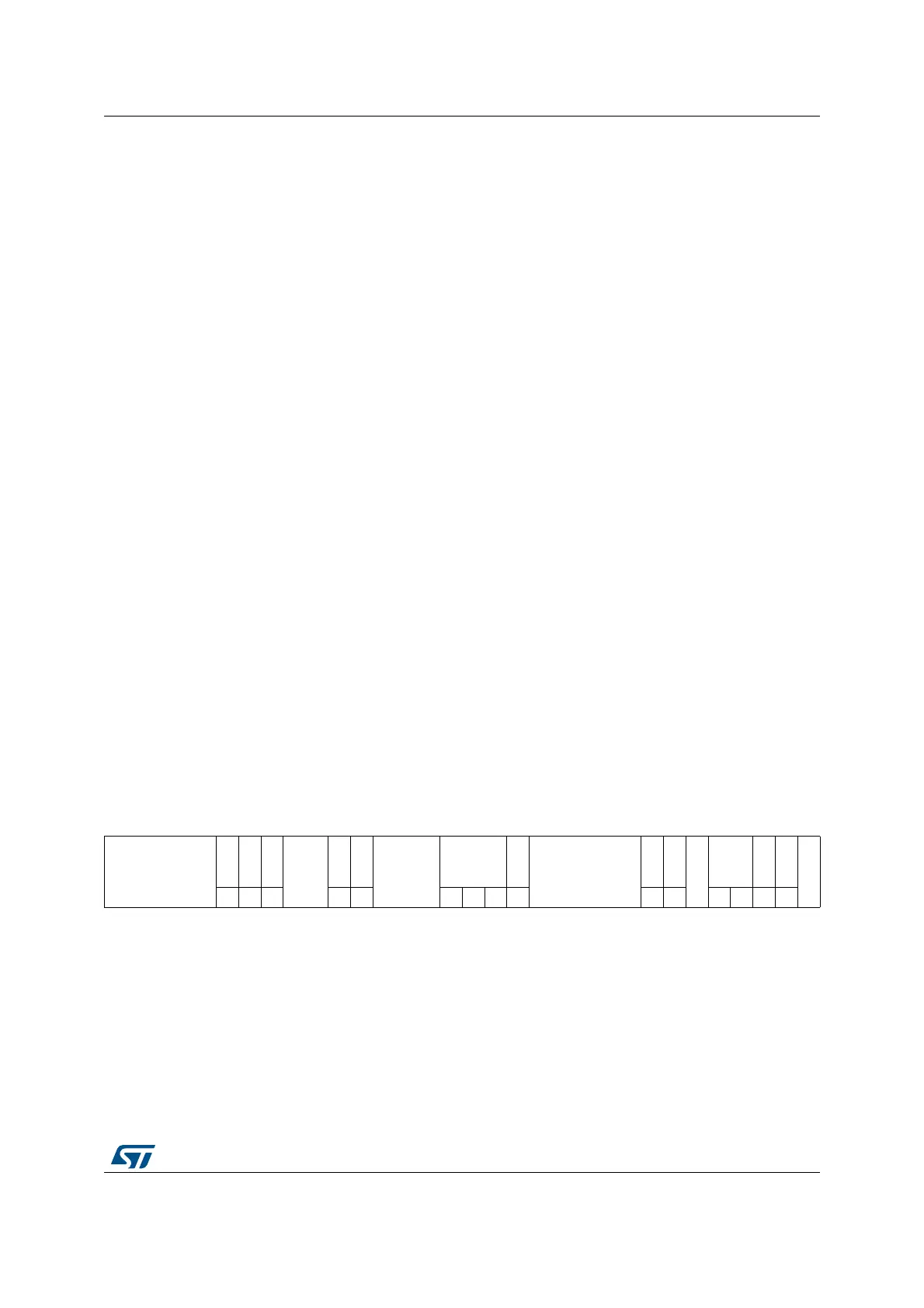

313029282726252423222120191817161514131211109876543210

Reserved

DTCEFD

RSF

DFRF

Reserved

TSF

FTF

Reserved

TTC

ST

Reserved

FEF

FUGF

Reserved

RTC

OSF

SR

Reserved

rw rw rw rw rs rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...