DocID018909 Rev 11 1249/1731

RM0090 USB on-the-go full-speed (OTG_FS)

1368

gating. The dynamic power consumption due to the USB clock switching activity is cut

even if the 48 MHz clock input is kept running by the application

Most of the transceiver is also disabled, and only the part in charge of detecting the

asynchronous resume or remote wakeup event is kept alive.

• Gate HCLK (GATEHCLK bit in OTG_FS_PCGCCTL)

When setting the Gate HCLK bit in the clock gating control register, most of the system

clock domain internal to the OTG_FS core is switched off by clock gating. Only the

register read and write interface is kept alive. The dynamic power consumption due to

the USB clock switching activity is cut even if the system clock is kept running by the

application for other purposes.

• USB system stop

When the OTG_FS is in the USB suspended state, the application may decide to

drastically reduce the overall power consumption by a complete shut down of all the

clock sources in the system. USB System Stop is activated by first setting the Stop

PHY clock bit and then configuring the system deep sleep mode in the power control

system module (PWR).

The OTG_FS core automatically reactivates both system and USB clocks by

asynchronous detection of remote wakeup (as an host) or resume (as a device)

signaling on the USB.

To save dynamic power, the USB data FIFO is clocked only when accessed by the OTG_FS

core.

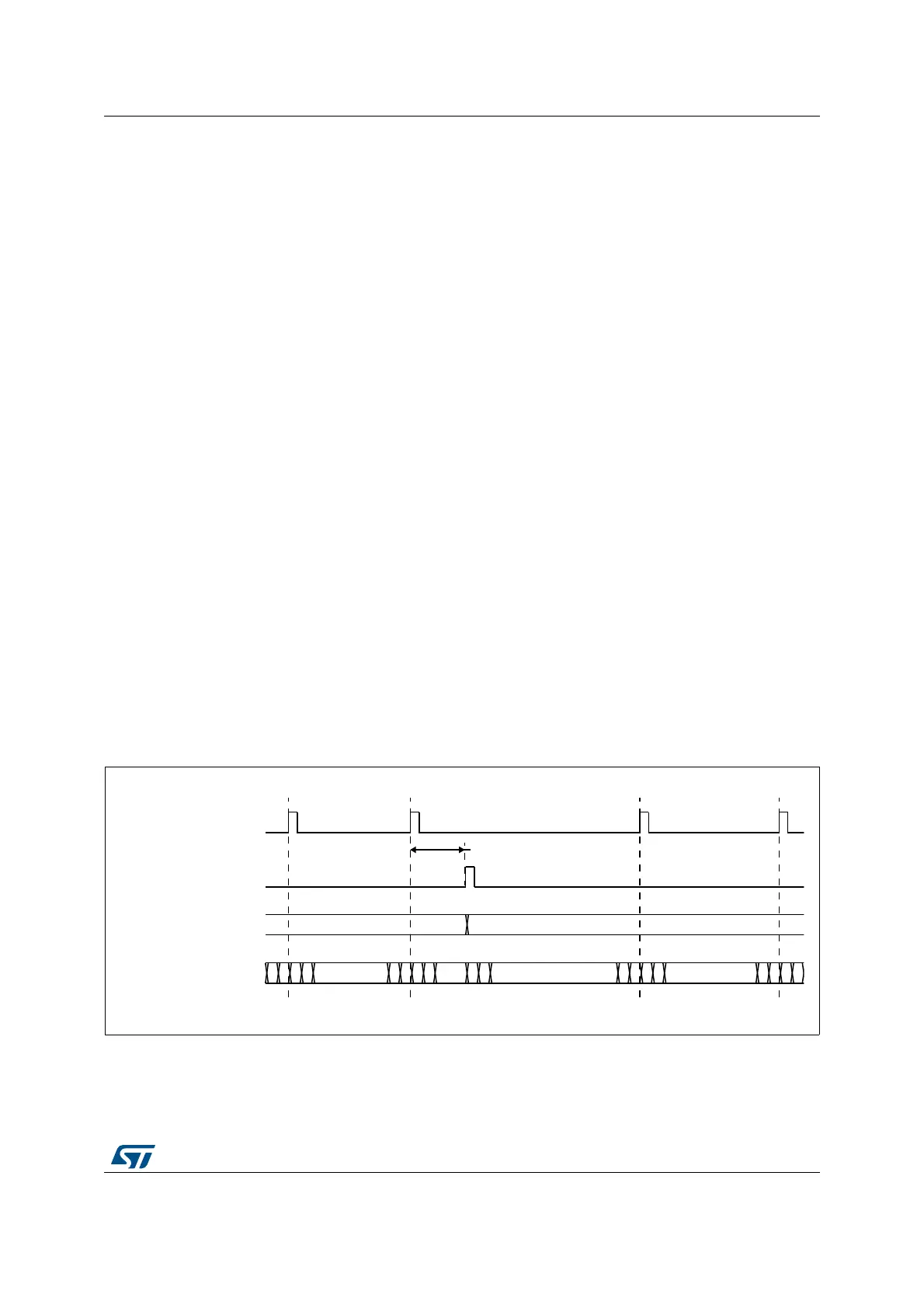

34.9 Dynamic update of the OTG_FS_HFIR register

The USB core embeds a dynamic trimming capability of micro-SOF framing period in host

mode allowing to synchronize an external device with the micro-SOF frames.

When the OTG_HS_HFIR register is changed within a current micro-SOF frame, the SOF

period correction is applied in the next frame as described in Figure 391.

Figure 391. Updating OTG_FS_HFIR dynamically

x

x

xx

,ATENCY

3/&

RELOAD

/4'?&3?(&)2

WRITE

VALUE

&RAME

TIMER

/LD/4'?&3?()&2VALUE

PERIODS

/4'?&3?()&2VALUE

PERIODS()&2WRITELATENCY

.EW/4'?&3?()&2VALUE

PERIODS

/4'?&3?(&)2

AI

Loading...

Loading...