DocID018909 Rev 11 999/1731

RM0090 Universal synchronous asynchronous receiver transmitter (USART)

1010

30.5 USART mode configuration

30.6 USART registers

Refer to Section: List of abbreviations for registers for a list of abbreviations used in register

descriptions.

The peripheral registers have to be accessed by half-words (16 bits) or words (32 bits).

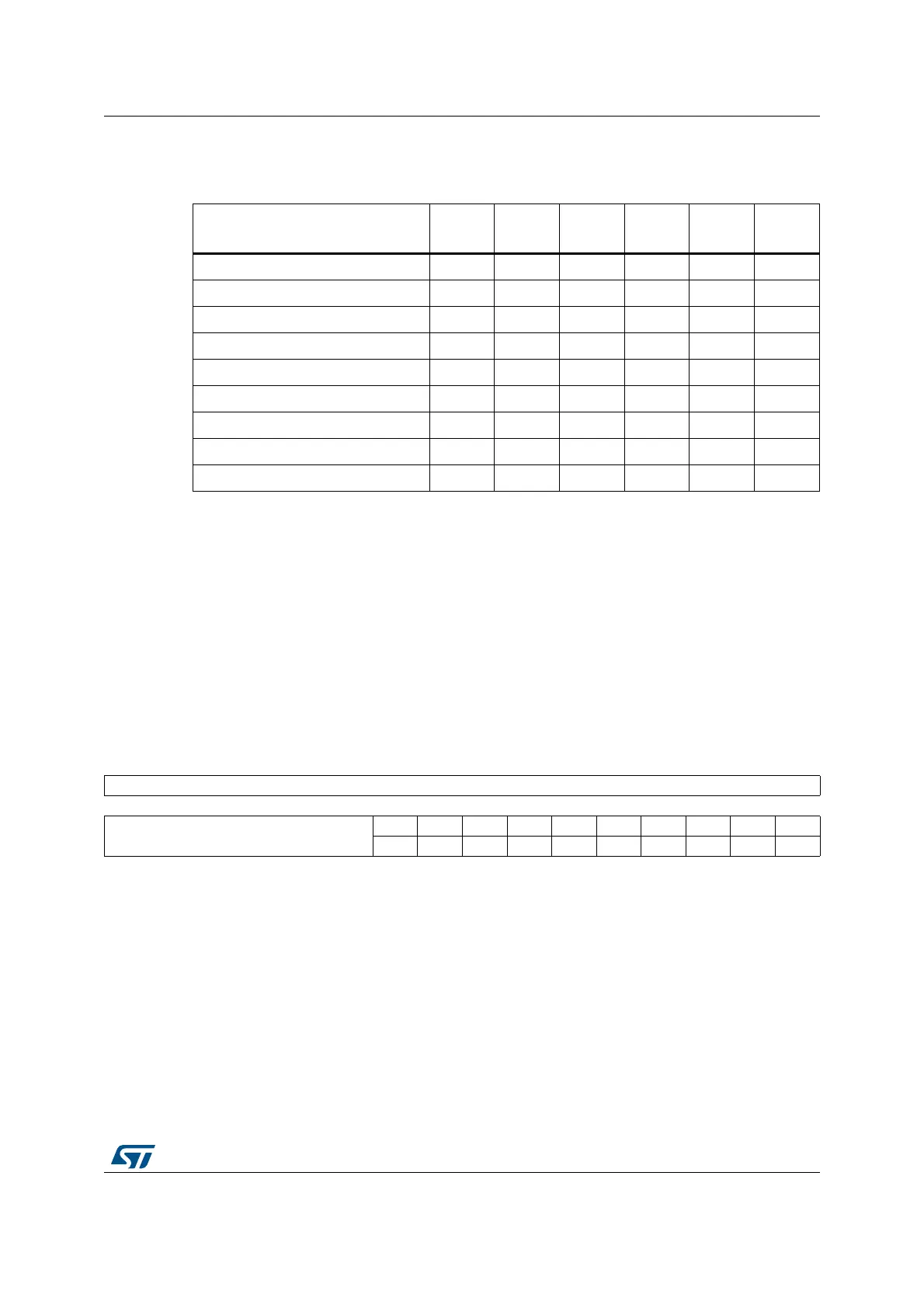

30.6.1 Status register (USART_SR)

Address offset: 0x00

Reset value: 0x00C0 0000

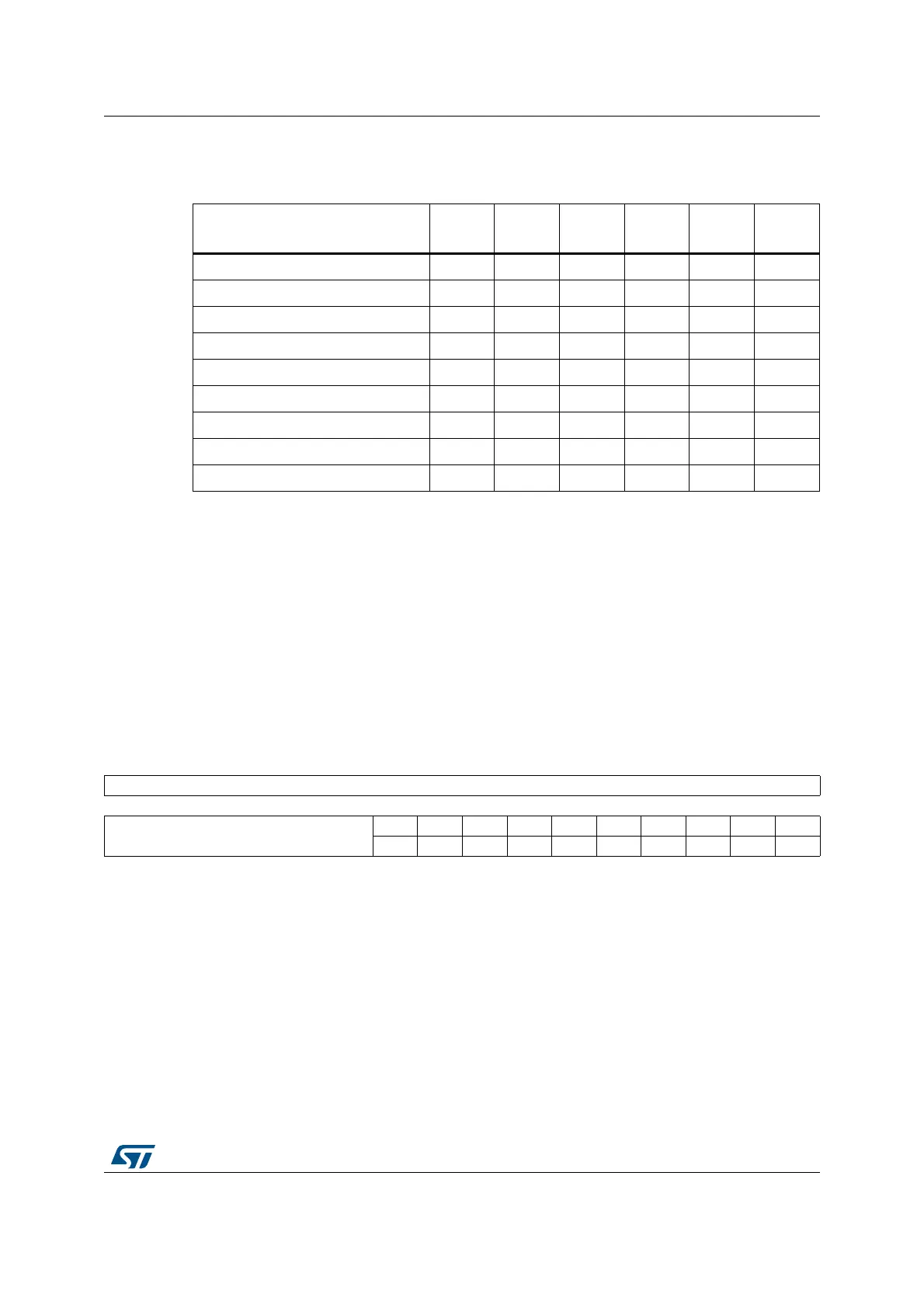

Table 147. USART mode configuration

(1)

1. X = supported; NA = not applicable.

USART modes

USART

1

USART

2

USART

3

UART4 UART5

USART

6

Asynchronous mode XXXXXX

Hardware flow control XXXNANAX

Multibuffer communication (DMA)XXXXXX

Multiprocessor communicationXXXXXX

Synchronous XXXNANAX

Smartcard XXXNANAX

Half-duplex (single-wire mode)XXXXXX

IrDA XXXXXX

LIN XXXXXX

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

CTS LBD TXE TC RXNE IDLE ORE NF FE PE

rc_w0 rc_w0 r rc_w0 rc_w0 r r r r r

Loading...

Loading...