www.ti.com

Registers

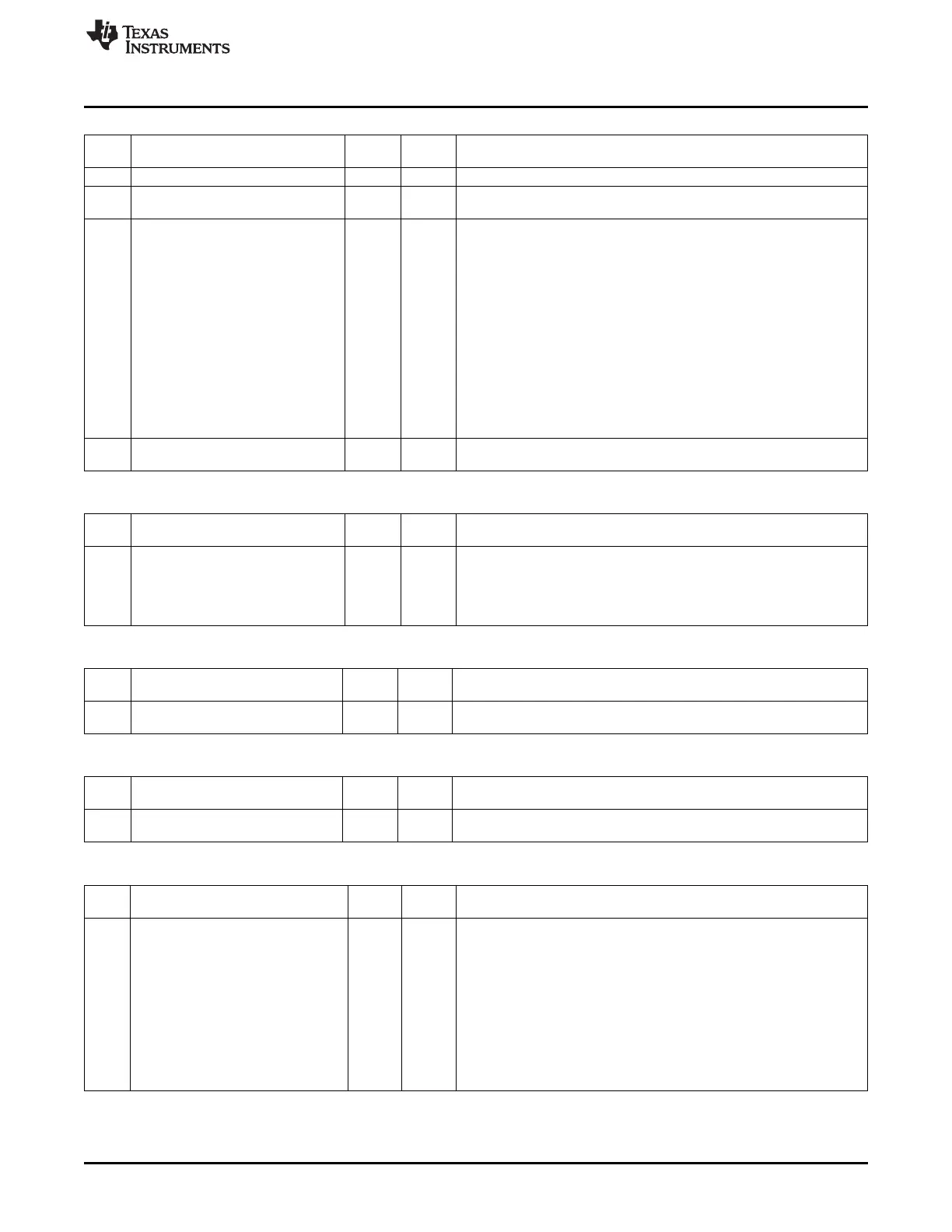

SRCMATCH (0x6182) – Source Address Matching and Pending Bits

Bit Name Reset R/W Description

No.

7:3 – 0000 0 R/W Reserved. Always write 0

2

PEND_DATAREQ_ONLY

1 R/W When this bit is set, the AUTOPEND function also requires that the

received frame is a DATA REQUEST MAC command frame.

1

AUTOPEND

1 R/W Automatic acknowledgment pending flag enable.

On reception of a frame, the pending bit in the (possibly) returned

acknowledgment is set automatically, given that:

–

FRMFILT0.FRAME_FILTER_EN is set.

–

SRCMATCH.SRC_MATCH_EN is set.

–

SRCMATCH.AUTOPEND is set.

– The received frame matches the current

SRCMATCH.PEND_DATAREQ_ONLY setting.

– The received source address matches at least one source-match

table entry, which is enabled in both SHORT_ADDR_EN and

SHORT_PEND_EN or EXT_ADDR_EN and EXT_PEND_EN.

Note: Details for SHORT_PEND_EN and EXT_PEND_EN is found in the

memory map description (Section 23.4).

0

SRC_MATCH_EN

1 R/W Source address matching enable (This bit is don't care if

FRMFILT0.FRAME_FILTER_EN = 0.)

SRCSHORTEN0 (0x6183) – Short Address Matching

Bit Name Reset R/W Description

No.

7:0

SHORT_ADDR_EN[7:0]

0x00 R/W

The 7:0 part of the 24-bit word SHORT_ADDR_EN that enables/disables

source address matching for each of the 24 short address table entries.

Optional safety feature: To ensure that an entry in the source-matching

table is not used while it is being updated, set the corresponding

SHORT_ADDR_EN bit to 0 while updating.

SRCSHORTEN1 (0x6184) – Short Address Matching

Bit Name Reset R/W Description

No.

7:0

SHORT_ADDR_EN[15:8]

0x00 R/W

The 15:8 part of the 24-bit word SHORT_ADDR_EN. See previoius

description of SRCSHORTEN0.

SRCSHORTEN2 (0x6185) – Short Address Matching

Bit Name Reset R/W Description

No.

7:0

SHORT_ADDR_EN[23:16]

0x00 R/W

The 23:16 part of the 24-bit word SHORT_ADDR_EN. See previous

description of SRCSHORTEN0.

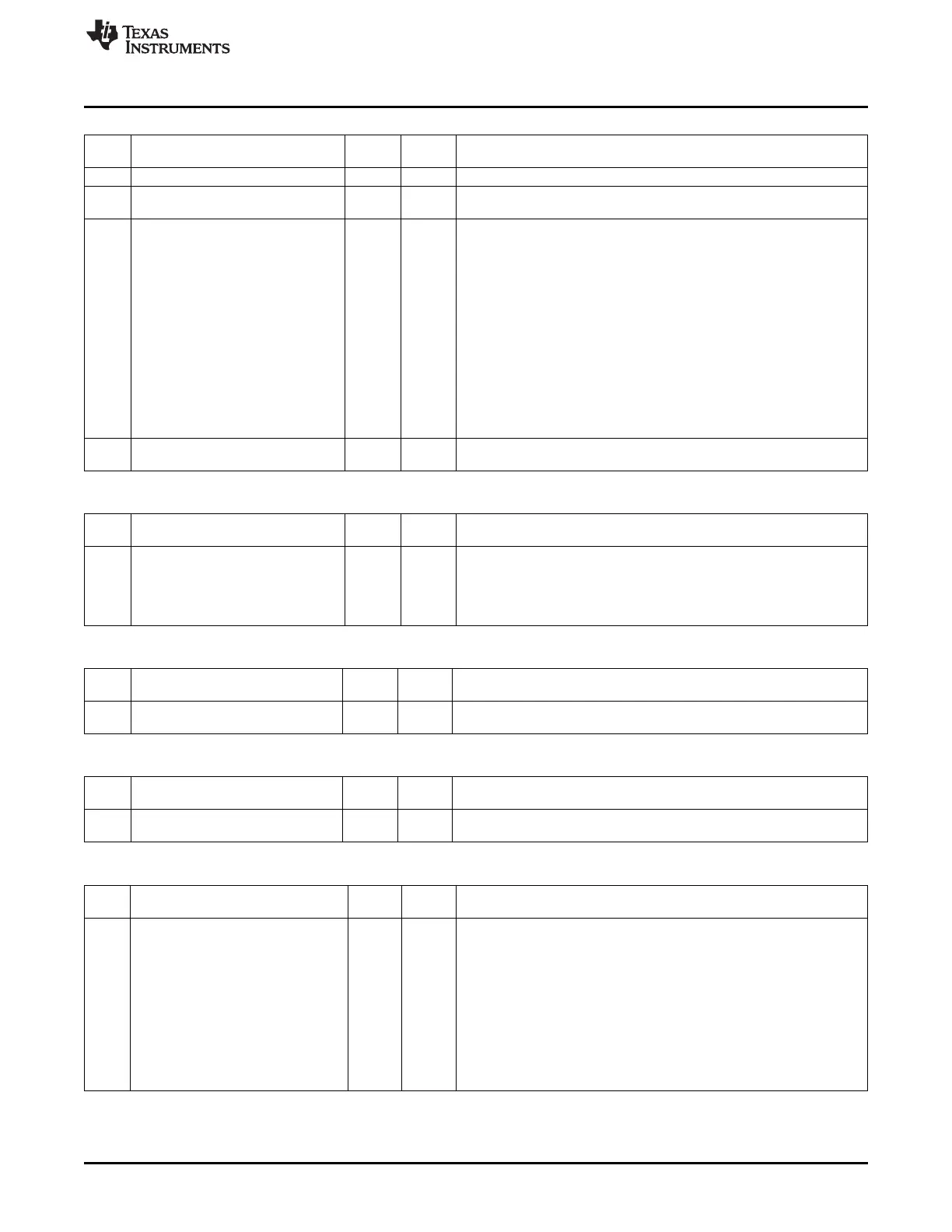

SRCEXTEN0 (0x6186) – Extended Address Matching

Bit Name Reset R/W Description

No.

7:0

EXT_ADDR_EN[7:0]

0x00 R/W

The 7:0 part of the 24-bit word EXT_ADDR_EN that enables/disables

source address matching for each of the 12 extended address table

entries.

Write access: Extended address enable for table entry n (0 to 7) is

mapped to EXT_ADDR_EN[2n]. All EXT_ADDR_EN[2n + 1] bits are

read-only and don't care when written to.

Read access: Extended address enable for table entry n (0 to 7) is

mapped to both EXT_ADDR_EN[2n] and EXT_ADDR_EN[2n + 1].

To ensure that an entry in the source matching table is not used while it

is being updated, set the corresponding EXT_ADDR_EN bit to 0 while

updating.

269

SWRU191C–April 2009–Revised January 2012 CC253x Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...