www.ti.com

Instruction Set Summary

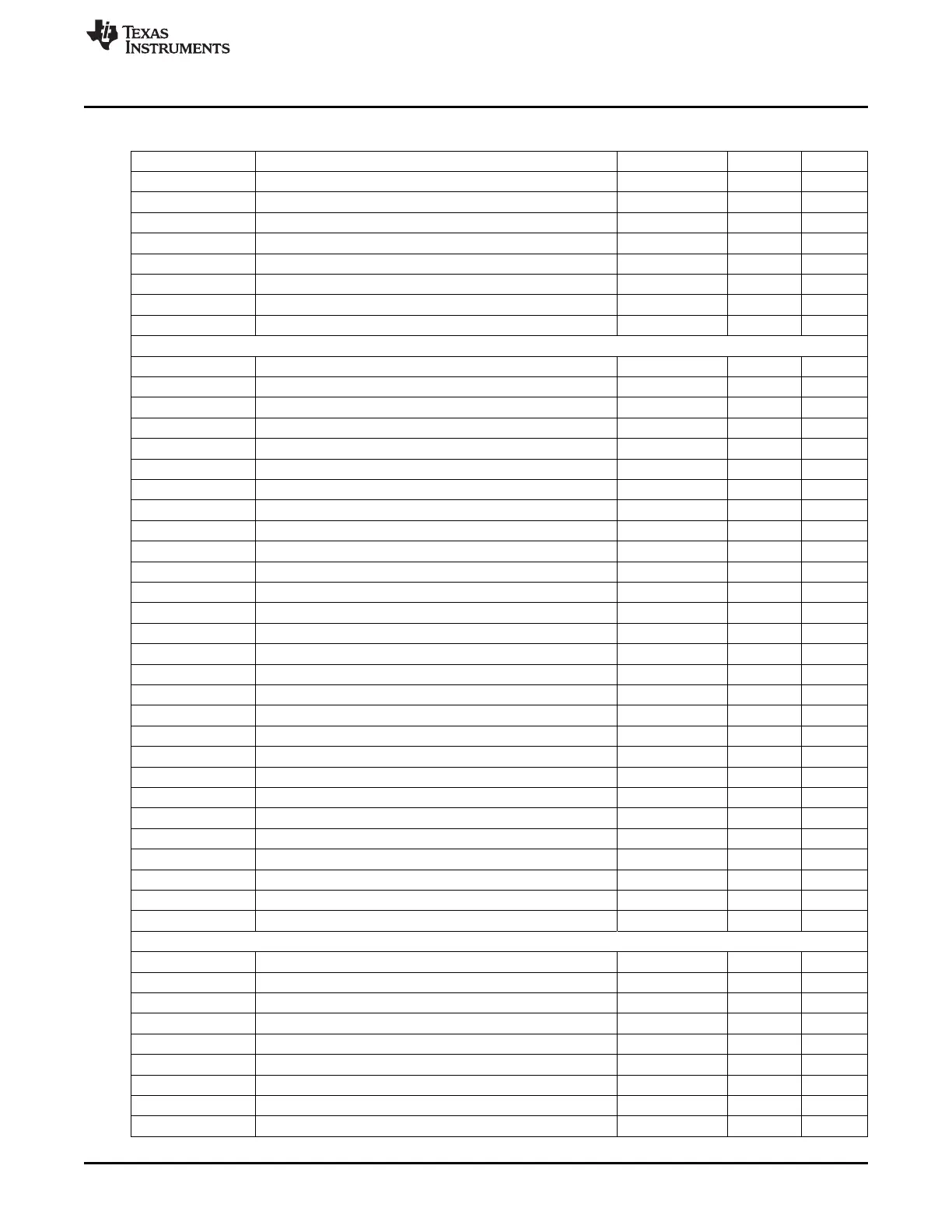

Table 2-3. Instruction Set Summary (continued)

Mnemonic Description Hex Opcode Bytes Cycles

XRL direct,#data Exclusive OR immediate data to direct byte 63 3 4

CLR A Clear accumulator E4 1 1

CPL A Complement accumulator F4 1 1

RL A Rotate accumulator left 23 1 1

RLC A Rotate accumulator left through carry 33 1 1

RR A Rotate accumulator right 03 1 1

RRC A Rotate accumulator right through carry 13 1 1

SWAP A Swap nibbles within the accumulator C4 1 1

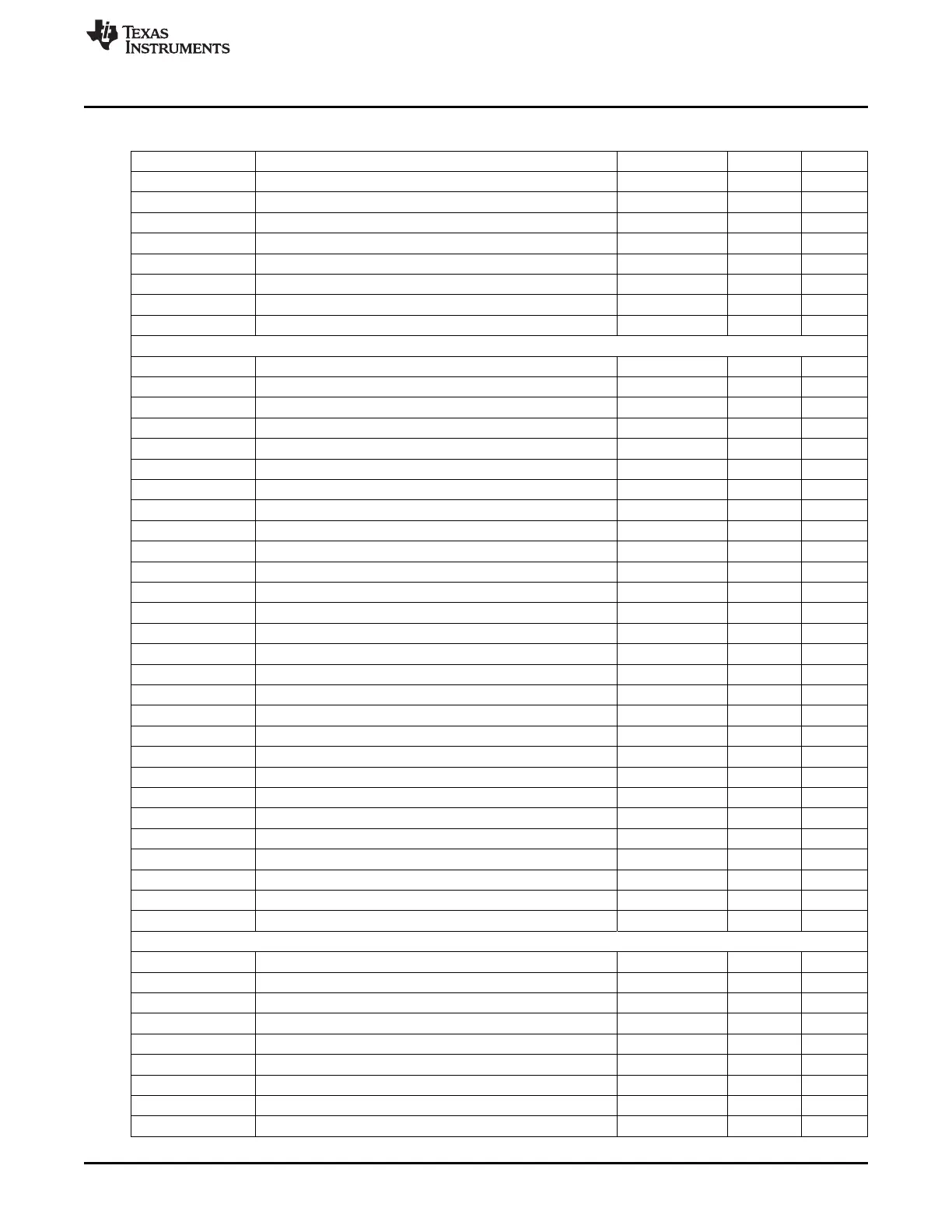

DATA TRANSFERS

MOV A,Rn Move register to accumulator E8–EF 1 1

MOV A,direct Move direct byte to accumulator E5 2 2

MOV A,@Ri Move indirect RAM to accumulator E6–E7 1 2

MOV A,#data Move immediate data to accumulator 74 2 2

MOV Rn,A Move accumulator to register F8–FF 1 2

MOV Rn,direct Move direct byte to register A8–AF 2 4

MOV Rn,#data Move immediate data to register 78–7F 2 2

MOV direct,A Move accumulator to direct byte F5 2 3

MOV direct,Rn Move register to direct byte 88–8F 2 3

MOV direct1,direct2 Move direct byte to direct byte 85 3 4

MOV direct,@Ri Move indirect RAM to direct byte 86–87 2 4

MOV direct,#data Move immediate data to direct byte 75 3 3

MOV @Ri,A Move accumulator to indirect RAM F6–F7 1 3

MOV @Ri,direct Move direct byte to indirect RAM A6–A7 2 5

MOV @Ri,#data Move immediate data to indirect RAM 76–77 2 3

MOV DPTR,#data16 Load data pointer with a 16-bit constant 90 3 3

MOVC A,@A+DPTR Move code byte relative to DPTR to accumulator 93 1 3

MOVC A,@A+PC Move code byte relative to PC to accumulator 83 1 3

MOVX A,@Ri Move external RAM (8-bit address) to A E2–E3 1 3

MOVX A,@DPTR Move external RAM (16-bit address) to A E0 1 3

MOVX @Ri,A Move A to external RAM (8-bit address) F2–F3 1 4

MOVX @DPTR,A Move A to external RAM (16-bit address) F0 1 4

PUSH direct Push direct byte onto stack C0 2 4

POP direct Pop direct byte from stack D0 2 3

XCH A,Rn Exchange register with accumulator C8–CF 1 2

XCH A,direct Exchange direct byte with accumulator C5 2 3

XCH A,@Ri Exchange indirect RAM with accumulator C6–C7 1 3

XCHD A,@Ri Exchange low-order nibble indirect. RAM with A D6–D7 1 3

PROGRAM BRANCHING

ACALL addr11 Absolute subroutine call xxx11 2 6

LCALL addr16 Long subroutine call 12 3 6

RET Return from subroutine 22 1 4

RETI Return from interrupt 32 1 4

AJMP addr11 Absolute jump xxx01 2 3

LJMP addr16 Long jump 02 3 4

SJMP rel Short jump (relative address) 80 2 3

JMP @A+DPTR Jump indirect relative to the DPTR 73 1 2

JZ rel Jump if accumulator is zero 60 2 3

41

SWRU191C–April 2009–Revised January 2012 8051 CPU

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...