Instruction Set Summary

www.ti.com

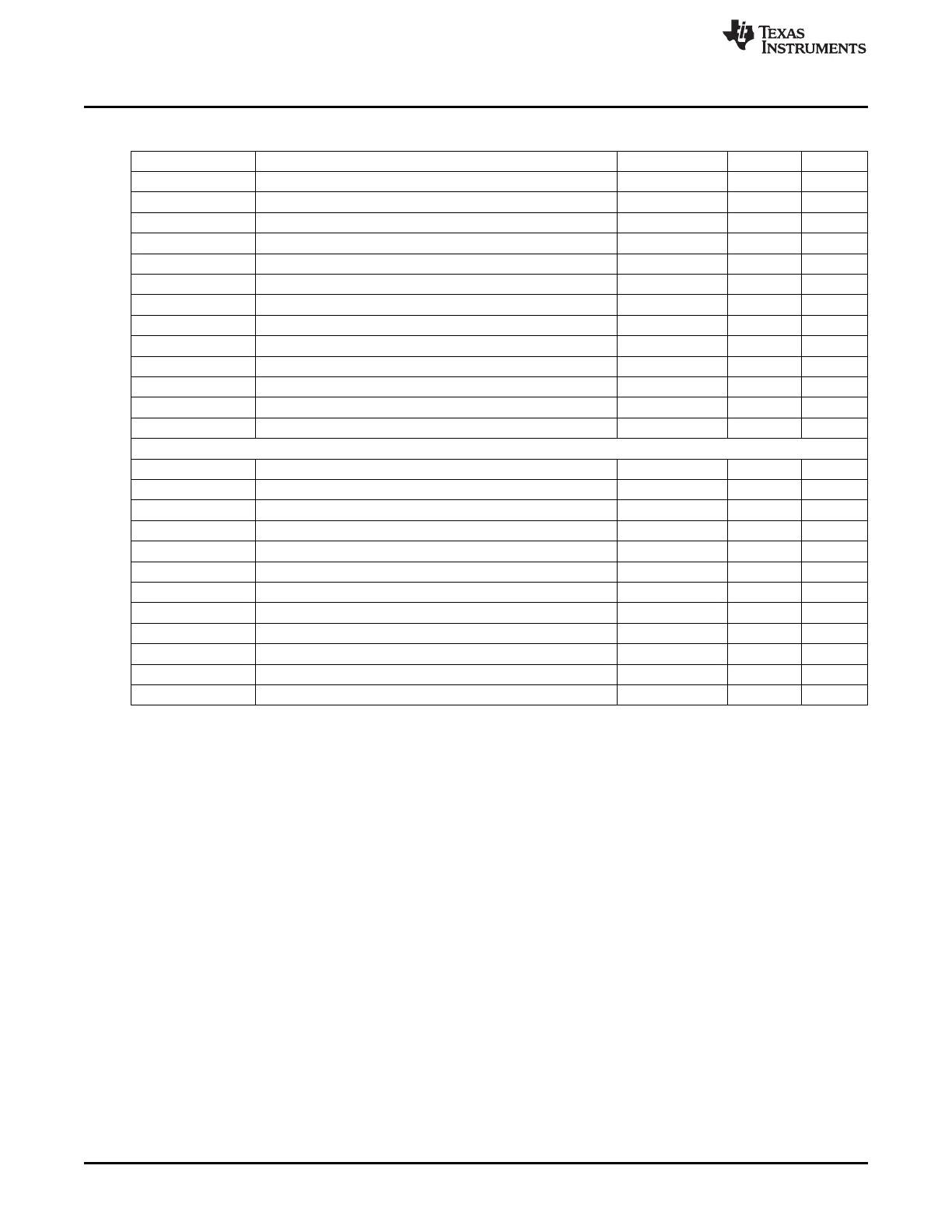

Table 2-3. Instruction Set Summary (continued)

Mnemonic Description Hex Opcode Bytes Cycles

JNZ rel Jump if accumulator is not zero 70 2 3

JC rel Jump if carry flag is set 40 2 3

JNC Jump if carry flag is not set 50 2 3

JB bit,rel Jump if direct bit is set 20 3 4

JNB bit,rel Jump if direct bit is not set 30 3 4

JBC bit,direct rel Jump if direct bit is set and clear bit 10 3 4

CJNE A,direct rel Compare direct byte to A and jump if not equal B5 3 4

CJNE A,#data rel Compare immediate to A and jump if not equal B4 3 4

CJNE Rn,#data rel Compare immediate to reg. and jump if not equal B8–BF 3 4

CJNE @Ri,#data rel Compare immediate to indirect and jump if not equal B6–B7 3 4

DJNZ Rn,rel Decrement register and jump if not zero D8–DF 1 3

DJNZ direct,rel Decrement direct byte and jump if not zero D5 3 4

NOP No operation 00 1 1

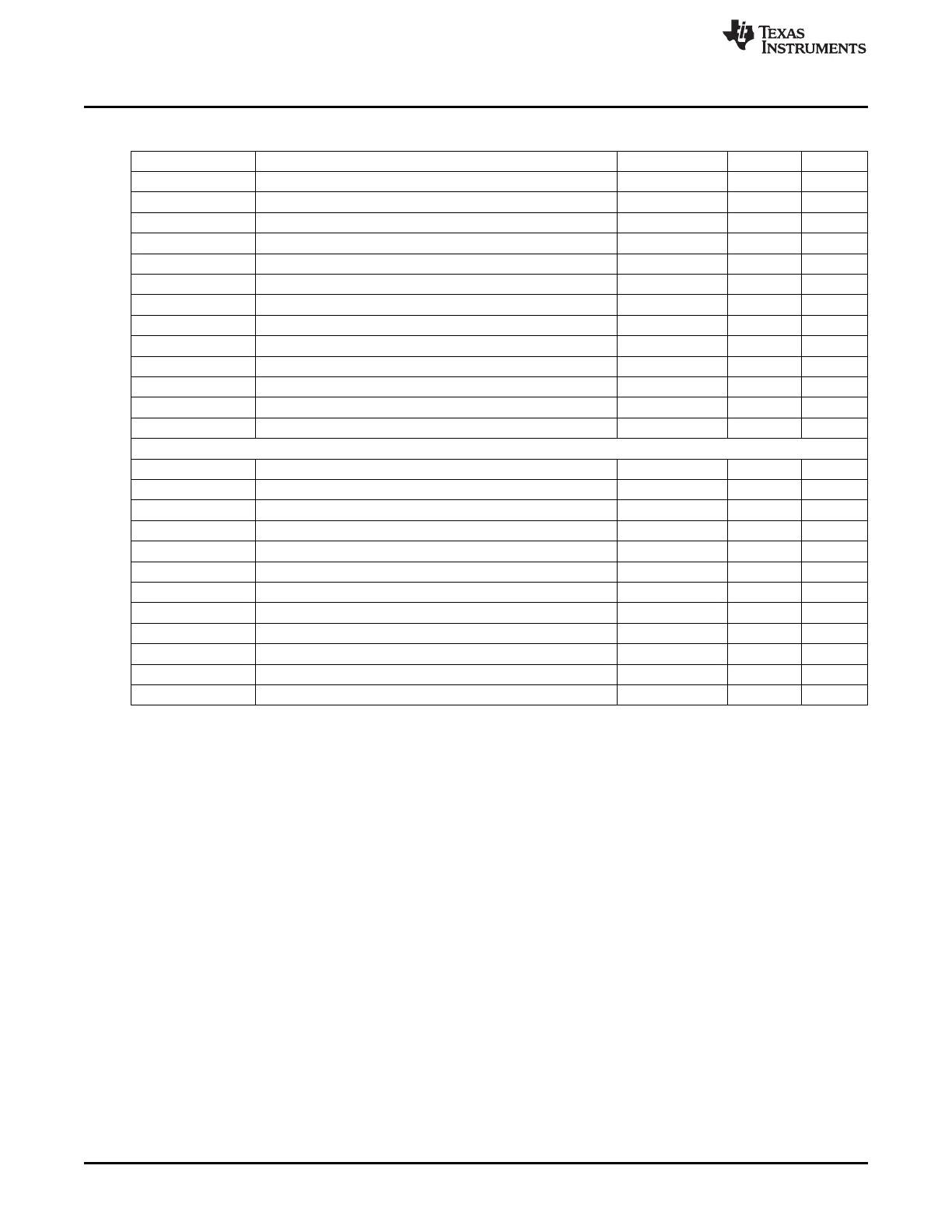

Boolean VARIABLE OPERATIONS

CLR C Clear carry flag C3 1 1

CLR bit Clear direct bit C2 2 3

SETB C Set carry flag D3 1 1

SETB bit Set direct bit D2 2 3

CPL C Complement carry flag B3 1 1

CPL bit Complement direct bit B2 2 3

ANL C,bit AND direct bit to carry flag 82 2 2

ANL C,/bit AND complement of direct bit to carry B0 2 2

ORL C,bit OR direct bit to carry flag 72 2 2

ORL C,/bit OR complement of direct bit to carry A0 2 2

MOV C,bit Move direct bit to carry flag A2 2 2

MOV bit,C Move carry flag to direct bit 92 2 3

42

8051 CPU SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...