Interrupts

www.ti.com

In the case when interrupt requests of the same priority level are received simultaneously, the polling

sequence shown in Table 2-8 is used to resolve the priority of each request. Note that the polling

sequence in Figure 2-4 is the algorithm found in Table 2-8, not that polling is among the IP bits as listed in

the figure.

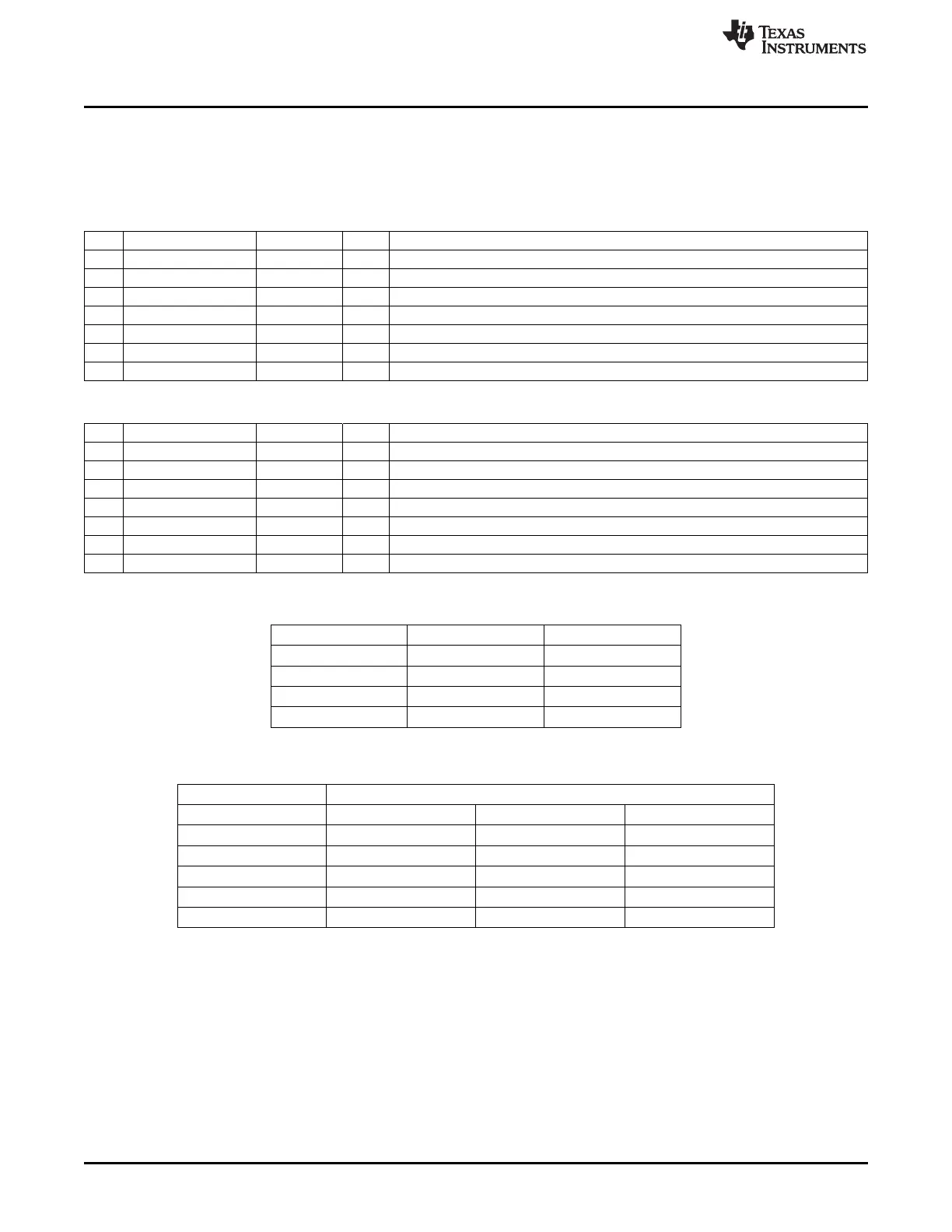

IP1 (0xB9) – Interrupt Priority 1

Bit Name Reset R/W Description

7:6 – 00 R/W Reserved

5

IP1_IPG5

0 R/W Interrupt group 5, priority control bit 1, see Table 2-7: Interrupt Priority Groups

4

IP1_IPG4

0 R/W Interrupt group 4, priority control bit 1, see Table 2-7: Interrupt Priority Groups

3

IP1_IPG3

0 R/W Interrupt group 3, priority control bit 1, see Table 2-7: Interrupt Priority Groups

2

IP1_IPG2

0 R/W Interrupt group 2, priority control bit 1, see Table 2-7: Interrupt Priority Groups

1

IP1_IPG1

0 R/W Interrupt group 1, priority control bit 1, see Table 2-7: Interrupt Priority Groups

0

IP1_IPG0

0 R/W Interrupt group 0, priority control bit 1, see Table 2-7: Interrupt Priority Groups

IP0 (0xA9) – Interrupt Priority 0

Bit Name Reset R/W Description

7:6 – 00 R/W Reserved

5

IP0_IPG5

0 R/W Interrupt group 5, priority control bit 0, see Table 2-7: Interrupt Priority Groups

4

IP0_IPG4

0 R/W Interrupt group 4, priority control bit 0, see Table 2-7: Interrupt Priority Groups

3

IP0_IPG3

0 R/W Interrupt group 3, priority control bit 0, see Table 2-7: Interrupt Priority Groups

2

IP0_IPG2

0 R/W Interrupt group 2, priority control bit 0, see Table 2-7: Interrupt Priority Groups

1

IP0_IPG1

0 R/W Interrupt group 1, priority control bit 0, see Table 2-7: Interrupt Priority Groups

0

IP0_IPG0

0 R/W Interrupt group 0, priority control bit 0, see Table 2-7: Interrupt Priority Groups

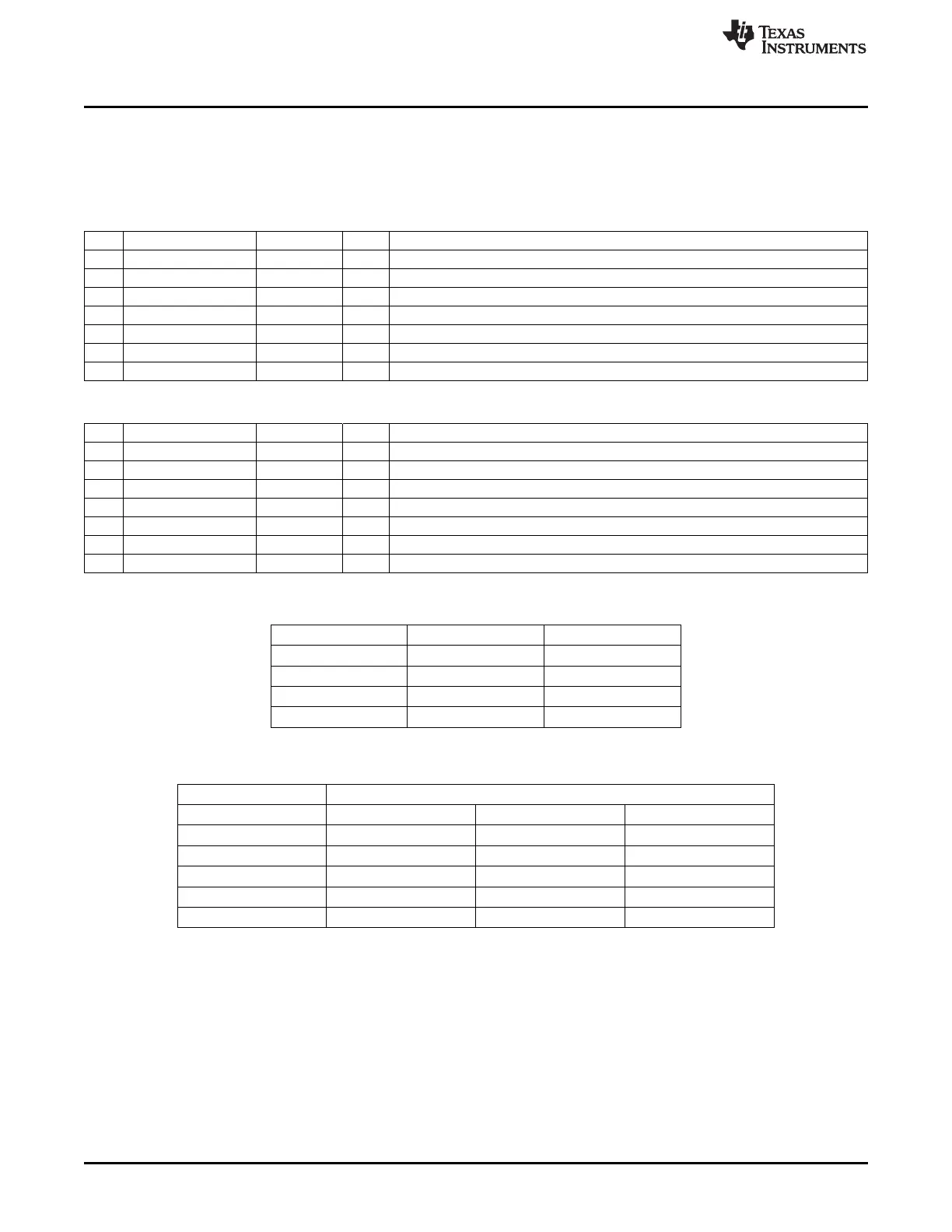

Table 2-6. Priority Level Setting

IP1_x IP0_x Priority Level

0 0 0 – lowest

0 1 1

1 0 2

1 1 3 – highest

Table 2-7. Interrupt Priority Groups

Group Interrupts

IPG0 RFERR RF DMA

IPG1 ADC T1 P2INT

IPG2 URX0 T2 UTX0

IPG3 URX1 T3 UTX1

IPG4 ENC T4 P1INT

IPG5 ST P0INT WDT

50

8051 CPU SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...